#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건

을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

Disclaimer

# 공 학 박 사 학 위 논 문

박막형 고주파 소자를 위한 저가형 3차원 웨이퍼 레벨 패키징의 설계와 제작

임 재 환

### 공 학 박 사 학 위 논 문

# 박막형 고주파 소자를 위한 저가형 3차원 웨이퍼 레벨 패키징의 설계와 제작

지도교수 류 지 열

이 논문을 공학박사 학위논문으로 제출함.

2014년 8월

부 경 대 학 교 대 학 원

정보통신공학과

임 재 환

# 임재환의 공학박사 학위논문을 인준함.

# 2014년 8월 25일

| CANATIONAL UN |   |      |           |  |  |  |

|---------------|---|------|-----------|--|--|--|

| 6             | 7 |      | m         |  |  |  |

| 주             | 심 | 공학박사 | 노 석 호 (인) |  |  |  |

| 위             | 원 | 공학박사 | 박 규 칠 (인) |  |  |  |

| 위             | 원 | 공학박사 | 이 용 욱 (인) |  |  |  |

| 위             | 원 | 공학박사 | 최 우 창 (인) |  |  |  |

| 위             | 원 | 공학박사 | 류 지 열 (인) |  |  |  |

## 목 차

| 제1장 서론                         |

|--------------------------------|

| 제2장 웨이퍼 레벨 패키징6                |

| 2.1. 패키징의 종류 6                 |

| 2.2. 고주파 MEMS패키징의 분류 및 연구현황 8  |

| 2.3. 동평면 도파관 해석 11             |

| 2.4. 동평면 도파관 설계 13             |

| 제3장 제안된 웨이퍼 레벨 패키징             |

| 3.1. 웨이퍼 레벨 패키지 설계 17          |

| 3.2. 웨이퍼 본딩 기술 및 재료 선정 23      |

| 3.3. Au와 Sn의 조성비에 따른 기초실험 31   |

| 3.4. 웨이퍼 레벨 패키지 공정설계 39        |

| 3.5. 패키지 웨이퍼의 제조공정 44          |

| 3.6. 동평면 도파관 웨이퍼의 제조공정 및 결과 49 |

| 3.7. 웨이퍼 레벨 본딩공정 및 후공정 53      |

| 제4장 동평면도파관 웨이퍼 레벨 패키징65        |

| 4.1. 동평면도파관 시뮬레이션 결과65         |

| 4.2. 동평면도파관 웨이퍼 레벨 패키징 공정 70   |

| 4.3. 실험 및 고찰 71                |

| 제5장 결론 79                      |

| 참고문헌 81                        |

# 그림 목차

| [그림 | 1.1.] | 아이폰에서 초박형 MEMS 소자의 사용 예       | 2  |

|-----|-------|-------------------------------|----|

| [그림 | 1.2.] | 일반적인 패키징과 WLP의 비교             | 3  |

| [그림 | 2.1.] | 단계별 패키징의 종류                   | 7  |

| [그림 | 2.2.] | 고주파 MEMS 패키징의 종류              | 9  |

| [그림 | 2.3.] | 동평면 도파관                       | 14 |

| [그림 | 2.4.] | 동평면 도파관 시뮬레이션 결과              | 16 |

| [그림 | 3.1.] | 애질런트사의 FBAR 소자용 WLP 구조        | 17 |

| [그림 | 3.2.] | DRIE 및 도금 공정 기반의 WLP 구조       | 18 |

|     |       | 제안된 WLP 단면도                   |    |

|     |       | 제안된 WLP 평면도                   | 21 |

| [그림 | 3.5.] |                               | 22 |

| [그림 | 3.6.] | Au/Sn 상태도 ·····               | 26 |

| [그림 | 3.7.] |                               | 32 |

| [그림 |       | 광학 현미경으로 관찰한 HS 솔더의 표면 상태     | 34 |

| [그림 | 3.9.] | 광학 현미경으로 관찰한 HA 솔더의 표면 상태     | 34 |

| [그림 | 3.10. | ] 광학 현미경으로 관찰한 E 솔더의 표면 상태    | 35 |

| [그림 | 3.11. | ] 광학 현미경으로 관찰한 Ht 솔더의 표면 상태 … | 35 |

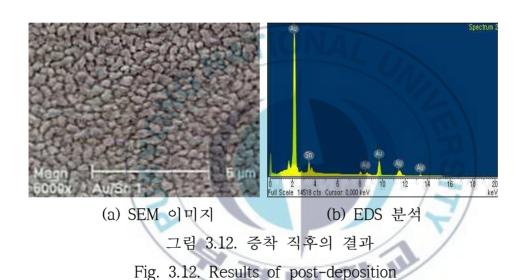

| [그림 | 3.12. | ] 증착 직후의 결과                   | 36 |

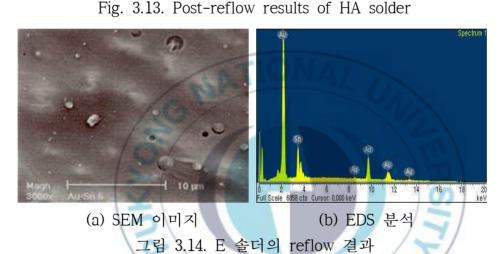

| [그림 | 3.13. | ] HA 솔더의 reflow 결과            | 37 |

| [그림 | 3.14. | ] E 솔더의 reflow 결과             | 37 |

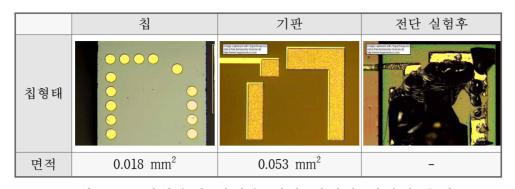

| [그림 | 3.15. | ] 전단응력 실험을 위한 일정한 형태의 솔더      | 38 |

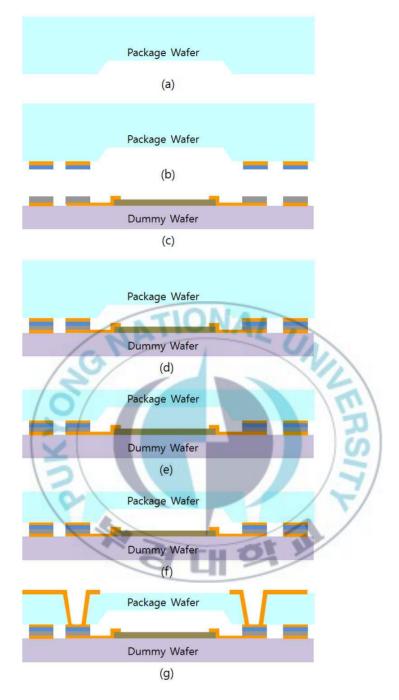

| [그림 | 3.16. | ] 제안된 WLP 공정도                 | 43 |

| [그림 | 3.17.]  | 실리콘 질화막 제거 전 후의 공동             | 44   |

|-----|---------|--------------------------------|------|

| [그림 | 3.18.]  | 금속패턴 형성을 위한 리프트-오프 패턴          | 45   |

| [그림 | 3.19.]  | 리프트-오프 패턴 상의 UBM 증착            | 46   |

| [그림 | 3.20.]  | 리프트-오프 후의 UBM 패턴               | 47   |

| [그림 | 3.21.]  | Ni/Au 층을 추가한 금속패턴              | 48   |

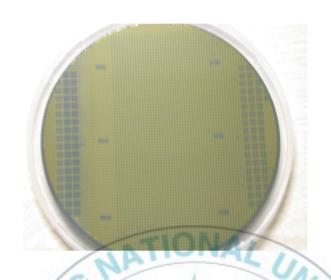

| [그림 | 3.22.]  | 완성된 패키지 웨이퍼                    | 48   |

| [그림 | 3.23.]  | Au/Sn 합금 솔더층이 형성된 기판 웨이퍼의      |      |

|     |         | 공정별 단계                         | ··50 |

| [그림 | 3.24.]  | 기판 웨이퍼의 배면에 형성된 웨이퍼 본딩용        |      |

|     |         | 정렬 패턴                          | 51   |

| [그림 | 3.25.]  | 완성된 기판 웨이퍼의 사진                 | 52   |

| [그림 | 3.26.]  | 웨이퍼 본딩 시 misalignment          | 55   |

| [그림 | 3.27.]  | 본딩된 웨이퍼 뒷면에서 관찰되는 크랙           | 56   |

| [그림 | 3.28.]  | 국부적으로 본딩되지 않은 영역의 decap 사진 …   | 57   |

| [그림 | 3.29.]  | Au 및 Sn을 이용하여 본딩한 접합부의 단면      | 58   |

| [그림 | 3.30.]  | Au/Sn 합금솔더를 이용하여 본딩한 접합부의 단면 … | 60   |

| [그림 | 3.31.]  | 무전해 도금된 Au와 진공 증착된 Sn을 이용하여    |      |

|     |         | 본딩한 접합부의 단면                    |      |

| [그림 | 3.32.]  | 패키지 웨이퍼 후면에 형성한 비아 홀           | 63   |

| [그림 | 3.33.]  | 패키지 웨이퍼의 비아 홀 상에 형성된 금속패턴 …    | 64   |

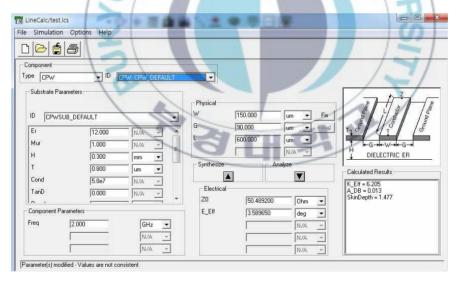

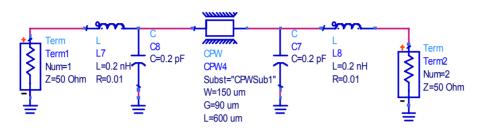

| [그림 | 4.1.] ( | CPW 패턴 계산기                     | 65   |

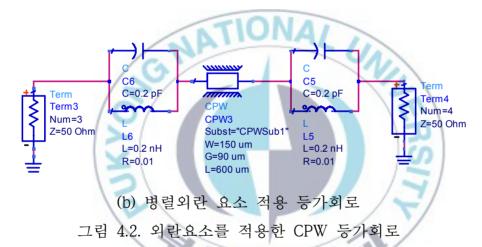

| [그림 | 4.2.]   | 외란요소를 적용한 CPW 등가회로             | 66   |

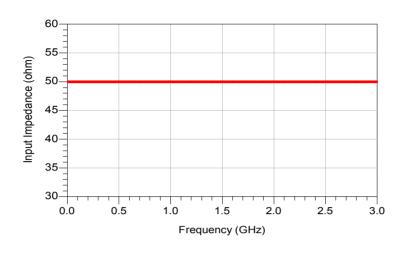

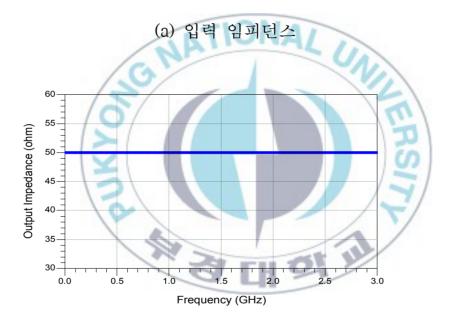

| [그림 | 4.3.]   | 설계된 CPW의 입력 및 출력 임피던스          | 67   |

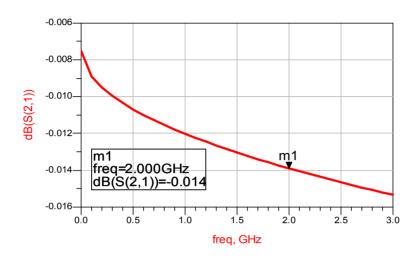

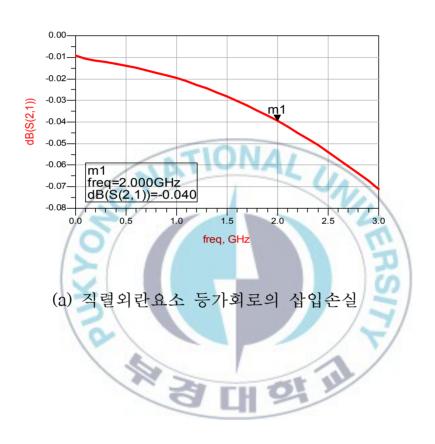

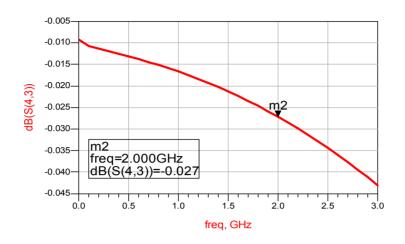

| [그림 | 4.4.] 2 | CGHz 대역에서의 삽입손실 시뮬레이션 결과       | 69   |

| [그림 | 4.5.]   | 완성된 CPW 웨이퍼 레벨 패키징             | 70   |

| [그림 | 4.6.1   | 세작된 WLP의 전단응력 측정 결과            | 71   |

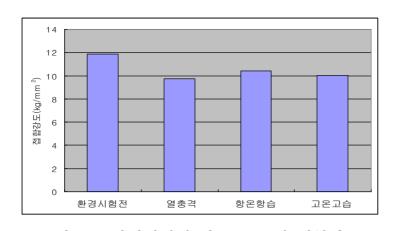

| [그림 | 4.7.] | 환경시험에   | 따른 WLP | 의 접합강도 | <u> </u> |       | ···· 73  |

|-----|-------|---------|--------|--------|----------|-------|----------|

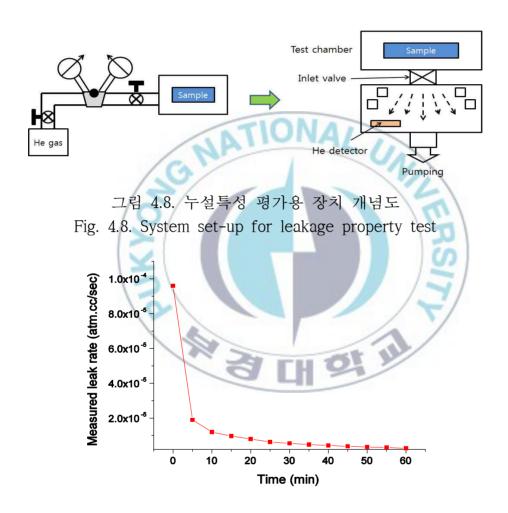

| [그림 | 4.8.] | 누설특성 평  | 형가용 장치 | 개념도    | •••••    |       | ····· 74 |

| [그림 | 4.9.] | 4조각의 4인 | ]치 웨이퍼 | 에서 측정된 | 헬륨       | 누설량 · | ····· 74 |

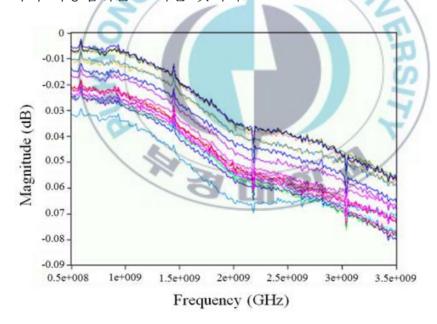

| [그림 | 4.10. | ] 주파수에  | 따른 WLP | 칩의 삽입선 | 는실 "     |       | ···· 75  |

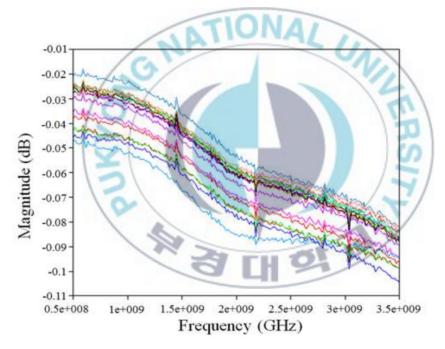

| [그림 | 4.11. | ] 환경시험  | 후 주파수에 | 따른 WLP | 칩의       | 삽입손실  | 77       |

# 표 목 차

| [班 3.1. | ] 웨이퍼 본딩 기술의 종류 및 특징 23              |

|---------|--------------------------------------|

| [班 3.2. | ] 솔더 재료들의 특성 26                      |

| [班 3.3. | ] 플립칩 본딩을 위한 다양한 무연솔더 27~28          |

| [班 3.4. | ] 증착성분 33                            |

| [班 3.5. | ] 패턴 형태에 따른 전단응력 38                  |

| [표 3.6. | ] 웨이퍼 본딩을 위한 Au/Sn 솔더의 구조 및 본딩 결과 54 |

| [       | ] 2GHz에서 측정된 WLP 칩의 삽입손실 76          |

## Design and Fabrication of a Low-Cost 3-Dimensional Wafer Level Packaging for Thin Film Type RF Devices

#### Jae Hwan Lim

### Department of Information and Communications Engineering, The Graduate School Pukyong National University

#### **Abstract**

This thesis presents the design and fabrication of simple and low-cost wafer level packaging(WLP) for thin film radio frequency(RF) devices. The WLP with a small size of  $1.04 \times 1.04 \times 0.4mm^3$  was fabricated by low-cost micromachining process.

The package wafer of key function in the WLP consisting of junction with the package wafer and device wafer contains cavity for securing a space of the located device, electrical feed-through for electrical connection, solder for bonding with device wafer, etc.

Without high-cost silicon deep reactive etching(DRIE) and plating process for electrical through-interconnection, the proposed technique utilizes typical silicon anisotropic etching and metal deposition method. As the solder material for bonding and hermetic sealing, we used gold (Au)/tin(Sn) alloy. The fabricated

WLP with a bonding size of  $0.315mm^2$  showed an excellent average shear strength of  $10.425kg/mm^2$  and a low leak rate of less than  $1.2\times10^{-5}atm.cc/\mathrm{sec}$ . It also showed a very low insertion loss of -0.0048dB at the operation frequency of 2GHz.

The proposed WLP structure is simple and cost-effective, so we expect that the proposed WLP is one of good candidates for packages of thin-film-type RF devices.

### 제1장 서론

최근 들어 스마트폰 등을 비롯하여 이동성을 증가시킨 휴대형 무선기기에 대한 시장 규모가 급격히 팽창함에 따라 고주파 대역에 적용이 가능한 무선통신시스템의 개별소자에 대한 많은 연구가 진행되고 있다[1~5]. 고주파 송수신 시스템의 핵심부품이라할 수 있는 스위치, 트랜지스터, 공진기, 필터 등 외부의 회로로서별도로 연결되는 수동 및 능동소자의 경우 제작단가가 높고, 소자의 크기가 크며, 전력손실 등의 문제로 휴대기기의 적용에 문제점이 되기도 한다. 따라서 원활한 무선통신환경에서 휴대성과이동성을 증가시키기 위해 사용되는 부품의 경박단소화에 따른 복합화와 소형화가 끊임없이 요구되고 있다. 이를 위해 기존의고주파 설계 기술과 MEMS(Micro-Electro-Mechanical System)기술이 융합된 RF MEMS 기술이 주목받고 있다[1].

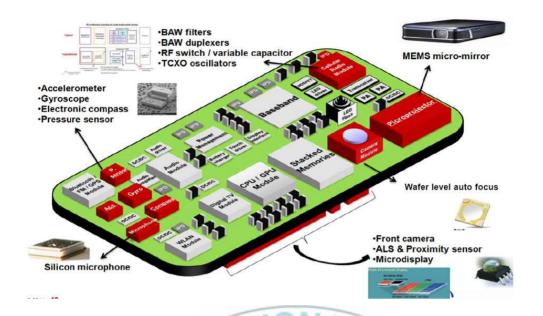

그림 1.1은 스마트폰에서 초박형 MEMS 소자가 이용되는 예를 보여주고 있다. 실리콘 기판 상에 박막의 형태로 제조되는 초소형의 고주파 수동소자들은 실리콘 웨이퍼를 재료로 초박형 패키징이 가능하다는 장점이 있다.

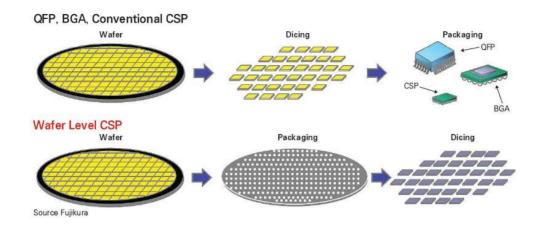

그림 1.2는 일반적인 패키징과 웨이퍼 레벨 패키징(Wafer Level Packaging, WLP)을 비교한 것이다. 기존의 패키징은 크게 3가지과정, 즉 웨이퍼에서 개별 칩으로 절단하여 세정을 거친 다음에 분리된 칩을 리드프레임 혹은 세라믹 등의 기판에 본딩하는 과정, 소자에 와이어 본딩하는 과정, 그리고 금속 케이스 혹은 에폭시 등으로 몰딩하는 과정으로 이루어진다.

그림 1.1. 아이폰에서 초박형 MEMS 소자의 사용 예 Fig. 1.1. Example of ultra thin film MEMS devices for i-phone

이러한 공정은 작업 공수가 많을 뿐 아니라 수율이 좋지 못하여 단가를 줄이는데 한계를 가지고 있고, 특히 여러 가지 부품을 집적시키고자 할 경우에 부피가 지나치게 커지는 단점을 가지고 있다. 현재 박막형 고주파 소자의 패키징은 WLP 방식으로 제작되고 있는데, WLP는 소자 웨이퍼를 절단하지 않고 웨이퍼단계에서 패키징 작업까지 완성한 다음에 칩을 분리하는 방식이므로 공정이 간단하고, 패키징 되지 않은 소자를 절단하고 세정하는 과정에서 발생하는 손실을 줄일 수 있다. 또한 WLP 기술은 능동 및 수동 부품의 통합화 추세에 효과적으로 대응할 수 있는 기술로, 칩 단위 패키징에 비해 생산성이 향상되어 가격절감 효과가 크며, 소형화가 용이하다[2].

그림 1.2. 일반적인 패키징과 WLP의 비교 Fig. 1.2. Comparison of general package and WLP

박막형 고주파 소자들은 음향주파수로 진동하는 진동체를 가지고 있고 진동체의 질량이 매우 작기 때문에 미세한 먼지나수분, 산소, 탄소 등과 같은 가벼운 원자의 부착에 의해서도 진동주파수가 달라질 수 있다. 그러므로 이러한 소자들은 매우 엄격한 밀봉을 필요로 하는데, WLP 기술에 있어서 완전한 밀봉을할 수 있는 방법으로는 금속을 이용한 솔더본딩이 적합하다[3].

휴대형 무선기기에 사용되는 부품의 경박단소화 추세에 따라서 웨이퍼의 두께도 점차 얇아지고 있다. 현재 휴대형 무선기기에서 요구되는 박막형 고주파 칩의 두께는 0.4mm 이하로 소자 웨이퍼와 패키지 웨이퍼가 같은 두께를 가진다고 가정하면 패키지 웨이퍼의 두께는 약 0.2mm가 되어야 한다. 이러한 얇은 웨이퍼는 그 만큼 취급이 까다롭고 제조과정에서 파손에 의한 손실이 증가하게 된다[4~6].

WLP에서 패키지 웨이퍼는 소자를 외부 환경으로부터 보호하는

기능과 함께 소자의 입출력 단자를 외부와 연결하는 기능을 동시에 수행하여야 한다. 외부 환경과 완전히 단절된 소자로부터 입출력 단자를 외부와 연결시키기 위해서는 관통전극(electrical through-interconnection)이 필요하다. 관통전극은 웨이퍼를 관통하는 구멍을 형성하고 이에 양질의 전기전도체이면서 동시에 공기 및 액체의 소통을 차단할 수 있는 금속 등으로 채워서 제작한다. 일반적으로 패키지 웨이퍼를 제작하는 방법으로는 소자웨이퍼에 실리콘 DRIE(Deep Reactive Ion Etching) 방법으로 관통홀을 형성한 후, 전도성 재료로 홀을 도금함으로써 관통전극을 형성한다. 그러나 이 방법은 생산성이 떨어지고, 패키지 비용이상승하는 단점이 있다[7~8].

본 논문에서는 앞서 언급한 단점을 보완한 박막형 고주파소자를 위한 소형·박형의 WLP의 설계, 제작 및 WLP를 위한간단하고 저가인 3차원 실리콘 가공기술을 제안한다. 패키지웨이퍼를 제작하기 위하여 기존에 이용되던 실리콘 DRIE와 도금등의 값비싼 공정을 배제하고, 이방성 습식식각, 금속증착 등저가의 일반적인 마이크로머시닝 공정기술을 사용하였다. 패키지의 밀봉특성을 평가하기 위하여 실제 박막형 고주파 소자대신에 동평면도파관(Coplanar Wave Guide, CPW)을 형성한 더미소자를 제작하였다. 또한, 금(Au)과 주석(Sn)의 합금을 이용하여제작된 패키지 웨이퍼와 더미 웨이퍼를 본당하여 WLP를완성하였다. 완성된 WLP를 절단하여 개별 칩으로 분리한 후 칩의전단응력(shear strength) 및 누설률(leak rate)을 평가하였다.

제2장에서는 WLP개요, CPW 신호전송선 설계에 대해 기술한다. 제3장에서는 본 연구에서 제안하는 WLP에 대해 설명하고, 각종 제조 공정, 본딩 공정 및 후공정에 대하여 언급한다. 또한

제4장에서는 동평면 도파관 WLP에 대한 시뮬레이션과 실험결과를 분석하고, 마지막 제5장에서는 결론을 간략히 기술한다.

### 제2장 웨이퍼 레벨 패키징

#### 2.1. 패키징의 종류

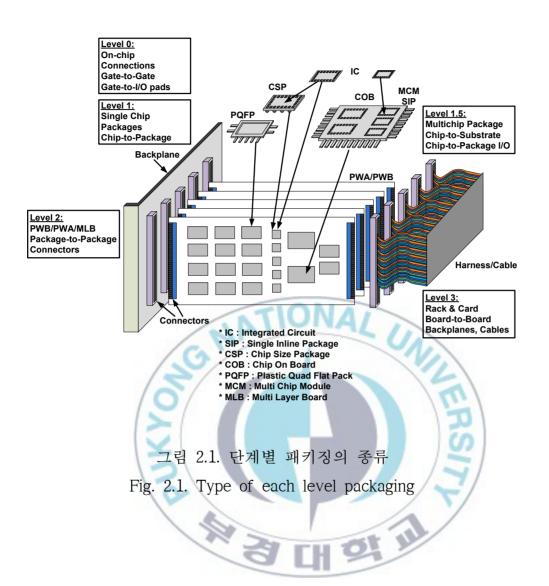

일반적으로 집적회로(Integrated Circuits, IC)는 패키징 방법을 통해 4단계로 구분되어질 수 있다. 그림 2.1은 패키징의 각 단계별 기본개념을 나타낸다[4]. 0-레벨 패키징은 웨이퍼 상에서 여러 소자나 칩 간의 전기적 연결을 구성하여, 패키징한 후에 개별 소자로 분리하는 것으로 WLP이라고 한다. 1<sup>st</sup> 레벨 패키징은 단일 패키징 구조의 내부에 여러 개의 칩을 연결하는 칩 규모 패키징 (Chip Scale Packaging, CSP)을 기반으로 하고 있으며, C&W(chip and wire) 본딩, Flip Chip(FC) 본딩 등을 통해 전기적 연결이 이루어진다. 2<sup>nd</sup> 레벨 패키징은 패키징되어 있는 칩 간의 전기적 연결을 이루는 것으로, Printed Circuit Board(PCB) 또는 PWA(Printed Wire Assembly)라 불리는 하나의 컴포넌트를 이루는 말한다. 마지막으로 마더보드(Mother Board) 것을 또는 PWB(Printed Wiring Board)를 통해 개별 컴포넌트 간의 전기적 연결을 하는 것으로 이를 3<sup>rd</sup> 레벨 패키징이라고 한다[9].

CSP는 웨이퍼 상에 완성된 개별 소자를 다이싱한 후에 패키징 구조의 내부에서 전기적 연결을 이루는 것에 비해 웨이퍼 단위 패키징은 소자들 간의 전기적 연결이나 외부의 환경으로부터 소자를 보호하는 구조를 웨이퍼 상에서 일괄적으로 구현할 수 있어서 대량 생산에 적합하고 전체 칩의 제작비용에서 50% 가량을 차지하는 패키징 관련 비용을 크게 절감할 수 있다[9 ~ 10].

### 2.2. 고주파 MEMS 패키징의 분류 및 연구현황

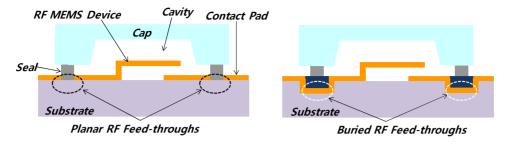

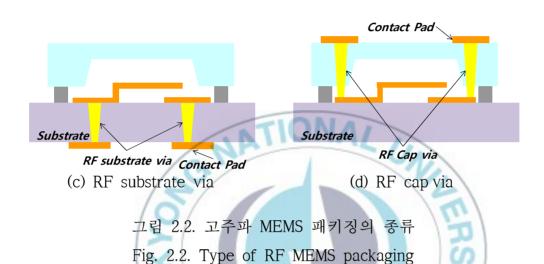

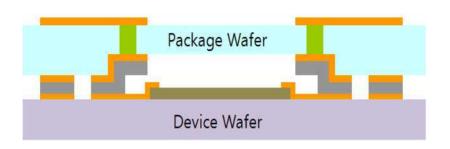

그림 2.2는 일반적인 고주파 MEMS 패키징의 4가지 종류를 나타낸 것이다. 고주파 MEMS 소자의 패키징을 위해서는 고주파 신호의 인가를 위한 접촉패드와 신호 전송시 최소 손실을 위한 임피던스 정합이 고려된 신호 전송선이 필수적으로 확보되어야한다. 또한, 고주파 MEMS 소자의 3차원적인 구동을 위한 공동(Cavity)부 및 소자보호를 위해 둘러싸여진 cap이 필요하다.

그림 2.2(a)의 horizontal planar RF feed through 방식이나 그림 2.2(b)의 horizontal buried RF feed through 방식의 경우 기판 위에 contact pad, 신호 전송선 및 MEMS 소자를 표면 마이크로 머시닝(Surface micromachining)을 통해 동시에 구성할 수 있기때문에 공정의 간소화 및 높은 수율을 확보할 수 있다는 장점이 있다. 그러나 소자별로 cap을 씌워야하기 때문에 WLP이 어렵고 cap과 기판간의 접합에서 전기적 절연을 해줄 수 있는 SU-8, PerMX, BCB(benzocyclobutene)와 같은 폴리머를 이용하여야 하는데이로 인해 외부의 치명적인 환경으로부터 MEMS 소자를 보호할 수 있는 완전실장(hermetic sealing)을 구현하기 어렵다는 단점도가지고 있다[9~10].

(a) Horizontal planar RF feed through (b) Horizontal buried RF feed through

이와 달리 그림 2.2(c)의 RF substrate via 방식과 그림 2.2(d)의 RF cap via 방식의 경우에는 기판 관통 연결구조(through wafer interconnection)를 이용하여 신호 전송선과 contact pad를 연결하기 때문에 완전실장이 가능한 양극접합(anodic bonding)이나 유택틱 접합(eutectic bonding)을 이용하여 WLP이 가능하다. 또한 수직으로 contact pad와 신호 전송선을 연결하기 때문에 horizontal plannar 방식에 비해 패키징 구조가 차지하는 면적(footprint)도 줄일 수 있다[9~11].

본 연구에서는 공정비용이 고가인 DRIE(Deep Reactive Ion Etching)등을 이용한 건식에칭방법을 이용하지 않고, 전통적으로 저비용, 고수율인 이방성 습식식각(anisotropy wet etching)방법을 통해 cap웨이퍼의 상하부를 관통하여 전극을 연결하는 방식을 제안하고자 한다.

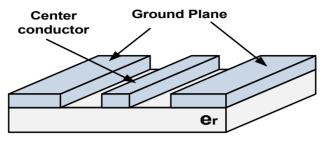

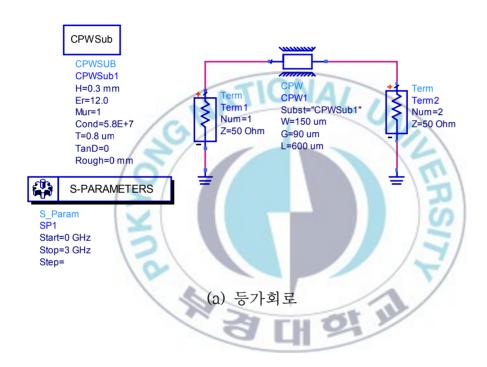

#### 2.3. 동평면 도파관 해석

동평면 도파관(Coplanar waveguide, CPW)의 구조는 기판두께 h, 신호선의 폭 W, 신호선과 접지면과의 거리 S 및 비유전율  $\mathcal{E}_r$  을 이용하여 특성 임피던스  $Z_0$ 의 신호전송선을 구현할 수 있으며, 커패시터, 인덕터 등의 고주파 소자를 구성할 수 있다.

특성임피던스  $Z_0$  및 관련 수식은 식(2.2) ~ (2.5)와 같다.

$$Z_O = \frac{30\pi}{\sqrt{\varepsilon_0 \varepsilon_{eff}}} \frac{K(k')}{K(k)}$$

(2.1)

$$\frac{K(k)}{K'(k)} = \frac{1}{\pi} \ln\left[2\frac{(1+\sqrt{k})}{(1-\sqrt{k})}\right] \qquad \text{for } 0 \le k \le 0.707$$

(2.2)

$$\frac{K'(k)}{K(k)} = \frac{1}{\pi} \ln\left[2\frac{(1+\sqrt{k})}{(1-\sqrt{k})}\right] \qquad \text{for } 0.707 \le k \le 1$$

$$K'(k) = K(k'), \qquad k' = \sqrt{1-k^2}$$

$$k = \frac{a}{b}, \qquad a = \frac{S}{2}, \qquad b = \frac{S}{2} + W$$

(2.3)

$$K'(k) = K(k'), k' = \sqrt{1 - k^2}$$

(2.4)

$$k = \frac{a}{b}, \qquad a = \frac{S}{2}, \qquad b = \frac{S}{2} + W$$

(2.5)

유효유전율은 식(2.6) ~ (2.7)과 같다.

$$e_{eff} = 1 + \frac{\varepsilon_r - 1}{2} \frac{K(k')K(k_1)}{K(k)K(k'_1)}$$

(2.6)

$$k_1 = \frac{\sinh(\frac{\pi a}{2h})}{\sinh(\frac{\pi b}{2h})} \tag{2.7}$$

CPW 구조에서 특성 임피던스를 갖는 신호전송선을 설계할 때 우선적으로 고려해야 할 것은 주파수에 따른 유전체기판의 두께이다. 신호전력에서 누설이 발생하면 신호의 감쇄를 증가시키고 회로의 이웃한 부분과 누화(crosstalk)를 발생시키게 된다. 전력누설은 surface mode의 차단 주파수를 동작 주파수 이상으로 끌어올리는 얇은 유전체 기판을 사용하면 방지할 수 있는데, 이때 유전체기판의 두께 h는 식 (2.8)과 같이 결정된다. 또한, 유전체의 두께 h가 접지면 간 거리인 b보다 클 경우에는 특성임피던스  $Z_0$ 는 유전체의 두께에 대해 독립적으로 작용한다.

$$h < \frac{0.12\lambda_0}{\sqrt{\varepsilon_r}} \tag{2.8}$$

제작 시 접지면의 면적은 제한될 수 없으며, 그 크기는 c > 5b가 되어야 한다. 따라서 중심도체 양면의 접지면을 주기적으로 와이어 본딩(wire bonding)하면 주파수가 변화하는 경향을 감소 시킬 수 있다. 또한 higher mode에서의 확산을 막기 위해 접지면과 접지면 사이의 거리 b는 식(2.9)를 만족하여야 한다.

$$b < \frac{\lambda}{2} \tag{2.9}$$

#### 2.4. 동평면 도파관 설계

본 논문에서 제안하는 WLP 구조에서는 MEMS 소자를 실장하여 패키징하지 않고 50 ohm의 특성 임피던스를 갖는 CPW를 이용하여 패키징 구조의 성능을 평가하고자 한다. CPW는 기판의 윗면에 신호 전송선(signal line)이 있고 아랫면에는 접지선(ground line)이 있는 마이크로스트립과는 달리 신호 전송선과 좌우의 접지선이 기판의 한 면에 있는 구조로 되어 있어서 비아를 통한 연결이용이하고, 신호 전송선과 접지선 간 수직 전자장이 형성되기때문에 TEM(Transverse Electro-Magnetic)모드를 구현할 수 있어마이크로스트립보다 고주파 전송특성이 우수하다.

그림 2.3과 같은 CPW에 대하여 식 (2.1) ~ (2.5)가 적용된다. 즉, CPW의 특성 임피던스(characteristic impedance) 값은 신호연결선의 넓이와 좌우에 있는 두 접지선의 간격에 의해 결정되어진다[7-8].

CPW는 TEM 모드를 이용하는 전송선로로 마이크로스트립선로와 유사하지만 접지면이 바닥에 있는 것이 아니라 신호선의 좌우에 위치한 형태로 동일면에 있기 때문에 관통 홀을 구현하기 쉬워서 단락 stub류와 같은 회로를 구현하기가 훨씬 용이해진다. 또한 마이크로스트립 급전방식에 비해 분산이 적으며 광대역특성을 얻을 수 있으며, 접지면과 동일한 면에 급전구조를 구현함으로써 관통 홀을 사용하지 않고 소자의 직렬 및 병렬실장이 용이하기 때문에 회로의 소형화에 유리한 장점이 있다. 무엇보다도 CPW는 급전선과 접지면에 수직으로 전계가 형성되기때문에 마이크로스트립과 달리 완전한 TEM 모드를 구현할 수 있어서 고주파가 될수록 마이크로스트립 보다 전송특성 좋아진다.

(b) 동평면 도파관 구조

(b) 동평면 도파관 단면

그림 2.3. 동평면 도파관 Fig 2.3. CPW(Coplanar waveguide)

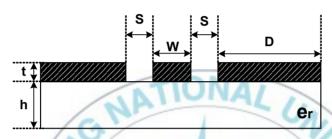

본 연구에서 제안하는 WLP 구조에 사용될 CPW의 신호 전송선은 고주파회로 설계 프로그램인 Advanced Design System의 Line Calk.를 사용하여 특성 임피던스 매칭이 50ohm이 되도록 계산하였는데, 중심통과주파수를 이동통신기기 등에서 가장 많이 사용되는 주파수 대역인 2GHz를 기준으로 계산하였다. 그에 따라 150um의 신호전송선 선폭을 갖도록 하였고, 신호전송선과 접지선 사이의 간격을 90um로 하였으며 신호전송선의 길이는 600um로 산정하였다.

그림 2.4(a)는 설계프로그램으로 계산된 CPW 등가회로를 나타내고 있으며, 이 회로를 기반으로 주파수 특성을 시뮬레이션 하였다. 그림 2.4(b)는 등가회로의 시뮬레이션 결과를 나타낸다. 실제제작공정을 통해 만들어진 소자는 측정을 위한 리드선 등에서기생성분으로 유도성 및 용량성 잡음을 가지게 되는데, 이러한기생성분들을 시뮬레이션에 모델링하여 몇 가지 조건에서 수행한주파수 응답을 제4장에서 언급할 것이다.

# (b) 삽입손실

그림 2.4. 동평면 도파관 시뮬레이션 결과 Fig. 2.4. CPW simulation result

### 제3장 제안된 웨이퍼 레벨 패키징

### 3.1. 웨이퍼 레벨 패키지 설계

그림 3.1은 애질런트사의 고주파소자인 FBAR(Film Bulk Acoustic Resonator) 소자용 WLP 구조의 초기 모델을 나타낸 것이다. 그림 3.1에서와 같이 고주파 소자(RF device)가 형성된 Base Wafer와 관통된 well이 형성된 유리 재질의 cap 웨이퍼를 솔더로 접합한 후, 기계적 가공으로 형성된 well을 통한 와이어 본딩으로 전기적 연결을 하는 방식이다. 일반적인 패키징 방식에 비해 공정과정과 패키지 크기가 획기적으로 축소되었다.

Fig. 3.1. WLP structure for FBAR device of Agilent Technologies, inc.

이러한 구조보다 패키지의 소형화 및 공정과정을 보다 더 간소화 한 형태는 그림 3.2와 같다. 그림 3.2는 cap의 소재를 유리에서 실리콘으로 대체하고, 기존의 well 부분은 실리콘 DRIE (Deep Reactive Ion Etching) 방법을 이용하여 50um 이하의 관통 홀을 형성하였다. 형성된 관통 홀에 구리 전해도금 방법을 이용하여 전기

적으로 연결하였다. 최근의 WLP 기술은 초박형화 및 저가격화를 위한 cap 웨이퍼의 개발에 집중되어 있다[12~14].

그림 3.2. DRIE 및 도금 공정 기반의 WLP 구조 Fig. 3.2. DRIE and plating-based WLP structure

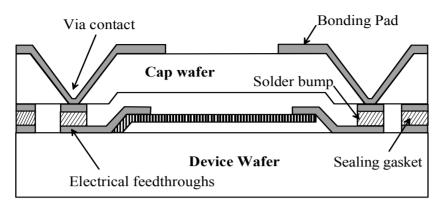

본 연구에서는 패키지 웨이퍼의 본딩 면을 1차로 가공하고 이를 소자 웨이퍼와 본딩시킨 다음에 나머지 면을 가공할 수 있는 새로운 패키지 구조를 제안한다. 또한 종래에는 전기배선이 공동의 바닥면을 따라 웨이퍼의 반대편으로 연결되어 배선 길이가 상대적으로 길었으나 본 연구에서는 소자의 입출력 단자 바로 위에서 웨이퍼의 반대편으로 연결함으로써 배선길이를 보다 짧게 하고자 하였다. 그림 3.3은 본 연구에서 제안하는 고주파 소자용 밀봉 공동을 가진 WLP의 단면도를 나타낸 것이다. 소자 웨이퍼는 active element 등 고유의 구성 요소 이외에 패키징을 위해서 밀봉에 필요한 개스킷과 입출력 신호를 패키지 웨이퍼로 전달하기 위한 electrical feed-through가 추가된다.

그림 3.3. 제안된 WLP 단면도

Fig. 3.3. Cross-sectional view of the proposed WLP

한편 패키지 웨이퍼는 소자의 active element가 수 마이크로미터 높이의 moving part를 가질 경우에 대비하여 이를 수용하기 위한 공동과, 소자의 입출력 단자를 외부로 전달하기 위한 관통전극과 이것을 외부회로와 연결하기 위한 와이어 본딩패드 소자의 active element를 보호하기 위한 밀봉 개스킷을 주요 구성요소로 한다. 소자 웨이퍼와 패키지 웨이퍼의 본딩에는 Au/Sn 솔더를 사용한다. Au/Sn 솔더는 제조비용이 높다는 단점을 제외하고는 매우 낮은 leakage rate, 높은 전기전도도, 높은 본딩강도 등 웨이퍼 본딩 재료로서 매우 우수한 특성을 가지고 있다. Au/Sn 솔더 본딩의 또다른 장점은 웨이퍼 본딩, hermetic sealing 그리고 소자 웨이퍼와 패키지 웨이퍼 간의 전기적인 연결을 동시에 제공할 수 있다는 것이다. 이는 공정의 단순화를 통해 고가인 재료비의 단점을 보완해준다.

관통 인터커넥션의 형성방법은 공정순서와 위치만 바뀌었을 뿐기존의 공정과 동일하다. 즉, 본딩 면에 다층 금속막으로 구성된 전기배선(electrical feed-through)을 형성하고 웨이퍼의 반대편에서

실리콘을 식각하여 반대편의 금속막을 드러낸다. 금속이 드러나면 식각을 멈추고 그 위에 새로운 다층 금속을 형성하여 비아 인터커 넥션과 와이어 본딩 패드로서 사용하게 된다. 이때 비아 홀의 형 성방법으로 이방성 습식식각을 사용한다. 이방성 습식식각은 역 파리미드형의 식각형태를 갖는데 식각창의 면적에 의해 식각 깊이 및 바닥면의 형태를 정확히 제어 가능한 이점이 있다. 한 가지 단 점으로는 비아 홀의 바닥 면적에 비해 표면적이 매우 크기 때문에 제한된 면적에 많은 수의 비아 홀을 형성할 수 없는 점을 들 수 있다. 다행히 대부분의 고주파 소자, 센서 및 MEMS 소자는 입출 력 단자 수가 많지 않기 때문에 큰 문제가 되지 않는다. 관통 인 터커넥션의 위치가 공동의 바닥으로부터 소자의 입출력 단자 바로 위로 변경되었는데 이것은 인터커넥션의 길이를 보다 짧게 함으로 써 기생 인덕턴스를 최대한 줄이기 위한 것이다. 그러나 이를 위 해서 최종적인 웨이퍼의 두께를 이전 보다 얇게 할 필요가 있지만 이것은 웨이퍼 본딩 이후에 이루어지므로 이로 인한 부작용은 없 을 것으로 예상된다.

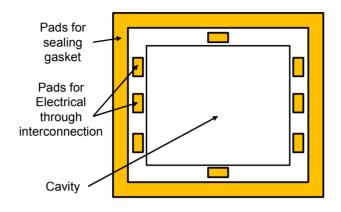

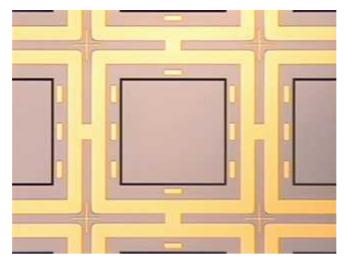

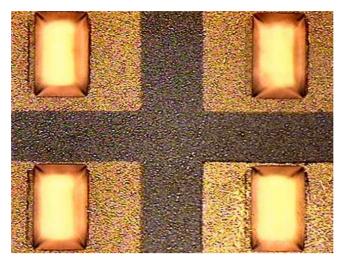

그림 3.4는 본 연구에서 설계한 패키지 웨이퍼의 평면도를 나타 낸 것이다. 금속 패드 위에 위치하는 솔더 패턴은 폭과 길이가 금 속패드 보다 각각 5um씩 작게 설계하였다. 이때 마이크로스트립 라인에 필요한 2개의 패드를 제외한 나머지는 단순히 패키지 웨이 퍼의 상과 하를 연결하는 기능만 가진다. 밀봉링의 면적과 접촉패 드의 면적을 합한 전체 본딩 면적은  $0.315mm^2$ 가 된다. 패키지 웨 이퍼의 윗면(외부와 접촉하는 면)에는 바닥면과 전기적으로 연결된 비아 인터커넥션과 PCB 등 외부 회로와 연결하기 위한 와이어 본 딩 패드가 형성된다. 공동과의 전기적인 연결을 위한 비아 홀의 면적은  $70um \times 120um$ 로 하였다. 이때 공동과 직접 접촉하는 바닥 면적은  $20um \times 80um$ 로 설계하였다[13].

그림 3.4. 제안된 WLP 평면도 Fig. 3.4. Top view of the proposed WLP

고주파 박막 소자를 위한 패키지의 개발에 있어 실제 소자 웨이퍼를 사용하는 것이 이상적이긴 하지만, 본 연구에서는 고주파 소자를 위한 비용절감형 패키지에 중점을 두고, 소자 웨이퍼를 대신하는 더미 웨이퍼를 자체 설계하고 이에 대응되는 패키지 웨이퍼를 설계하였다. 더미 웨이퍼지만 실제 소자의 크기와 입출력 단자의 위치 및 수 등은 동일하게 배치하였다. 한 웨이퍼 내에는 적어도 수 천개 이상의 칩이 들어가므로 여러 종류의 시험용 패턴을 설계해 볼 수 있다.

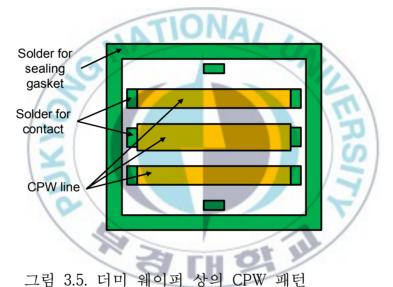

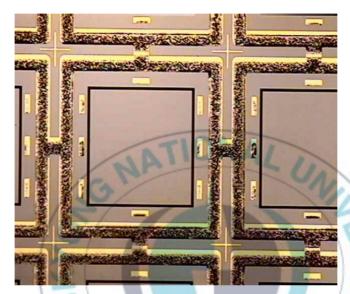

그림 3.5는 그 중에서 더미 웨이퍼와 패키지 웨이퍼의 직류 및 고주파 특성을 평가하기 위해 설계한 CPW 패턴을 나타낸 것이다. 패키지 칩의 크기는  $1.04 \times 1.04 mm^2$ 로서 칩과 동일한 패키지 면적

을 가진다. 패턴의 길이는 680um이고 폭은 150um이다. 공동은 칩의 중앙에 한 변이 520um인 정사각형으로 설계하였고 웨이퍼의접합 및 밀봉을 위한 개스킷의 폭은 80um로 하였다. 이는 모의실험으로 충분한 기계적인 강도와 낮은 누설특성을 가질 수 있음을확인하고 설계한 값이다. 이때 전체 밀봉링의 면적은  $0.303mm^2$ 가된다.

소자 웨이퍼의 입출력 단자와 연결되는 컨택 패드의 크기는 공정 마진과 기계적인 접합 강도 및 전기적인 접촉저항을 고려하여  $35um \times 110um$ 로 설계하였고, 한 개의 칩에는 8개의 패드를 배치하였다. 따라서 전체 패드 면적은  $0.012mm^2$ 이다.

Fig. 3.5. CPW pattern of dummy wafer

### 3.2. 웨이퍼 본딩 기술 및 재료 선정

웨이퍼 본딩을 이용하는 WLP에 있어서 본딩 방법의 선택은 매우 중요하다. 웨이퍼 본딩 방법은 표 3.1에 나타낸 바와 같이 surface bonding, metallic interlayer bonding 및 insulator interlayer bonding으로 크게 구분할 수 있다[12]. 이들 각종 본딩 방법은 고유의 특성과 장단점을 가지고 있어서 용도에 따라서 최적의 본딩 방법을 선택하는 것이 필요하다.

표 3.1. 웨이퍼 본딩 기술의 종류 및 특징 Table 3.1. Wafer bonding method and properties

| Bonding method |                    | Tempe-<br>rature(℃) | Herme-<br>ticity | Relia-<br>bility | Bond<br>strength<br>MPa | Comments                        |  |

|----------------|--------------------|---------------------|------------------|------------------|-------------------------|---------------------------------|--|

|                | anodic bonding     | medium,             | yes              | good             | >30                     | requires flat surface,          |  |

|                |                    | 200-500             |                  |                  | n v                     | high voltages                   |  |

| Surface        | fusion bonding     | very high,          | yes              | good             | >20                     | requires surface prepa-         |  |

| bonding        | -                  | 700-1400            |                  |                  |                         | ration, flat surface            |  |

|                | surface activated  | very low,           | yes              | not              | >10                     | requires flat surface,          |  |

|                | bonding            | RT-200              |                  | certain          |                         | surface preparation             |  |

|                | eutectic bonding   | medium,             | ves              | not              | 20                      | particle insensitive            |  |

|                | editectic boliding | 180-400             |                  | certain          | 20                      | particle insensitive            |  |

| Metallic       | thermo-compression | medium,             | not              | not              | 10                      | very high pressure,             |  |

| interlayer     | bonding            | 350-500             | certain          | certain          | 10                      | particle insensitive            |  |

|                | solder bending     | low,                | Woo              | not              |                         | partiala inconsitivo            |  |

|                | solder bonding     | 180-300             | yes              | certain          |                         | particle insensitive            |  |

|                | adhasiya handina   | low,                |                  | not              |                         | very particle insensitive,      |  |

| Insulating     | adhesive bonding   | RT-300              | no               | certain          | 10-25                   | very versatile                  |  |

| interlayer     | alone fuit bonding | med./high,          |                  | and d            |                         | particle insensitive, versatile |  |

|                | glass-frit bonding | >400                | yes yes          | good             |                         |                                 |  |

이를 위해서는 먼저 소자의 특성과 요구사항을 파악하는 것이 선 행되어야 한다. 고주파 소자 특히 박막형 진동자와 같은 다이아프 램형 소자는 음향주파수로 진동하는 진동체를 가지고 있고 진동체 의 질량이 매우 작기 때문에 미세한 먼지나 수분 심지어는 산소 및 탄소와 같은 가벼운 원자의 부착에 의해서도 진동주파수가 달 라질 수 있다. 따라서 고주파 소자와 같은 박막형 고주파 소자는 매우 엄격한 밀봉(hermetic sealing)을 필요로 한다[13~14]. 웨이퍼 본딩 기술에 있어서 완전한 밀봉을 해줄 수 있는 방법은 접착제나 에폭시를 제외한 대부분의 본딩 기술이 사용가능하다. 그 다음으 로 고려할 사항은 본딩 온도이다. 본딩 온도가 약 400℃ 이상으로 지나치게 높으면 소자의 특성을 변화시킬 수 있으므로 가능한 낮 은 온도에서 하는 것이 바람직하다. 또 다른 고려사항은 부가적인 기능으로써, 밀봉과 전기적인 연결을 동시에 제공할 수 있으면 그 만큼 공정수와 비용을 줄일 수 있다. 이러한 여러 가지 사항들을 고려해 볼 때 박막형 고주파 소자를 위한 WLP에는 eutectic 본딩 혹은 솔더 본딩이 가장 유리하다고 할 수 있다. 그 중에서도 플럭 스의 사용 없이 직접 솔더링이 가능한 Au/Sn 솔더를 사용한 본딩 이 가장 적합하다고 할 수 있다[14~15].

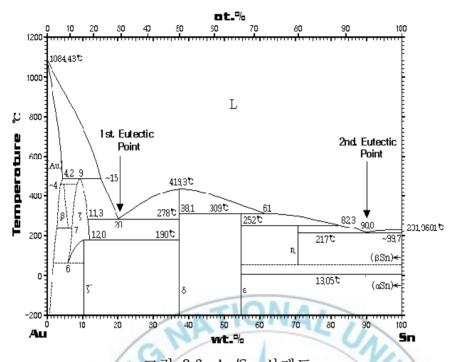

현재 사용되고 있는 Au/Sn 계열의 솔더들은 이미 접합재료로서 1970년대에서부터 연구되어 왔다. 그림 3.6에서와 같이 Au/Sn 합금은 두 곳의 공정점을 가지며, 안정적인 ℰ(Au₅Sn), ℰ(AuSn), ℰ(AuSn₂) 그리고 η(AuSn₄) 상(phase)들을 나타내는 합금이다. 여기서 ℰ과 η상은 309℃ 이하에서 고체 확산에 의해 나타나는 상이며, 309℃ 이상으로 온도가 올라갈 경우 고체와 액체 간의 확산에의해 두상은 소멸되는 특성이 있다. 공정점 솔더의 경우 ℰ상이주로 나타나고 있다. 초기에는 패키징의 sealing 등에 이용되었고,

1990년대에 들어오면서 재료가 갖는 기계적 성질이나 전기적 특성의 장점이 연구되어 전기도금(electro-plating)등에 의한 범프형태로 플립칩 본딩에 이용되기 시작하였다.

표 3.2는 Au/Sn 솔더 및 합금의 기본이 되는 재료인 Au와 Sn에 대한 특성을 나타낸 것이다. 현재 미국과 일본을 비롯한 여러 선진국에서는 이미 공업제품에 대해 환경규제가 적용되어 가면서,모든 전자제품에 납(Pb)을 사용하지 않으려는 움직임이 일고 있으며,가까운 시일 내에 이를 실천하기 위해 많은 준비를 하고 있다. 플립칩 본딩 등에 이용되고 있는 솔더의 경우 오래전부터 Pb-Sn계열의 솔더를 사용하고 있으며,현재도 많은 양이 사용되고 있다.하지만 이 Pb-Sn계열의 솔더는 앞으로 환경규제에 의해 그 사용에 많은 제약을 받게 되어, 많은 연구자들은 납이 함유되지 않은 솔더를 개발하여 Pb-Sn계열의 솔더를 대체하려고 노력 중이다.표 3.3은 그 결과를 요약한 것으로 많은 대체 재료들이 연구 중에 있다. 그러나 아직까지는 Pb-Sn 솔더를 완전히 대체할 만한 재료는 만들지 못했으며,기존의 솔더를 대체하기 위해서는 아직도

에 있다. 그러나 아직까지는 Pb-Sn 솔더를 완전히 대체할 만한 재료는 만들지 못했으며, 기존의 솔더를 대체하기 위해서는 아직도비용, 융점, 접합강도, 젖음성, 크립 저항성, 피로 저항성 및 금속층과의 계면 반응특성 등이 개선될 필요가 있다. 이와 같은 상황에서 플럭스를 사용하지 않으면서, 동시에 적은 양으로도 충분한전단응력을 보이는 Au/Sn은 매력적인 재료로 연구되고 있다.

그림 3.6. Au/Sn 상태도

Fig. 3.6. Au/Sn state diagram

표 3.2. 솔더 재료들의 특성

Table 3.2. Properties of solder materials

| 재       | 1     |                     | AuSn(8:2) | Au    | Sn     |

|---------|-------|---------------------|-----------|-------|--------|

| ㅁ키지 돈 시 | 비중    | 130                 | TH S      | 19.32 | 7.3    |

| 물리적 특성  | 탄성계수  | kg/mm²              | 6000      | 7800  | 5800   |

| 열적 특성   | 녹는점 ℃ |                     | 280       | 1084  | 231.96 |

|         | 열전도도  | W/mm℃               | 0.25      | 0.3   | 0.066  |

|         | 열팽창계수 | 10 <sup>-6</sup> /℃ | 16        | 14    | 21.2   |

| 전기적 특성  | 전기저항  | <i>μ Ω</i> ·cm      | -         | 2.35  | 11     |

|         | 전기전도도 | $10^6$ /cm $\Omega$ | -         | 0.452 | 0.0917 |

표 3.3. 플립칩 본딩을 위한 다양한 무연솔더 Table 3.3. Various lead-free solders for flip chip bonding

| Alloy composition                                                     | <i>T</i> <sub>m</sub> (℃) | $T_{\mathbb{S}}$ (°C) | $T_1$ (°C) | $T_{\mathrm{e}}$ (°C) |

|-----------------------------------------------------------------------|---------------------------|-----------------------|------------|-----------------------|

| Bi-26In-17Sn<br>Bi-32In<br>Bi-41.7Sn-1.3Zn                            | 79<br>127                 |                       |            | 109.5                 |

| Bi-41Sn-1Ag Bi-42Sn Bi-43Sn (eutectic) Bi-43Sn-2.5Fe                  | 121                       |                       |            | 139<br>139            |

| Bi-45Sn-0.33Ag<br>In-3Ag<br>In-34Bi<br>In-48Sn (eutectic)             | 140-145                   |                       |            | 141<br>110<br>117     |

| Sn-1Ag-1Sb<br>Sn-1Ag-1Sb-1Zn                                          | VAT                       | 222                   | 232        | <b>_</b>              |

| Sn-2.5Ag-0.8Cu-0.5Sb<br>Sn-2.8Ag-20In                                 | 210-216<br>178            |                       | 217        |                       |

| Sn-25Ag-10Sb<br>Sn-2Ag<br>Sn-2Ag-0.8Cu-0.6Sb                          | 233                       | 221                   | 225        | 四                     |

| Sn-2Ag-0.8Cu-6Zn<br>Sn-2Ag-0.8Cu-8Zn                                  |                           | 217<br>215            | 217<br>215 | 35                    |

| Sn-3.5Ag<br>Sn-3.5Ag-(<6)Bi<br>Sn-3.5Ag-1Zn                           | 217                       | 211-221               | 212        | 221                   |

| Sn-3.5Ag-1Zn-0.5Cu<br>Sn-3.6Ag-1.5Zn                                  | 216, 217<br>225           |                       | IL TE      |                       |

| Sn-4.7Ag-1.7Zn<br>Sn-4Ag<br>Sn-4Ag-7Sb                                | 217                       | 221                   | 225<br>230 |                       |

| Sn-4Ag-7Sb-1Zn<br>Sn-10Bi-0.8Cu<br>Sn-10Bi-0.8Cu-1Zn                  |                           | 185                   | 217        |                       |

| Sn-10Bi-0.0Cu-12h<br>Sn-10Bi-5Sb<br>Sn-10Bi-5Sb-1Zn<br>Sn-4.8Bi-3.4Ag |                           | 193                   | 232        |                       |

| Sn-42Bi<br>Sn-45Bi-3Sb                                                |                           | 139<br>145            | 170<br>178 |                       |

# 표 3.3 플립칩 본딩을 위한 다양한 무연솔더 (계속)

Table 3.3. Various lead-free solders for flip chip bonding (continue)

| Alloy composition                                                      | T <sub>m</sub> (℃)    | $T_{\mathrm{s}}$ (°C) | $T_1$ (°C) | $T_{\mathrm{e}}$ (°C) |

|------------------------------------------------------------------------|-----------------------|-----------------------|------------|-----------------------|

| Sn-45Bi-3Sb-1Zn<br>Sn-56Bi-1Ag<br>Sn-57Bi-1.3Zn<br>Sn-5Bi-3.5Ag        | 136.5<br>127          |                       |            |                       |

| Sn-7.5Bi-2Ag-0.5Cu<br>Sn-0.5Cu<br>Sn-0.7Cu (eutectic)                  |                       | 207<br>227            | 212<br>229 | 227                   |

| Sn-2Cu-0.8Sb-0.2Ag<br>Sn-3Cu<br>Sn-4Cu-0.5Ag<br>Sn-10In-1Ag-(0-10.5)Bi | 266-268<br>188-197    | 227<br>216            | 275<br>222 |                       |

| Sn-20In-2.8Ag<br>Sn-42In<br>Sn-5In-3.5Ag                               | 178-189               | 117                   | 140        |                       |

| Sn-10In-1Ag-0.5Sb<br>Sn-36In<br>Sn-50In<br>Sn-8.8In-7.6Zn              | 196-206<br>181-187    | 117<br>117            | 165<br>125 | ER                    |

| Sn-2Mg (eutectic) Sn-5Sb Sn-4Sb-8Zn                                    | 198-204               | 234                   | 240        | 200                   |

| Sn-7Zn-10In-2Sb<br>Sn-8Zn-10In-2Bi<br>Sn-8Zn-4In                       | 181<br>175            | 7 511 7               | 11 11 TO   |                       |

| Sn-8Zn-5In-(0.1-0.5)Ag<br>Sn-9Zn-10In<br>Sn-5.5Zn-4.5In-3.5Bi          | 187<br>178<br>185-188 | LII                   |            |                       |

| Sn-6Zn-6Bi<br>Sn-9Zn (euetctic)<br>Sn-9Zn-5In                          | 127<br>188            |                       |            | 198                   |

|                                                                        |                       |                       |            |                       |

Au/Sn 솔더는 대체로 80(wt.%)Au와 20(wt.%)Sn의 조성을 가진 것을 널리 이용한다. 즉, Au가 중심이 된 합금으로서 높은 전기 전도도와 열전도성을 가지고 있다. 또한 일반적인 연납(soft solder) 등과 비교해 볼 때 매우 높은 접착성(adhesive property)과 부식 저항성을 지니고 있다[16]. 강도면에서도 높은 값을 나타내고 적은 부피로도 접착에 충분한 강도를 얻을 수 있어, 작은 부피의 장비 를 만드는데 유리하다[6]. 특히 열피로에 강하며, 환경규제의 대상 이 되고 있는 납을 함유하고 있지 않고 플럭스 없이 용융이 가능 하다는 장점이 있다. Au와 Sn들은 상온에서도 서로 쉽게 확산을 하여 합금을 이루므로, 균일한 조성의 합금 제작이 용이하다고 보 고되고 있다. 이와 더불어 플립칩 본딩 시 자기 정렬성(self-alignm ent)이 좋기 때문에 높은 정밀도를 갖는 곳에 사용될 수 있다. 또 한 용융에 따른 산화율과 열변형율이 낮기 때문에 100㎞ 이상의 높이를 갖는 솔더의 경우에도 그 정렬오차가 ±1μm 내외로 높은 정밀도를 갖고 있다. 이런 특성들로 인해 광전소자(optoelectronic devices) 패키징에서 유용한 재료로 사용되고 있다. 현재는 플립칩 본딩을 위한 용도 뿐만 아니라, 높은 전단강도와 젖음성을 이용하 여 광섬유의 정렬에도 사용되고 있다[17].

반면에 Au/Sn 합금은 구리와 같이 사용될 경우 그 계면에서 Kirkendall 공공(void)이 발생하여 기계적 성질이 낮아진다[17]. 하지만 광전자에 사용되어지는 경우 Ni이나 Pt, Pd 등이 함께 사용되기 때문에 현재는 큰 문제가 되지 않는다. Au/Sn 합금의 가장 큰 단점은 높은 융점과 가격이다.

Au/Sn(80:20wt%) 합금의 경우, 융점이 약 278℃로 약간 높은 편이다. 따라서 기존에 저융점 솔더를 사용하던 설비를 Au/Sn 솔더로 바꿀 경우 대부분의 장비를 교체해야 하는 단점이 있다. 또한,

Au/Sn 합급은 Au가 많이 함유되어 있기 때문에 그 가격이 높은 편이다. 가격을 낮추기 위해 그림 3.6에서 나타난 두번째 공정점을 이용하여, 합금을 제작할 수 있으나, Sn이 많이 함유될 경우 열피로에 대한 저항력이 낮아지거나 돌기형으로 성장한 금속결정 (whisker)의 성장으로 인해 전기적 단락을 일으킬 수 있다[18~20]. 그러나 현재 광전자 산업에 이용되고 있는 Au/Sn 솔더의 경우 다른 재료들 보다 우수한 전기적 특성이나 기계적 특성으로 인해 충분한 가격경쟁력을 지닌다.

## 3.3. Au와 Sn의 조성비에 따른 기초실험

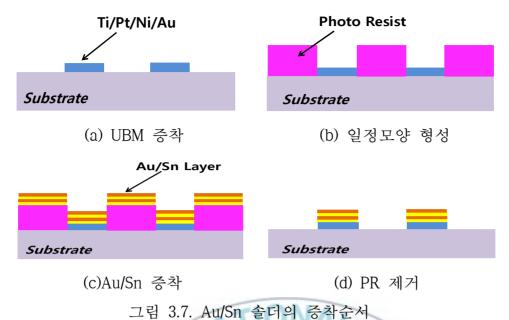

그림 3.6의 상태도에서 보는 바와 같이 Au/Sn 합금계는 크게 두 곳의 공정점이 관찰되고 있다. 솔더 제작 시 그 조직의 균질화와 기계적 및 전기적인 특성들을 고려하여 이 두 곳의 공정점 중 Sn 이 20% 함유되어있는 첫 번째 공정점을 목표로 하였다. 상태도에서 나타난 것과 같이 Au의 함량이 1%만 증가하거나 감소해도 용융온도가 약 30℃ 이상 상승하는 결과를 가져오기 때문에 조성의제어는 매우 중요한 문제이다. 정확한 목표조성을 갖는 Au/Sn 합금의 제작을 위해 본 연구에서는 이미 여러 실험들을 통해 소개되었던 적층(multilayer) 방식을 채택하였다. 여러 층으로 구성된 솔더를 제작하기 위해 진공 증착기(evaporator)를 이용하여 각각의 Au와 Sn의 층을 그림 3.7과 같은 방법으로 Si 기판 위에 적용하였다. 두께에 따른 조성제어를 위해서 식(3.1)을 이용하였다. 우선 Au와 Sn의 비중이 각각 19.32g/cm²와 7.3g/cm²이며, 목표조성은 80:20이므로, 식(3.1)과 같이 표현된다.

$$19.32(g/cm^3)A \times B = 7.3(g/cm^3) \times C$$

(3.1)

식 (3.1)에서 A는 Au와 Sn의 조성이 C:B일 때의 두께 비이다. B는 Sn의 목표조성(%)이며 C(=100-B)는 Au의 목표조성(%)이다. 즉, 동일 면적 상에서 Au와 Sn의 목표조성이 80:20일 경우 Sn 보다 Au의 두께가 약 1.51배가 된다.

Fig. 3.7. Deposition step of Au/Sn solder

실험에 사용된 시편들의 조성은 표 3.4에서 나타낸 것과 같다. 공정조성과 가장 근접한 값인 E 합금을 중심으로 Au가 높게 함유 된 HA 합금과 Sn이 높게 함유된 HS 합금을 제작하였으며, 비교를 위해 Ht 사의 솔더를 사용하였다.

먼저 중착이 끝난 직후의 솔더와 용융(reflow)을 실시한 후의 솔더를 광학현미경으로 관찰하였다. 용융 전후에 솔더가 조성에 따라 그 표면의 모습이 어떻게 변하는지를 관찰하기 위해 주사전자현미경(Scanning Electron Microscopy, SEM) 관찰을 실시하였으며, 동시에 EDS를 통해 용융 후 나타난 솔더의 조성을 조사하였다. 솔더의 기계적 특성을 분석하기 위해서 넓은 면적을 갖는 솔더와 일정한 모양을 갖는 형태의 솔더들로 bonding force(gf)를 측정하였다.

온도에 따라 솔더가 녹는 상태를 관찰하기 위해서 용융실험을 실시하였다. 온도조건은 공정점인 278℃보다 약간 높은 290℃에서부터 일반적인 플립칩 본딩에 사용되는 온도 영역인 320℃까지 실시하였다.

시간은 10초에서 30초까지 변화를 주었다. 온도나 시간의 변화에 따라 각각의 솔더가 크게 변하는 모습은 관찰되지 않았으며, 오직 조성에 따라 녹는 상태가 현저한 차이를 보였다.

표 3.4. 증착성분 Table 3.4. Deposition composition

| UBM(Å) |                 | Solder (each layer : Å) Components(wt.%) |         |      |      |      |      |      |       |       |

|--------|-----------------|------------------------------------------|---------|------|------|------|------|------|-------|-------|

| I.D    | Ti,NI<br>and Pt | Au                                       | Sn      | Au   | Sn   | Au   | Sn   | Au   | Au    | Sn    |

| HS     | 3000            | 4000                                     | 3500    | 3500 | 3000 | 2000 | 3000 | 1000 | 74.52 | 25.47 |

| Е      | 3000            | 4000                                     | 3500    | 3500 | 3000 | 3500 | 1500 | 1000 | 79.88 | 20.12 |

| НА     | 3000            | 4000                                     | 3500    | 3500 | 2000 | 4500 | 500  | 2000 | 86.06 | 13.94 |

| Ht     | 3000            | 6000                                     | Unknown |      |      |      | 80   | 20   |       |       |

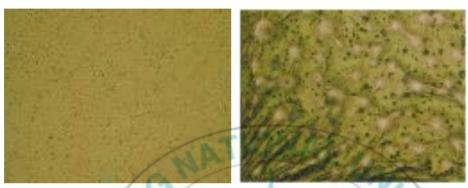

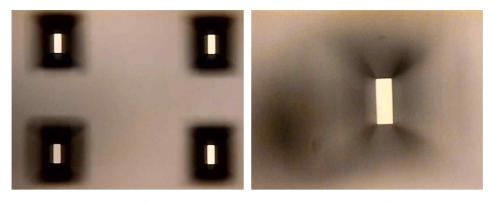

그림 3.8 ~ 3.11은 솔더가 녹은 상태와 증착 직후의 모습을 광학현미경으로 관찰한 것이다. 솔더가 녹은 상태는 실험한 모든 온도와 시간 조건에서 모두 유사하게 나타났으며, 대표적으로 290℃에서 실험한 시편의 사진을 나타내었다. 본 연구에 사용된 솔더들은 부식방지를 위해 가장 상층부에 Au를 일정 두께이상 증착시켜모두 금색을 지니고 있다. 그림 3.8의 HS와 그림 3.9의 HA 솔더는상태도에서 나타난 것과 같이 공정점에서 조성이 변화함에 따라

녹는 온도가 상승하여, 290℃에서는 완전히 녹지 못하는 모습이 관찰되었다. HS 솔더의 경우에는 산맥처럼 융기된 표면들이 형성되었으며, HA의 경우 움푹 패인 형태의 결정립 형성이 관찰되었다. 그림 3.10의 E솔더와 그림 3.11의 Ht사 솔더의 경우 표면이 모두 고르게 녹았으며, 결정립을 형성하지 않았다.

(a) 증착 후 (b) 290℃에서 melting 후 그림 3.8. 광학 현미경으로 관찰한 HS 솔더의 표면 상태 Fig. 3.8. Surface state of HS solder using SEM

(a) 증착 후 (b) 290℃에서 melting 후 그림 3.9. 광학 현미경으로 관찰한 HA 솔더의 표면 상태 Fig. 3.9. Surface state of HA solder using SEM

(a) 증착 후 (b) 290℃에서 melting 후 그림 3.10. 광학 현미경으로 관찰한 E 솔더의 표면 상태 Fig. 3.10. Surface state of E solder using SEM

(a) 증착 후 (b) 290℃에서 melting 후 그림 3.11. 광학 현미경으로 관찰한 Ht 솔더의 표면 상태 Fig. 3.11. Surface state of Ht Solder using SEM

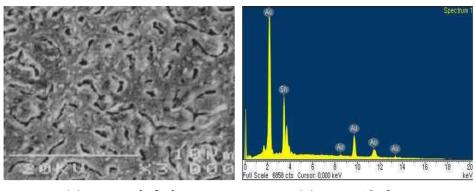

좀 더 정확한 분석을 위하여 Au/Sn 합금 솔더의 reflow 전후의 표면상태를 SEM으로 관찰하고, 그 조성비를 EDS로 분석하였다. 그림 3.12 ~ 3.14는 SEM 및 EDS 분석결과를 나타낸 것이다. 그림에서 나타난 바와 같이 증착이 이루어진 후의 표면에는 작은 입자

형태의 돌기가 형성된 모습이 관찰되었다. EDS 분석결과 부식 방지를 위해 표면에 증착되었던 Au로 인해 Au가 85%이상 함유된 합금들로 나타났다. 표면에 증착된 Au의 두께가 얇고 상온에서도 Au/Sn은 서로 확산되어 합금이 되기 쉽기 때문에 증착 과정이나 증착 후 보관하는 과정에서 확산에 의해 Sn과 합금이 된 것으로 판단된다. E 솔더의 경우 용융 후에 목표로 했던 조성과 유사한 값을 나타내었다. 그러나 HS나 HA의 경우는 표면에 여러 조성들이 나타나고 있다. 특히 융기되거나 함몰된 부분들이 서로 다른 조성들을 보이고 있다.

(a) SEM 이미지 (b) EDS 분석 그림 3.13. HA 솔더의 reflow 결과

Fig. 3.14. Post-reflow results of E solder

각각의 조성에 따른 전단응력을 측정하여 플립칩 본딩 시의 결합력을 알아보았다. 전단응력을 실험하기 위해서 두 가지 시편을 준비하였다. 먼저 Si 기판 전면에 솔더를 증착시켜 실험하였으며, 다른 하나는 그림 3.15와 같이 일정한 형태의 패턴을 만들어 솔더를 증착시켰다. 각 솔더별로 10개의 칩을 사용하여 실험한 결과, 대부분이 칩면적의 70%이상 접착된 것을 확인하였다.

그림 3.15. 전단응력 실험을 위한 일정한 형태의 솔더 Fig. 3.15. Solder of constant type for shear strength experiment

표 3.5는 각각의 조성과 칩의 형태에 따른 전단응력을 표로 나타낸 것이다. 표 3.5에서 나타난 값과 같이 전면에 솔더가 증착되어 결합된 칩의 경우 넓은 면적이 접착되었기 때문에 높은 접착력을 나타내었다. 이에 반해 모양이 형성된 칩은 보다 낮은 값을 나타내었다. 이는 접착하는 부분의 면적차이에 따른 것으로 단일면적에 따른 접착력은 비슷하게 나타났다. 조성에 따른 접착력의 차이는 크게 나타나지 않았다.

표 3.5. 패턴 형태에 따른 전단응력 Table 3.5. Shear strength by pattern types

|     | 전 단 응 력 (gf)    |              |  |  |  |

|-----|-----------------|--------------|--|--|--|

| 시 편 |                 | _            |  |  |  |

|     | without pattern | with pattern |  |  |  |

| HS  | 878             | 221          |  |  |  |

| Е   | 871             | 216          |  |  |  |

| HA  | 879             | 223          |  |  |  |

## 3.4. 웨이퍼 레벨 패키지 공정설계

WLP는 웨이퍼 단위로 1차적인 패키징을 완료하므로 절단된 칩 을 개별적으로 패키징하는 것에 비해 패키징 비용을 절감할 수 있 다. 그러나 이를 위해서는 소자 웨이퍼의 수율과 패키지 웨이퍼의 수율이 함께 충분히 높아야 한다. 일반적으로 동평면 도파관 소자 등은 제조 기술의 발전으로 현재 약 90% 정도의 수율이 가능한 것으로 알려져 있다[21]. WLP에서 패키지 웨이퍼는 소자를 외부 환경으로부터 보호 기능과 함께 소자의 입출력 단자를 외부와 연 결하는 기능을 동시에 수행하여야 한다. 외부 환경과 완전히 단절 된 소자로부터 입출력 단자를 외부와 연결시키기 위해서는 관통전 극(through hole interconnection) 혹은 관통 실리콘 비아(through silicon via)가 필요하다. 관통전극은 웨이퍼를 관통하는 구멍을 형 성하고 이를 양질의 전기전도체이면서 동시에 공기 및 액체의 소 통을 차단할 수 있는 금속 등으로 채워서 만들어진다. 따라서 관 통전극의 형성을 위해서는 패키지 웨이퍼의 양면으로부터 공정이 이루어질 필요가 있다. 패키지 웨이퍼의 양면 공정은 크게 두 가 지 순서로 가능하다. 첫 번째는 웨이퍼의 양면 공정을 소자 웨이 퍼와의 본딩 이전에 모두 완료하는 방법이다. 이 방법의 단점은 패키지 웨이퍼 가공의 전 공정에서 최종적으로 요구되는 두께인  $150 \sim 200um$  정도의 얇은 웨이퍼를 사용하여야 하므로 웨이퍼 파 손 확률이 높다는 것이다. 두 번째 방법은 패키지 웨이퍼의 양면 공정을 본딩전 과 후로 나누어서 하는 방법으로 먼저 본딩면을 1 차로 가공하여 소자 웨이퍼와 본딩시키고 그 다음에 나머지 면의 가공을 완료하는 방법이다. 이 방법의 장점은 패키지 웨이퍼의 전 반부 공정, 즉 본딩 전의 공정에서는 정상적인 두께의 웨이퍼를 사용할 수 있기 때문에 그 만큼 웨이퍼 파손 가능성을 줄일 수 있다는 것이다. 따라서 본 연구에서는 후자의 공정에 대하여 연구하였고, 그 공정 설계도는 그림 3.16에 나타내었다[23 ~ 25].

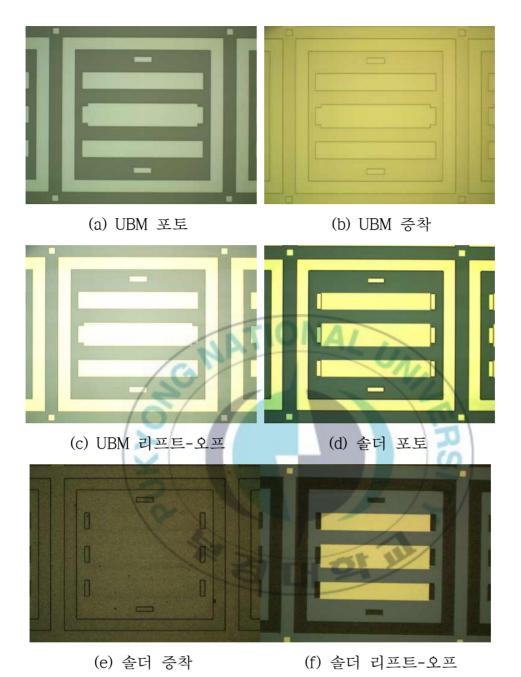

WLP 제작에는 고주파 특성을 고려하여 10 k \(\alpha\) · cm 이상의 비저항을 갖는 300 \(\mu\) 두께의 4인치(100) 실리콘 웨이퍼를 이용하였다. 패키지 웨이퍼를 제작하기 위하여 먼저 웨이퍼의 양면에 동공의 식각 보호막으로서 LPCVD 실리콘 질화막(Si<sub>3</sub>N<sub>4</sub>)을 50 nm 두께로 증착하고, 포토리소그라피 공정 및 건식 식각으로 동공 식각창을 형성한 다음에 25%와 85℃ TMAH 수용액 상에서약 35분간 식각하여 깊이가 20 \(\mu\) 인 동공을 그림 3.16(a)와 같이 형성하였다.

또한 LPCVD 실리콘 질화막(Si<sub>3</sub>N<sub>4</sub>)을 49% HF 용액으로 벗겨낸 후패키지 웨이퍼의 본딩면에 전기적인 배선과 솔더 실링 개스킷의하부 금속막을 리프트-오프 기술을 이용하여 형성하였다. 이를위해 먼저 포토레지스트로 리프트-오프 패턴을 형성하였다. 이공정은 깊이가 20μm인 동공이 형성된 표면에서 이루어지기 때문에스핀 코팅 방식에 비해 step coverage가 좋은 스프레이 코팅 방식을 사용하였다. 리프트-오프 패턴이 완성된 웨이퍼 위에전자빔 증착기를 이용하여 다층 금속막을 증착하였다. 금속패턴은더미 웨이퍼로부터 입출력 신호를 전달 받아 패키지 웨이퍼의반대편으로 전달하는 interconnection 기능과 웨이퍼 본딩에사용되는 솔더의 하부에서 under bump metallization (UBM)의기능을 동시에 수행하게 된다. Interconnection 기능을 위해서는 단순히 낮은 전기저항만 가지면 되지만 UBM에는 여러 가지구비조건이 따른다. 보통 UBM은 3층 구조로 이루어지는데 먼저

최하층은 실리콘과 접착성이 좋아야 하고, 중간층은 솔더재료와 젖음성(wettability)이 좋으면서 확산방지 기능을 가져야 하며, 마지막의 최상층은 보호층으로서 산화방지 기능을 가져야 한다[23]. Au/Sn 솔더용으로 이러한 조건을 모두 만족시키는 UBM 구조는 Cr/Ni/Au, Ti/Ni/Au, Ti/Pt/Au 등이 대표적인데, 본연구에서는 Cr/Ni/Au 구조를 사용하였다. 이때 각 층의 두께는 Cr(100nm)/Ni(200nm)/Au(500nm)로 하여 그림 3.16(b)와 같은 패턴을 형성하였다.

더미 웨이퍼는 패키지 웨이퍼와 동일한 방법으로 CPW 소자와 소자의 입출력 단자를 형성하였다. 금속패턴 형성이 완료된 웨이퍼는 다음 후속 공정인 웨이퍼 본딩을 위해 Au/Sn 솔더의 형성이 필요한데, 본 연구에서는 패키지 웨이퍼에 4μm의 Au를 무전해 방식으로 도금하였고, 더미 웨이퍼에는 진공증착 방법으로 2.9μm의 Sn을 증착하였다. 이때 Sn 표면에 Au를 0.08μm 증착하여 Sn의 산화를 방지하도록 하여 그림 3.16(c)와 같은 패턴을 형성하였다.

제작된 패키지 웨이퍼와 더미 웨이퍼를 그림 3.16(d)와 같이 본당한 후 패키지 웨이퍼의 후면을 연마하여 두께를 낮추었다. 패키지 웨이퍼의 두께는 비아 홀의 크기에 따라 결정되는데 약 100μm의 두께가 되도록 연마하여 그림 3.16(e)와 같이 전체 칩의 두께가 400μm가 되도록 하였다. 연마 과정이 끝나면 이 과정에서 발생한 유기 및 무기 오염을 제거하는 세정공정을 수행한 이후에 비아홀 식각을 위한 식각마스크를 형성하였다. 비아홀은 실리콘의 이방성 습식식각 공정을 이용하여 형성되므로 실리콘 질화막 혹은 실리콘 산화막이 식각마스크로서 적합하다. 하지만 본당된 웨이퍼 는 계면에 저 융점의 솔더 물질이 있으므로 가능한 낮은 온도에서 식각마스크를 형성하는 것이 요구된다.

본 연구에서는 250℃에서 PECVD 방법으로 300nm의 실리콘질화막을 형성하였다. 습식 식각에서는 본딩된 웨이퍼 전체가식각 용액속에 들어가므로 본딩된 웨이퍼의 후면을 보호하기 위해전면과 동일한 실리콘 질화막을 증착하였다. 패키지 웨이퍼면의상부에 관통 홀 식각 창을 형성한 후, 85℃와 25%의 TMAH수용액 상에서 실리콘 기판을 에칭하여 관통 홀을 형성하였다. 이때 식각 시간을 조절하여 관통 홀의 바닥에 반대편의 금속패턴이 드러난 이후에 반대편의 금속층이 손상되지 않도록 하여 그림 3.16(f)와 같은 패턴을 형성하였다.

관통 홀의 형성이 끝나면 마지막으로 관통 홀에 관통전극 및 와이어 본딩 패드를 위한 금속패턴을 형성하게 되는데, 앞서기술한 바와 같이 사진전사 공정과 전자빔 진공증착 및 리프트-오프 방법을 통해 금속패턴을 형성하였다. 금속층의 구조는 그림 3.16(g)와 같이 Ti(100nm)/Ni(200nm)/Au(1,000nm)로 하였다.

그림 3.16. 제안된 WLP 공정도 Fig. 3.16. Proposed WLP process

## 3.5. 패키지 웨이퍼의 제조공정

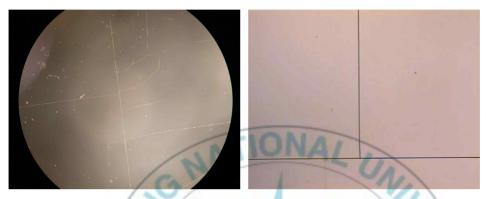

실험에는 4인치(100) 실리콘 웨이퍼로서 고주파 특성을 고려하여  $10k \Omega \cdot cm$  이상을 갖는 고저항 웨이퍼를 사용하였고, 초기 웨이퍼의 두께는  $300\mu m$ 였다. 먼저 웨이퍼의 양면에 공동의 식각 보호막으로서 LPCVD 실리콘 질화막(Si<sub>3</sub>N<sub>4</sub>)을 50nm 두께로 성장하였다. 포토리소그라피 공정 및 건식 식각으로 공동 식각창을 형성한 다음에 25%, 와 85℃ TMAH 수용액 상에서 약 35분간 식각하여 깊이가  $20\mu m$ 인 공동을 형성하였다. 이어서 LPCVD 실리콘 질화막(Si<sub>3</sub>N<sub>4</sub>)을 49% HF 용액으로 제거하였다. 그림 3.17은 공동을 식각한 것으로 표면 및 형태가 매우 양호한 것을 확인할 수 있다.

(a) 공동형성 (b) 실리콘 질화막 제거 후의 그림 3.17. 실리콘 질화막 제거 전 후의 공동 Fig 3.17. Cavity of pre- and post- Si<sub>3</sub>N<sub>4</sub> cancellation

패키지 웨이퍼의 본딩면에 전기적인 배선과 솔더 실링 개스킷의 하지 금속막을 리프트-오프 기술을 이용하여 형성하였다. 이를 위 해 먼저 포토레지스트로 그림 3.18과 같이 리프트-오프 패턴을 형 성하였다. 이 공정은 깊이가 20µm인 공동이 형성된 표면에서 이루어지기 때문에 스핀 코팅 방식에 비해 step coverage가 좋은 스프레이 코팅 방식을 사용하였다.

그림 3.18. 금속패턴 형성을 위한 리프트-오프 패턴 Fig. 3.18. Lift-off pattern for metal pattern formation

리프트-오프 패턴이 완성된 웨이퍼 위에 전자빔 중착기를 이용하여 그림 3.19와 같이 다층 금속막을 중착하였다. 그림 3.19는 포토레지스터의 전용 remover에서 포토레지스터를 제거한 후 패키지웨이퍼 상에 형성된 금속패턴을 보여주고 있다.

금속패턴은 소자 웨이퍼로부터 입출력 신호를 전달 받아 패키지 웨이퍼의 반대편으로 전달하는 interconnection 기능과 웨이퍼 본 당에 사용되는 솔더의 하부에서 UBM의 기능을 동시에 수행하게된다. Interconnection 기능을 위해서는 단순히 낮은 전기저항만 가지면 되지만 UBM은 여러 가지 구비조건이 따른다.

마지막의 최상층은 보호층으로서 산화방지 기능을 가져야 한다. Au/Sn 솔더용으로 이러한 조건을 모두 만족시키는 UBM 구조는 Cr/Ni/Au, Ti/Ni/Au, Ti/Pt/Au 등이 대표적이다. 본 연구에서는 이들모두를 사용하였지만 Cr/Ni/Au 구조를 가장 많이 사용하였다. 이때각 층의 두께는 Cr(100nm)/Ni(200nm)/Au(500nm)로 하였다. 그림 3.20에서와 같이 전자빔의 증착 과정에서도 열에 의한 포토레지스터의 변형이 관찰되지 않았다.

Fig. 3.19. UBM deposition on lift-off pattern

그림 3.20. 리프트-오프 후의 UBM 패턴 Fig. 3.20. UBM pattern after a lift-off process

금속패턴 형성이 완료된 웨이퍼는 후속 공정인 웨이퍼 본딩을 위해 Au/Sn 솔더의 형성이 필요하다. Au/Sn 솔더는 합금을 기판혹은 패키지 웨이퍼의 어느 한 쪽에 형성하는 방법과 Au와 Sn을 각각 두 웨이퍼에 나누어서 형성하는 방법이 가능하다[26~27]. 본연구에서는 위 두 가지 방법을 모두 실험하였다. 그리고 수um 두께의 Au를 진공증착으로 하게 되면 단가가 매우 높기 때문에 이를 무전해 도금으로 하는 방법도 시도하였다.

그림 3.21은 패키지 웨이퍼 상에 무전해 도금공정으로 Ni (1um)/Au(3um)이 형성된 사진을 나타낸 것이다. 도금공정의 특성 상 전반적으로 표면이 거칠고 웨이퍼 내 두께 균일도는 약  $\pm 0.5um$  정도로서 진공증착에 비해 감소하였다. 무전해 도금의 장점은 생산 원가가 매우 저렴하고 사진전사공정과 같은 부가적인 공정이 필요치 않다는 점이다.

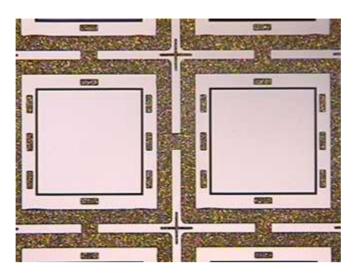

그림 3.22는 완성된 패키지 웨이퍼의 전체를 나타낸 것이다.

그림 3.21. Ni/Au 층을 추가한 금속패턴 Fig. 3.21. Metal pattern with Ni/Au layer

그림 3.22. 완성된 패키지 웨이퍼 Fig. 3.22. Fabricated package wafer

## 3.6. 동평면도파관 웨이퍼의 제조공정 및 결과

기판 웨이퍼는 패키지 웨이퍼와 동일한 방법으로 직류 및 고주파 특성 측정을 위한 CPW 패턴과 소자의 입출력 단자를 형성하였다. 그 다음으로 Au/Sn 합금을 형성하는 방법으로 기판 웨이퍼에 형성하였다. Au/Sn 합금은 진공증착기를 이용하여 Au와 Sn을 교대로 적충하고, Au와 Sn의 전체 두께를 조절하여 Au 함량이 75wt.%인 Au/Sn 합금을 형성하였다. 솔더 패턴의 형성에는 금속배선과 동일한 리프트-오프 기술을 이용하였다.

마지막으로 Au와 Sn을 각각 다른 웨이퍼에 형성하는 방법은 Au 및 Sn의 두께만 다를 뿐 Au/Sn 합금 형성 방법과 동일하게 하였다. 패키지 웨이퍼에는 Au를 2um이상 증착하였고 기판 웨이퍼에는 Sn을 2.9um 두께로 형성하였다. 이때 Sn 표면에 Au를 0.08um 증착하여 Sn의 산화를 방지하도록 하였다.

Au/Sn 혹은 Au와 Sn의 솔더 접합층 형성 공정이 끝난 다음에 웨이퍼 본딩 시 기판 웨이퍼와 패키지 웨이퍼의 정렬에 필요한 웨이퍼 정렬 패턴을 형성하였다. 웨이퍼 본딩 시스템은 크게 본딩용지그, 마스크 정렬장비 및 본딩장비 3 가지로 구성된다. 지그는 본딩하고자 하는 두 웨이퍼를 서로 정렬하여 임시로 고정시키는 장치이고, 마스크 정렬장비는 일반적으로 반도체 제조에 사용되는 mask aligner 장비와 동일한데 단지 본딩용 지그를 수용할 수 있도록 제작된 것이다. 그리고 웨이퍼 본딩장비는 웨이퍼 지그를 수용하여 가압 및 가온할 수 있는 장비이다. 웨이퍼 본딩용 마스크 정렬 장비에서 웨이퍼의 정렬 과정을 살펴보면 먼저 cap 웨이퍼를

그림 3.23. Au/Sn 합금 솔더층이 형성된 기판 웨이퍼의 공정별 단계 Fig. 3.23. Process steps of substrate wafer with Au/Sn solder layer

패턴이 형성된 면이 아래를 향하도록 하여 top 지그 위에 장착한다. Back side 렌즈를 통해 정렬키를 확인하고 이를 화면캡처하여이미지로 저장한다. 다음에 기판 웨이퍼를 bottom side 지그 위에올려놓고 역시 Back side 렌즈를 통해 웨이퍼의 배면에 형성된 정렬키를 미리 저장된 이미지와 정렬하여 맞추게 된다. 따라서 본당하고자 하는 두 웨이퍼 중 어느 한 웨이퍼의 배면에 웨이퍼 정렬에 필요한 정렬패턴이 필요하게 된다. 이를 위해 기판 웨이퍼의배면에 웨이퍼 정렬에 필요한 정렬 패턴을 건식식각을 통해 형성하였다.

그림 3.24는 기판 웨이퍼의 배면에 형성된 웨이퍼 본딩 정렬키패턴이다. 정렬 패턴은 웨이퍼의 중앙에서 좌와 우로 약 66mm떨어진 지점에 형성하였다.

그림 3.24. 기판 웨이퍼의 배면에 형성된 웨이퍼 본딩용 정렬 패턴 Fig. 3.24. Align pattern for bonding with substrate wafer back side

그림 3.25는 웨이퍼 본딩 전까지 완료된 기판 웨이퍼를 나타낸 것이다.

그림 3.25. 완성된 기판 웨이퍼의 사진 Fig. 3.25. Photograph of completed substrate wafer

## 3.7. 웨이퍼 레벨 본딩공정 및 후공정

웨이퍼 본딩에 사용한 Au/Sn 솔더의 구조와 각각의 본딩조건 및 결과를 표3.6에 요약하여 나타내었다. 웨이퍼 본딩조건은 크게 Au 와 Sn을 각각 따로 형성한 경우와 Au/Sn 합금을 기판 웨이퍼에 형 성한 경우로 구별된다. Au와 Sn을 따로 형성한 경우 Sn의 융점이 238℃로서 낮기 때문에 275℃ ~ 290℃ 범위에서 20분간 본딩하였 다. 275℃ 및 280℃ 본딩 결과 압력이 5,000N 이상으로 높을 경우 에는 크랙이 발생하였고, 모든 압력 범위에서 전체적으로 혹은 국 부적으로 본딩이 제대로 되지 않는 unbonded 영역이 나타났다. Au 와 Sn을 따로 형성한 경우에 가장 적합한 본딩조건은 285℃ 및 290℃에서 5,000N의 압력으로 실시한 경우였다. 이 조건에서는 크 랙 및 국부적인 unbonded 영역도 발생하지 않았다. Au/Sn 합금 솔 더의 경우에는 보다 높은 온도인 290℃ 및 315℃에서 3,000N, 4,000N 및 5,000N의 압력으로 본딩하였다. 290℃에서는 솔더가 잘 녹지 않아 본딩이 전혀 이루어지지 않은 경우도 발생하였다. 그러 나 이 경우 본딩 장비에서 실제 온도가 설정 온도에 미치지 못했 기 때문인 것으로 판단된다. 왜냐하면 Au75wt.%Sn 합금은 외부에 서 실시된 멜팅 실험결과 280℃에서부터 녹는 것이 뚜렷이 관찰되 기 때문이다. 315℃에서 본당한 결과도 전 압력 범위에서 국부적 인 unbonded 영역이 발생하지 않았다. 따라서 Au/Sn 합금 솔더에 적합한 본딩온도는 315℃ ~ 320℃ 범위 이고, 압력은 약 5,000N이 라고 할 수 있다. 웨이퍼 본딩 시 분위기는 진공 분위기와 질소 분위기 두 가지로 진행하였고 결과의 큰 차이는 관찰되지 않았다.

표 3.6. 웨이퍼 본딩을 위한 Au/Sn 솔더의 구조 및 본딩 결과

Table 3.6. Structure and bonding result of Au/Sn solder for wafer

bonding

|           | Bonding     | Parameters &         | D = 0 = 0     |                     |  |

|-----------|-------------|----------------------|---------------|---------------------|--|

| Solder 구조 | Temp<br>(℃) | Pressure<br>(Newton) | Time<br>(min) | 본딩결과                |  |

|           | 275         | 5000                 | 20            | Unbonded, Low temp  |  |

|           | 280         | 7,000                | 20            | Cracks, Low temp    |  |

| Au + Sn   | 280         | 6,000                | 20            | Cracks, Low temp    |  |

| Au + Sii  | 280         | 5,000                | 20            | Cracks, Low temp    |  |

|           | 285         | 5,000                | 20            | No cracks, Good     |  |

|           | 290         | 5,000                | 20            | No cracks, Good     |  |

| Au75wt%Sn | 290         | 4000                 | 1             | Unbonded, Low temp  |  |

|           | 315         | 5,000                | 2             | Cracks, unbonded    |  |

|           | 315         | 4,000                | 2             | No cracks, unbonded |  |

|           | 315         | 3,000                | 2             | No cracks, unbonded |  |

|           |             | 0                    | / LH          | 91                  |  |

표 3.6의 결과에 대하여 웨이퍼 본딩 시 관찰되었던 대표적인 불량원인을 분석하였다. 그림 3.26은 본딩된 웨이퍼의 정렬 정밀도를 확인하기 위해 본딩된 시료를 분리하여 내부를 관찰한 사진이다. 금속패턴 위에 솔더가 한 쪽으로 치우처진 상태로 본딩 되었음을 알 수 있다. 웨이퍼 본딩 시 이러한 misalignment는 빈번히

발생하지는 않았지만 사용된 장비의 결함으로 발생할 수 있다. 웨이퍼 본딩 시 이러한 misalignment가 약 5um이하일 경우에는 본딩 강도가 낮아지고 직류 및 고주파 삽입 손실이 증가하지만 그이상일 경우에는 본딩이 제대로 이루어지지 않을 것으로 예상된다.

그림 3.26. 웨이퍼 본딩 시 misalignment Fig 3.26. Misalignment in wafer bonding

또한 웨이퍼 본딩 시 가장 빈번히 발생하는 불량은 크랙이었다. 그림 3.27은 웨이퍼 본딩 시 관찰되는 크랙을 나타낸 것이다. 크랙은 실리콘 웨이퍼의 결정방향을 따라 직선 형태로 발생하는 것과임의의 형태를 가지는 두 종류로 나타난다. 크랙의 원인은 과도한압력, particle 장비 불량, 웨이퍼 warpage 등 다양하다. 그러나 실질적으로는 particle과 warpage는 공정과정에서 적절히 관리되었기때문에 장비 불량과 과도한 압력에서 오는 경우가 대부분 이다.

먼저 압력은 7,000N에서 3,000N까지 1,000N씩 감소시키며 실험한 결과 4,000N 이하의 압력에서는 크랙이 발생하지 않았다. 그러나 4,000N 이하의 본딩 압력에서는 국부적으로 본딩이 되지 않는 영역이 관찰되었는데 사용 장비에 따라서 많은 차이를 나타내었다. 본딩 온도는 크랙의 발생과 큰 상관관계가 없는 것으로 나타났다.

(a) 크랙 사진

(b) 확대 사진

그림 3.27. 본딩된 웨이퍼 뒷면에서 관찰되는 크랙

Fig. 3.27. Crack in bonded wafer back side

그림 3.28은 본딩이 제대로 이루어지지 않은 부분의 웨이퍼를 분리하여 접합부를 관찰한 사진이다. 본딩이 되지 않은 영역은 금속패턴 위에 솔더가 거의 묻어있지 않은 것을 알 수 있다. 실리콘웨이퍼는 열전도도가 매우 좋기 때문에 웨이퍼 내에서 국부적인 온도 차이는 많지 않을 것으로 예측된다. 따라서 국부적인 unbonding은 낮은 압력에 기인하는 것으로 판단된다.

그림 3.28. 국부적으로 본딩되지 않은 영역의 decap 사진 Fig. 3.28. Decap photograph of locally unbonded area

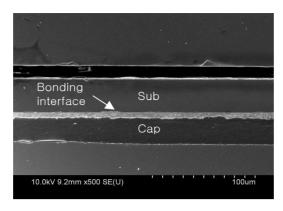

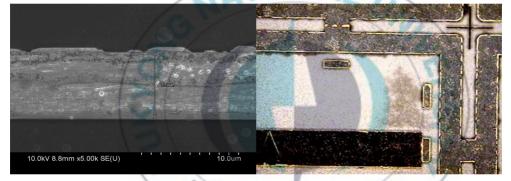

웨이퍼 본딩 시 발생한 불량의 원인을 분석하기 위하여 접합부의 단면을 SEM으로 분석하였다. 그림 3.29는 Au와 Sn을 각각 패키지 웨이퍼와 기판 웨이퍼에 중착하고, 280℃에서 7,000N의 압력으로 20분간 본당한 접합부의 SEM 사진을 나타낸 것이다. 이 시료는본딩 압력이 충분히 높은데도 불구하고 솔더충과 패키지 웨이퍼가제대로 본딩되지 않은 경우이다. 이러한 현상은 웨이퍼의 일부에서만 관찰되는 것이 아니고 거의 전체에서 관찰되었다.

(a) 접합부 단면

(c) unbonded 접합부 확대(void)

그림 3.29. Au 및 Sn을 이용하여 본딩한 접합부의 단면

Fig. 3.29. Cross-sectional view of bonded junction part using Au and Sn

순수한 Sn의 융점은 약 240℃이고 Au80wt.% Sn의 융점은 약 280℃이다. 따라서 정상적인 경우 Sn이 용융되면서 Au와 반응하여 AuSn4, AuSn2, AuSn, Au5Sn 등 융점이 280℃ 이하인 Au/Sn의 intermetallic을 형성하여 본딩이 이루어져야 한다. 그러나 만약 실제 온도가 280℃ 이하일 경우에 Sn은 극히 일부의 Au와 반응하여 AuSn4 및 AuSn2 상만 형성하고 Au rich의 다른 상들은 생성되지 않게 된다. 이것도 시간이 충분한 경우이고 본딩 시간이 충분하지 못하면 Sn rich상들도 생성하기 어렵게 된다. 따라서 이 경우에는 장비의 설정온도는 280℃ 였지만 실제 웨이퍼의 온도는 이 보다 훨씬 낮은 것으로 판단된다. 솔더 층의 내부에서도 많은 균열이 발견되는데 이 역시 온도가 낮아 Sn이 제대로 잘 녹지 않은 결과로 판단된다.

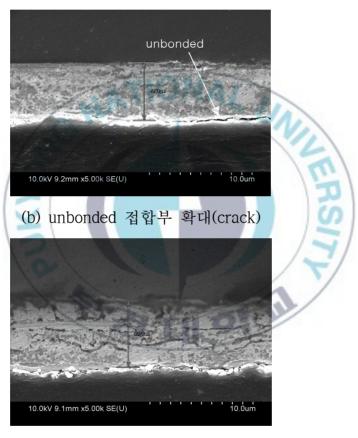

그림 3.30은 Au/Sn 합금 솔더를 사용하여 290℃에서 4,000N의 압력으로 1분간 본당한 샘플을 나타낸 것이다. 솔더 층이 녹은 상태는 양호하지만 Sn과 Au의 계면에 일부 unbonding 영역이 있고, 솔더 층내에 많은 kirkendall void가 관찰된다. 사진을 자세히 살펴보면 사진의 중앙 부분은 본당이 이루어 졌지만 그 양쪽은 본당이전혀 이루어지지 않았다. 이것은 먼저 접촉이 이루어진 일부에서 Sn과 Au의 합금 반응이 시작되면서 주변의 Sn과 Au를 소모하여Au/Sn 합금을 형성하는데 합금 조성의 융점이 290℃ 이상으로 되어 다시 굳어지는 freezing 현상으로 판단된다[16, 28 ~ 30].

(a) 접합부 단면

(b) unbonded 접합부 확대

그림 3.30. Au/Sn 합금솔더를 이용하여 본당한 접합부의 단면 Fig. 3.30. Cross-sectional view of bonded junction part using Au/Sn alloy solder

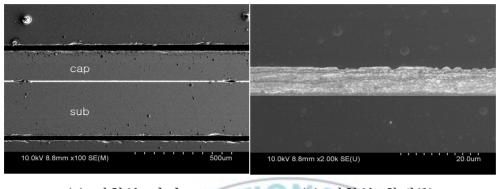

그림 3.31은 패키지 웨이퍼의 금속층 위에 다시 무전해 도금으로 Ni(1μm)/Au(4μm)를 형성한 시료를 285℃에서 5,000N의 압력으로 20분간 본당한 시료로서 비교적 양호한 접합상태를 보여주고 있다. 솔더 층과 패키지 웨이퍼 사이의 접합 계면이 뚜렷이 구분되

기는 하지만 계면에 큰 void나 크랙은 관찰되지 않고 있다. 본딩된 웨이퍼를 decap하여 내부를 관찰한 사진에서도 솔더가 밀봉 캐스 킷과 금속패드 위에 균일하게 잘 붙어 있음을 알 수 있다.

(a) 접합부 단면

(b) 접합부 확대(1)

(c) 접합부 확대(2) (d) debonding 접합부 평면 그림 3.31. 무전해 도금된 Au와 진공 증착된 Sn을 이용하여 본딩한 접합부의 단면

Fig. 3.31. Cross-sectional view of bonded junction part using electroless plating Au and deposited Sn

웨이퍼 본딩이 성공적으로 이루어진 웨이퍼는 패키지 웨이퍼의 후면을 절삭 연마하여 두께를 낮추게 된다. 패키지 웨이퍼의 두께

는 비아홀의 크기에 따라 결정되는데 약 70㎞에서 90㎞ 두께 범위 에서 제작하였다. 절삭 연마 과정이 끝나면 이 과정에서 발생한 유기 및 무기 오염을 제거하는 세정공정을 수행한 후에 비아홀 식 각을 위한 마스크를 형성한다. 비아홀은 실리콘의 이방성 습식식 각 공정을 이용하여 형성되므로 실리콘 질화막 혹은 실리콘 산화 막이 식각마스크로서 적합하다. 이때 본딩된 웨이퍼는 계면에 저 융점의 솔더물질이 있으므로 가능한 낮은 온도에서 식각마스크를 형성하는 것이 요구된다. 실험에서는 250℃에서 PECVD 방법으로 300nm의 실리콘 질화막을 형성하였다. 습식 식각에서는 본딩된 웨 이퍼 전체가 용액속에 들어가므로 기판 웨이퍼의 후면도 보호할 필요가 있다. 이를 위해서 같은 실리콘 질화막을 이용하거나 경우 에 따라서는 진공증착된 150nm 두께의 Cr을 이용한다. 식각마스크 공정이 완료되면 패키지 웨이퍼의 후면에 비아홀 식각 패턴을 형 성하게 된다. 이는 사진전사공정과 실리콘 질화막의 건식식각 공 정을 통해 이루어졌다. 비아홀 식각창이 형성되면 포토레지스트를 제거하고 85℃와 25%의 TMAH 수용액 중에서 실리콘 기판을 에칭 하여 비아홀을 형성하였다. 이때 식각 시간을 조절하여 비아홀의 바닥에 반대편의 금속패턴이 드러난 이후에 반대편의 금속층이 손 상되지 않도록 하였다. 경우에 따라서 비아홀 바닦에 실리콘을 일 부 남긴 상태에서 습식식각을 중지하고 남은 실리콘층을 건식식각 으로 제거하는 것도 가능하다.

그림 3.32는 패키지 웨이퍼의 후면에 형성된 비아홀의 사진을 나타낸 것이다.

(a) 비아 홀 평면 (b) 비아 홀 확대 그림 3.32. 패키지 웨이퍼 후면에 형성한 비아 홀 Fig. 3.32. Via hole formed in the back side of package wafer

비아홀의 형성이 끝나면 마지막으로 패키지 웨이퍼의 후면에 관통전극 및 와이어 본딩 패드를 위한 금속패턴을 형성하게 된다. 앞에서와 마찬가지로 사진전사공정과 전자빔 진공증착 및 리프트오프 방법을 통해 금속패턴을 형성하였다. 금속층의 구조는 Ti(100nm)/Ni(200nm)/Au(1,000nm)로 하였다. 이 금속층은 두꺼울수록 낮은 직류 및 고주파 저항을 가지므로 최상층인 Au 층의 두께는 1um에서 2um까지 변화시켜 특성을 분석하였다. 그림 3.33은비아홀 상부에 형성된 금속패턴을 나타낸 것이다.

그림 3.33. 패키지 웨이퍼의 비아 홀 상에 형성된 금속패턴 Fig. 3.33. Metal pattern formed on via hole of package wafer

## 제4장 동평면도파관 웨이퍼레벨 패키징

### 4.1. 동평면도파관 시뮬레이션 결과

CPW 패턴에 대한 시뮬레이션을 Advanced Design System의 Line Calk.를 이용하여 수행하였다. 먼저 CPW 패턴에 대한 각각의 요소인 전송선 패턴 폭(W), Ground plane과 전송선 간의 거리(G), 전송선의 길이(L), 동작주파수 및 기판의 유전율을 입력하여 ADS 계산기로 측정한 결과 최적의 패턴의 크기는 다음과 같이 계산되었다.

- 전송선 패턴 넓이(W) : 150um

- Ground Plane과 전송선과의 거리(G): 90um

- 전송선의 길이(L): 600um

그림 4.1. CPW 패턴 계산기

Fig. 4.1. CPW pattern calculator

계산된 패턴의 형태로 ADS에 CPW 회로와 측정 시 발생하는 외부 외란 요소를 적용한 등가회로를 그림 4.2와 같이 구성하였으며, 삽입손실을 확인하기 위해 S파라메터 시뮬레이션을 하였다.

(a) 직렬외란 요소 적용 등가회로

Fig. 4.2. CPW equivalent circuit with external disturbance

그림 4.3은 설계된 CPW이 입력 및 출력 임피던스 특성을 나타낸 것이다. CPW를 포함한 고주파 소자들은 반사손실을 줄이기 위해 입력 및 출력 임피던스를 50Ω이 되도록 설계한다. 그림 4.3으로부터 알 수 있듯이 입출력 임피던스가 50Ω으로 설계되었음을 확인 할 수 있다.

# (b) 출력 임피던스

그림 4.3. 설계된 CPW의 입력 및 출력 임피던스

Fig. 4.3. Input and output impedances of designed CPW

그림 4.4는 직렬외란 및 병렬외란 요소 등가회로에 대한 삽입손실을 나타낸 것이다. 삽입손실이 동작주파수에서 작으면 작을수록임피던스 정합이 잘 이루어져 있음을 증명한다. 그림 4.4로부터 알수 있듯이 2GHz의 동작주파수에서 매우 작은 삽입손실 특성을 보였다.

(b) 병렬외란요소 등가회로의 삽입손실 그림 4.4. 2GHz 대역에서의 삽입손실 시뮬레이션 결과

Fig. 4.4. Simulation results of insertion loss in 2GHz band

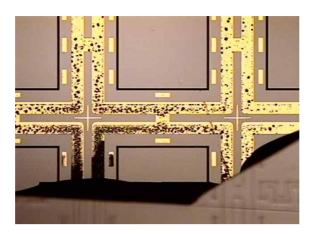

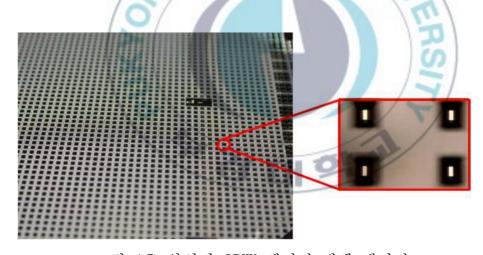

#### 4.2. 동평면도파관 웨이퍼 레벨 패키징 공정

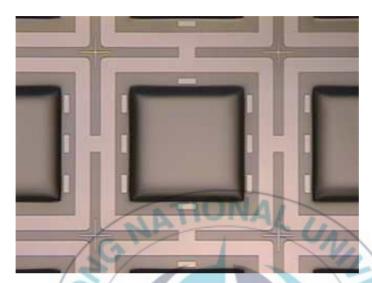

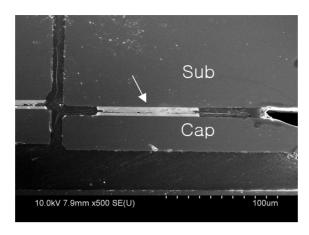

CPW웨이퍼 레벨 패키징은 그림 3.17에서 제안된 공정으로 진행하였다. 패키지 웨이퍼와 CPW 웨이퍼는 각각에 미리 형성된 본딩용 패턴으로 서로 정렬하였고, 그 상태에서 Au/Sn 솔더를 285℃에서 5,000N의 압력으로 20분간 본딩함으로써 두 웨이퍼간의 접합을 완성하였다. 그림 4.5의 왼쪽 사진은 완성된 웨이퍼레벨 패키징을 나타내고, 오른쪽 사진은 상층부를 확대한 것으로 패키지 웨이퍼와 CPW 웨이퍼의 금속 배선이 비아를 통해 잘 연결되어 있음을 확인할 수 있다.

완성된 패키지는 절단과정을 통하여 개별 칩으로 분리 되었고, 각각의 칩들에 대하여 기계적 특성 및 전기적 특성을 평가 하였다.

그림 4.5. 완성된 CPW 웨이퍼 레벨 패키징 Fig. 4.5. Completed CPW wafer level package

#### 4.3. 실험 및 고찰

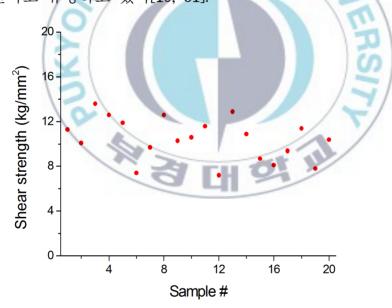

WLP의 가장 중요한 기계적 특성은 본당 후의 접합강도 및 패키지 누설특성이다. 접합된 패키지의 접합강도를 측정하기 위하여전단응력 시험장비인 Dage-4000을 이용하여 임의로 추출된 20개의 절단된 칩의 특성을 분석하였다. 전단응력의 측정을 위하여 측정 프로브의 끝단은 접합된 계면에서 100um 높이에 고정하였고, 프로브의 이동속도는 초당 500um로 설정하였다.

그림 4.6은 제작된 WLP의 전단응력을 나타낸 것이다. 전단응력은 평균  $11.725\pm1.30kg/mm^2$ 으로서 매우 양호한 결과를 얻을 수있었다. MIL-STD-883F 규격에 따르면  $5\times10^{-4}inch^2(0.32mm^2)$ 이하의 적은 패키지의 경우 최소한  $0.04kg/10^{-4}inch^2$ 의 응력을 견딜 수있어야 한다고 규정하고 있다[16, 31].

그림 4.6. 제작된 WLP의 전단응력 측정 결과 Fig. 4.6. Shear strength result of WLP

따라서 본 연구에서 형성한 접합의 전체 면적은 0.315mm<sup>2</sup>이므로 규격을 상회하는 우수한 접합강도를 가지고 있다고 할 수 있다.

다음으로 열충격, 항온항습 및 고온고습 시험 후에 접합강도의 변화를 측정하여 그림 4.7에 나타내었으며 이때 각각의 시험조건 은 아래와 같다.

- 열충격 시험 : IPC-TM-650, -55~125℃ (30분/회, 저온 15분, 고온 15분), 1,000회(21일)

- 항온항습 시험 : J-STD-3284 85℃, 85Rh 1000시간(42일)

- 고온방치 시험 : 150℃/500시간(21일)

그림 4.7과 같이 열충격 시험 후에 접합강도는 평균 9.0kg/mm² 으로 감소하였고, 항온항습 시험 후에는 평균 10.4kg/mm², 그리고 고온방치 시험 후에는 평균 10.0 kg/mm²으로 접합강도가 감소하였다. 열충격 시험 후에 가장 큰 접합강도의 저하가 나타났는데 이는 실리콘 웨이퍼와 Au/Sn 솔더, Ti/Ni/Au 등의 열팽창계수가 서로 다르기 때문에 이들의 계면에서 열화가 발생하는 것으로 판단된다.

그림 4.7. 환경시험에 따른 WLP의 접합강도

Fig. 4.7. Junction strength of WLP by environmental test

접합된 패키지의 밀봉특성 또는 누설특성을 평가하기 위해 MIL-STD- 884.1014 규격을 기준으로 헬륨 bombing과 누설감지 특성을 분석하였다[16, 32].헬륨 bombing 테스트는 내부에 공동을 가진 작고 사전에 밀봉된 부품의 누설 시험법으로 개념도를 그림 4.8에 나타내었다. CPW WLP용 패키지 칩은 공동과 기판 및 패키지 칩 사이의 간격에 의해 형성된 공간은 약 1.4×10<sup>-2</sup>mm³으로서 매우 미소하다. 이러한 미소 체적에 대한 누설 시험은 그 자체로서 쉽지 않다. 본 연구에서는 이를 보완하기 위해서 본딩된 4인치웨이퍼를 4등분하고 그 전체를 대상으로 누설 시험을 수행하였다. 압력 챔버에 넣은 다음 칩 외부의 오염물질에 대한 영향을 최소화하기 위해서 헬륨을 일정기간 흘렸다. 그 다음 챔버의 압력을 5기압으로 증가시켜 6시간 동안 상온에서 방치하였다. 그 후 시료를 꺼내 질량분석기를 이용하여 헬륨의 누설량을 5분 단위로 측정하였다.

그림 4.9는 5분간격으로 60분까지 누설특성을 측정한 결과를 나

타낸 것이다. 초기 누설율은 약  $10^{-4}$  atm.cc/sec이며, 약 10분 후에는  $1.2 \times 10^{-5}$  atm.cc/sec이하의 누설율을 나타내는 안정상태에 도달하였다. 헬륨누설시험 데이터는 칩 한 개로부터 측정된 것이 아니라 4조각으로 분리된 4인치 웨이퍼 전체를 측정한 것이므로 한 웨이퍼에 칩이 5,000개 이상 들어가는 것을 감안하면 칩 당 누설율은 대략  $1 \times 10^{-8}$  atm.cc/sec 이하라고 할 수 있다.

그림 4.9. 4조각의 4인치 웨이퍼에서 측정된 헬륨 누설량 Fig. 4.9. Measured leak rate in 4 pieces and 4inches wafer

고주파 소자의 성능 또는 특성을 파악하기 위해 주로 삽입손실 측정이 사용된다[13, 16]. 본 연구에서는 제작된 패키지의 고주파 특성을 측정하기 위하여 실제의 고주파 수동소자대신에 더미 웨이퍼에 형성된 CPW 패턴을 사용하였다. 패키지의 삽입손실을 측정하기 위하여 절단된 웨이퍼로부터 임의로 20개의 시료를 선별하였다. 측정에는 HP 8510C vector network analyzer probe station을 사용하였다. 주파수를 0.5 ~ 3.5GHz까지 변화시키면서 주파수에 따른 삽입손실의 분포를 측정하였다. 그림 4.10은 삽입손실(S12)의 분포도를 측정한 결과이다. 측정된 구간에서 주파수에 따라 완만하게 삽입손실이 증가하는 정상적인 패턴을 나타내고 있다. 측정주파수를 0.5 ~ 3.5GHz로 제한한 것은 사용목적이 휴대폰용 고주파수동 부품, 그 중에서도 CPW 소자를 대상으로 하는 것이므로 이들 소자의 사용범위를 고려한 것이다.

그림 4.10. 주파수에 따른 접합된 WLP 칩의 삽입손실 Fig. 4.10. Insertion loss of WLP chip as a function of frequency

표 4.1은 측정주파수 2GHz에서의 삽입손실 값을 나타낸 것이다. 평균 삽입손실은 -0.048dB로서 CPW 패턴 자체의 삽입손실(약 0.02dB)을 고려하면 패키지 자체의 삽입손실은 매우 미미하다고 할 수 있다.

표 4.1. 2GHz에서 측정된 WLP 칩의 삽입손실 Table 4.1. Insertion loss of WLP chip measured at 2GHz

| 시료   | 삽입손실 [dB] |

|------|-----------|

| 1    | -0.057    |

| 2    | -0.043    |

| 3    | -0.051    |

| 4    | -0.053    |

| 5    | -0.056    |

| 6    | -0.055    |

| 7/   | -0.053    |

| 8    | -0.052    |

| /9   | -0.039    |

| 10   | -0.039    |

| 11   | -0.046    |

| 12   | -0.065    |

| 13   | -0.036    |

| 14   | -0.036    |

| 15   | -0.035    |

| 16   | -0.035    |

| 17   | -0.050    |

| 18   | -0.053    |

| 19   | -0.054    |

| 20   | -0.054    |

| 평균   | -0.048    |

| 표준편차 | 0.008     |

제작된 패키지의 신뢰성을 평가하기 위하여 PCT시험 (pressure cooker test, PCT)을 수행하였다. 시험에 사용된 시료는 웨이퍼로부터 임의로 추출된 20개의 접합된 패키지 칩을 사용하였다. 시험조건은 120℃와 100% RH@2atm에서 48시간 동안 진행하였다. 비아홀 내부의 금속막을 현미경으로 관찰한 결과 관찰 가능한 손상및 변질이 관찰되지 않았다. 현미경 검사는 미세한 누설을 감지할수 없을 뿐 아니라 내부의 상태를 관찰할 수 없으므로 간접적인 방법으로 고주파 삽입손실을 측정함으로서 PCT 시험후 내부의 변질 여부를 판단하고자 하였다. 그림 4.11은 PCT 시험 이후에 측정된 패키지의 주파수에 따른 삽입손실의 분포도를 나타낸 것이다.

그림 4.11. 환경시험 후 주파수에 따른 WLP 칩의 삽입손실 Fig. 4.11. Insertion loss of WLP chip as a function of frequency after environmental test

분포도는 절대 값이 약간 상승한 것 이외에는 PCT 시험전과 거의 동일한 특성을 나타내고 있다. 여기서 2GHz에서의 삽입손실 값의 평균은 -0.063dB로서 PCT 시험 이전의 평균 삽입손실인 -0.048보다 약 30% 증가하였다. 그러나 아직 절대값이 매우 낮은 상태를 유지하고 있으므로 PCT 시험과정에서 누설과 침투 현상은 발생하지 않은 것으로 판단된다.

## 제5장 결론

본 논문에서는 새로운 형태의 식각방법과 본딩방법을 이용하여 수율이 높고 제작비용을 절감할 수 있는 새로운 형태의 박막형 고 주파 소자를 위한 웨이퍼 레벨 패키징을 구현하였다.

고주파 소자용 기존 패키지는 소자 웨이퍼와 패키징 웨이퍼를 DRIE 방법등으로 관통 홀을 형성한 후 형성된 관통 홀에 전기도 금을 이용하여 구리등 전도성 물질을 채워서 외부로 전극을 연결하는 방법이 사용되어왔으나, DRIE 공정이 고가이며, 구리등 전도체를 미세한 관통 홀에 채우는 과정에서 void 등의 불량이 많아수율이 낮고, 공정비용이 바싼 단점이 있다.

제안된 방법은 패키지 웨이퍼를 제작하기 위하여 기존에 이용되던 DRIE와 도금 등의 고가의 공정을 배제하고 이방성 습식식각, 금속증착 등 저가의 일반적이고 안정화된 마이크로머시닝 공정기술을 이용하여 관통 홀을 형성하였다.

패키지의 밀봉특성을 평가하기 위하여 실제 박막형 고주파 소자 대신에 CPW 소자를 제작하였다. 또한, 금(Au)과 주석(Sn)의 합금을 이용하여 제작한 패키지 웨이퍼와 더미 웨이퍼를 본당하여 WLP를 완성하였다. 완성된 WLP를 절단하여 개별의 칩으로 분리한 후 칩의 전단응역(shear strength) 및 누설률(leak rate)을 평가하였다.

본딩된 웨이퍼를 개별 칩으로 절단한 후에 칩의 접합강도를 측정하기 위하여 20개의 칩을 추출하여 Military standard 883F (MIL-STD-883F) 규격을 기준으로 실험하였다.

측정된 결과는 평균 전단응력  $10.425kg/mm^2$ 이었으며, 표준편차는  $1.89kg/mm^2$ 으로 양호한 결과를 보였다. 그러나 실험샘플 중 접

합강도의 편차가 큰 경우가 있는데, 이는 패키지 웨이퍼가 트랜치 및 관통 홀을 가지고 있고 솔더 재료와 실리콘과의 열팽창계수 차이에 의하여 본딩 공정에서 패키지 웨이퍼가 약간 휘어지는 것으로 판단되며 차후 연구에서 이러한 문제를 해결하기 위한 실험을 진행할 계획이다.

접합된 패키지의 밀봉 특성평가를 위해 헬륨 bombing과 누설특성 평가를 실시하였다. 전체샘플을 압력챔버에 실장한 후, 일정한 압력, 일정한 시간동안 헬륨가스를 주입하였다. 그 후 시료를 꺼내 질량분석이 가능한 압력챔버내에서 시료로부터 방출되는 헬륨의 누설량을 측정하였다. 초기 누설률은 약  $10^{-4}atm.cc/sec$ 였으며 10분 후  $1.2\times10^{-5}atm.cc/sec$  이하의 누설률로 안정상태에 도달하였다. 이는  $4.94\times10^{-8}atm.cc/sec$ 이하의 누설률을 규정하는 MIL-STD-883F를 만족하는 수치이다.

실제 공정을 통해 웨이퍼 레벨 패키징을 구현하였고, Network analyzer를 이용하여 삽입손실을 측정한 결과 2GHz 대역에서 약 -0.048dB로서 CPW 소자 자체의 삽입손일 0.02dB를 제외하면 미미한 삽입손실을 보임을 확인하였다. 또한 환경시험후의 삽입손실을 측정한 결과 -0.063dB로서 다소 증가하였으나 기존의 실리콘 기판관통 연결구조를 이용한 고주파 MEMS 소자의 패키징 구조들과 비교하였을 때 우수한 특성을 보인다고 할 수 있다.

제작된 WLP 칩의 사이즈는  $1.04 \times 1.04 \times 0.4mm^3$ 였고, 우수한 기계적 특성을 보였다. 평균 전단응력은  $10.425kg/mm^2$ 을 보였고, 접합된 웨이퍼 전체의 누설률은  $1.2 \times 10^{-5} atm.cc/sec$  이하였다. 제안된 WLP의 구조 및 공정은 저가 및 양산성을 확보할 수 있는 기술이므로 박막형 고주파 소자의 패키지로 적합하다고 판단된다.

#### 참고문헌

- [1] 황근철, "저온 동시 소결 세라믹 기판(LTCC)을 이용한 RF MEMS 소자의 실장법에 대한 연구," 서울대학교 대학원, 2003.

- [2] 윤민승, "TSV (Through Silicon Via) 기술동향" Journal of the Microelectronics and Packaging Society, vol. 16, no. 1, pp. 1-6, 2009.

- [3] J. Baborowskia, A. Pezousa, G. S. Durantea, R. J. Jamesb, R. Ziltenerc, C. Mullera, and M. A. Duboisa, "Wafer level packaging technology for silicon resonators" Procedia Chemistry, vol. 1, pp. 1535–1538, 2009.

- [4] "Integrated Circuit Manufacturing: A Technology Resource" in Integrated Circuit Packaging, Assembly and Interconnections, ed: Springer US, pp. 15–29, 2007.

- [5] R. Chanchani, C. D. Nordquist, R. H. Olsson, T. Peterson, R. Shul, C. Ahlers, T.A. Plut, and G.A.Patrizi, "A new wafer-level packaging technology for MEMS with hermetic micro-environment" IEEE international conference on Electronic Components and Technology, pp. 1604-1609, 2011.

- [6] S. Seok, M. Fryziel, N. Rolland and P.-A. Rolland, "Enhancement of bonding strength of packaging based on BCB bonding for RF devices" Microsystem Technologies, vol. 18, pp. 2035–2039, 2012.

- [7] Y. S. Bang, J. M. Kim, J. M Kim, Y. K. Kim and Y. H. Jang, "LTCC-based vertical via interconnects for RF MEMS packaging" Microwave and Optical Technology Letters, vol. 52, pp. 252–257, 2010.

- [8] A. Polyakow, P. M. Mendes, S, M. sinaga, M. Bartek, B. rejaci, J. H. Correia and J. N. Burghartz, "Processability and electrical characteristics of glass substrates for RF wafer-level chip-scale packages" 2003 Electronic Components and Technology Conference, pp. 875-880, 2003.

- [9] 이주용, "유리 기판 관통 비아구조를 갖는 웨이퍼 단위 RF-MEMS 패키징에 대한 연구," 단국대학교 대학원, 2013.

- [10] C. W. Lin, H. A. Yang, W. C. Wang, and W. Fang, "Implementation of three-dimensional SOI-MEMS wafer-level packaging using through-wafer interconnections" Journal of Micromechanics and Microengineering, vol. 17, no. 6, pp. 1200–1205, 2007.

- [11] M. Esashi, "Wafer level packaging of MEMS" Journal of Micromechanics and Microengineering, vol. 18, no. 7, pp. 1–13, 2008.

- [12] Q. C. Zaho, Z. C. Yang, Z. Y. Guo, H. T. Ding, M. Li, and G. Z. Yan, "Wafer-level vacuum packaging with lateral interconnections and vertical feedthroughs for microelectromechanical system gyroscopes" Journal of Micro/Nanolithography, MEMS, and MOEMS, vol. 10, no. 1, pp. 1-5, 2011.

- [13] J. H. Lim, J. Y. Ryu, H. J. Choi and W. C. Choi, "Design and fabrication of a low-cost wafer-level packaging for RF devices" Transactions on Electrical and Materials, vol 15, no. 2, pp. 91-95, 2014.

- [14] G. Murillo, Z. J. Davis, S. Keller, G. Abadal, J. Agusti, A. Cagliani, N. Noeth, A. Boisen, and N. Barniol, "Novel SU-8 based vacuum wafer-level packaging for MEMS devices" Microelectronic Engineering, vol. 87, pp. 1173-1176, 2010.

- [15] S. Tanaka et al., "Wafer-level hermatic packaging technology for MEMS using anodically-bondable LTCC wafer" IEEE international conference on MEMS, pp. 376-379, 2011.

- [16] W. C. Choi and H. J. Choi, "Development of a 3-D Process Technology for Wafer-Level Packaging of MEMS Devices" IEEE Transactions on Components, Packaging and Manufacturing Technology, vol 2, no. 9, pp. 1442-1448, 2012.

- [17] D. S. Tezcan, N. Pham, B. Majeed, P. D. Moor, W. Ruythooren and K. Baert, "Sloped through wafer vias for 3D wafer level packaging" IEEE international conference on Electronic Components and Technology, pp. 643-647, 2007.

- [18] R. Varia and X. Fan, "Reliability enhancement of wafer level packages with nano-column-like hollow solder ball structures" IEEE international conference on Electronic Components and Technology, pp. 754–760, 2011.

- [19] H. Y. Son, C. K. Chung, M. J. Yim, J. S. Hwang, K. W. Park, G. J. Jung and J. K. Lee, "Wafer-level flip chip packages using pre-applied anisotropic conductive films (ACFS)" IEEE Transactions on Electronics Packaging Manufacturing, vol. 30, no. 3, pp. 221-227, 2007.

- [20] V. Kripesh, V. S. Rao, A. Kumar, G. Sharma, K. C. Houe, Z. Xiaowu, K. Y. Mong, N. Khan and J. Lau, "Design and development of a multi-die embedded micro wafer level package" IEEE international conference on Electronic Components and Technology, pp. 1544-1549, 2008.

- [21] K. Wang, M. Frank, P. Bradley, R. Ruby, W. Mueller, A. Barfknecht and M. Gat, "FBAR Rx filters for handset front-end modules with wafer-level packaging" IEEE symposium on Ultrasonics, pp. 162-165, 2003.

- [22] C. H. Lin, J. M. Lu and W. Fang, "Encapsulation of film bulk acoustic resonator filters using a wafer-level microcap array" Journal of Micromechanics and Microengineering, vol. 15, no. 8, pp. 1433–1438, 2005.

- [23] C. A. Yuan and K. N. Chiang, "Micro to macro thermo-mechanical simulation of wafer level packaging" T. ASME, vol. 125, pp. 567-581, 2003.

- [24] J. Tian, J. Iannacci, S. sosin, R. Gaddi and M. Bartek, "RF-MEMS wafer-level packaging using through-wafer via technology" IEEE international conference on Electronic Components and Technology, pp. 441-447, 2006.

- [25] B. Lee, S. Seok and K. Chun, "A study on wafer level vacuum packaging for MEMS devices" Journal of Micromechanics and Microengineering, vol. 13, pp. 663–669, 2003.

- [26] S. Kühne and C. Hierold, "Wafer-level packaging and direct interconnection technology based on hybrid bonding and through silicon vias" Journal of Micromechanics and Microengineering, vol. 21, no. 8, pp. 1–7, 2011.

- [27] "Status of the MEMS industry" Yole Development, pp. 129–169, 2009.

- [28] J. W. Yoon, H. S. Chun, and S. B. Jung, "Reliability analysis of Au-Sn flip-chip solder bump fabricated by co-electroplating" Journal of Materials Research Society, vol. 22, no. 5, pp. 1219–1229, 2007.

- [29] D. Saias, P. Robert, S. Boret, c. Billard, G. Bouche, D. Belot and P. Ancey, "An above IC MEMS RF switch" IEEE Journal of Solid-State Circuits, vol. 38, no. 12, pp. 2318-2324, 2003.

- [30] H. Y. Son, C. K. Chung, M. J. Yim and K. W. Paik, "Wafer level package using pre-applied anisotropic conductive films (ACFs) for flip-chip interconnections" Proceeding of Electronic Components and Technology Conference, 2007.

- [31] C. W. Lin, C. P. Hsu, H. A. Yang, W. C. Wang and W. Fang, "Implementation of silicon-on-glass MEMS devices with embedded through-wafer silicon vias using the glass reflow process for wafer-level packaging and 3D chip integration" Journal of Micromechanics and Microengineering, vol. 18, no. 2, pp. 1-6, 2008.

- [32] J. Liu, Q. A, Huang, J. Shang, J. Song and J. Tang, "Micromachining of pyrex7740 glass and their applications to wafer-level hermetic packaging of MEMS devices" IEEE international conference on MEMS, pp. 469-499, 2010.