Dissertation for the Degree of Doctor of Philosophy

# Low-Power High-Linearity CMOS Radio

## Frequency Receiver Frontend for 24GHz

## Automotive Collision Avoidance Radar

by

Habibollah Rastegar

Department of Information and Communications Engineering

The Graduate School

Pukyong National University

February 2017

a

# Low-Power High-Linearity CMOS Radio Frequency Receiver Frontend for 24GHz Automotive Collision Avoidance Radar 24GHz 차량 충돌방지 저전력 고선형 CMOS 고주파 수신기 전단부

Advisor: Prof. Jee-Youl Ryu

by

Habibollah Rastegar

A dissertation submitted in partial fulfillment of the requirements for the

degree of

Doctor of Philosophy

in Department of Information and Communications Engineering,

The Graduate School,

Pukyong National University

February, 2017

b

# Low-Power High-Linearity CMOS Radio Frequency Receiver Frontend for 24GHz Automotive Collision Avoidance Radar

A dissertation by Habibollah Rastegar

Approved by:

Professor Deock-Ho Ha, (Chairman)

er

Professor Hyek-Hwan Choi, (Member)

Professor Kyu-Chil Park, (Member)

2

Dr. Sung-Woo Kim, (Member)

Professor Jee-Youl Ryu, (Member)

February, 2017

### **Table of Contents**

| L | ist of l                                                                             | Figu        | res                                          | v    |  |

|---|--------------------------------------------------------------------------------------|-------------|----------------------------------------------|------|--|

| L | ist of ]                                                                             | Fabl        | e                                            | x    |  |

| A | cknow                                                                                | vledg       | gement                                       | xi   |  |

| A | bstrac                                                                               | et          |                                              | xiii |  |

| 1 | In                                                                                   | ntroduction |                                              |      |  |

|   | 1.1                                                                                  | Mo          | tivation                                     | 1    |  |

|   | 1.2                                                                                  | Pro         | posed Receiver Frontend Architecture         | 2    |  |

|   | 1.3                                                                                  |             | jective                                      |      |  |

|   | 1.4                                                                                  |             | erview                                       |      |  |

| 2 | De                                                                                   |             | g of Low Noise Amplifier                     |      |  |

|   | <ul> <li>2.1 Background</li> <li>2.2 S-parameters</li> <li>2.3 Power Gain</li> </ul> |             |                                              |      |  |

|   |                                                                                      |             |                                              |      |  |

|   |                                                                                      |             | 17                                           |      |  |

|   | 2.4                                                                                  | Sta         | ability Factor                               |      |  |

|   | 2.5                                                                                  | Mo          | dulation Scheme                              |      |  |

|   | 2.5                                                                                  | 5.1         | Noise Sources                                |      |  |

|   |                                                                                      | 5.2         | Noise Figure                                 |      |  |

|   |                                                                                      | 5.3         | Output Noise of the First Stage              |      |  |

|   | 2.5                                                                                  | 5.4         | Sensitivity                                  |      |  |

|   | 2.6                                                                                  | Lin         | earity                                       |      |  |

|   | 2.6                                                                                  | 5.1         | 1-dB Compression Point                       |      |  |

|   | 2.6                                                                                  | 5.2         | Third-order Input Intecept Point (IIP3)      |      |  |

|   | 2.6                                                                                  | 5.3         | Linearity Consideration of the Systsem Level |      |  |

i

|   | 2.7 Inp | out Impedance Matching Network                          | 40 |

|---|---------|---------------------------------------------------------|----|

|   | 2.8 De  | sign Considerations and Analysis                        | 41 |

|   | 2.8.1   | LNA Descriptioin                                        | 41 |

|   | 2.8.2   | LNA Design                                              | 44 |

|   | 2       | .8.2.1 Fundamental                                      | 44 |

|   | 2       | .8.2.2 Nonlinear Base Capacitance in Bipolar Transistor | 47 |

|   | 2       | .8.2.3 Phase Adjustment by Feedback Capacitance         | 49 |

|   | 2.8.3   | Design Consideratioins                                  | 50 |

|   | 2.8.4   | Implementation                                          | 51 |

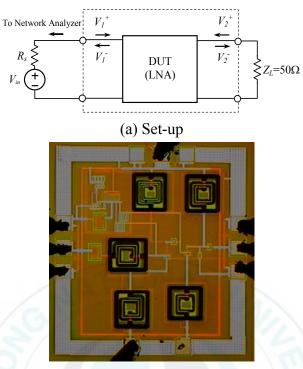

|   | 2.8.5   | Measurement set-up                                      |    |

|   | 2.8.6   | Experimental Validation                                 | 56 |

|   | 2.9 Me  | easurement Results                                      | 57 |

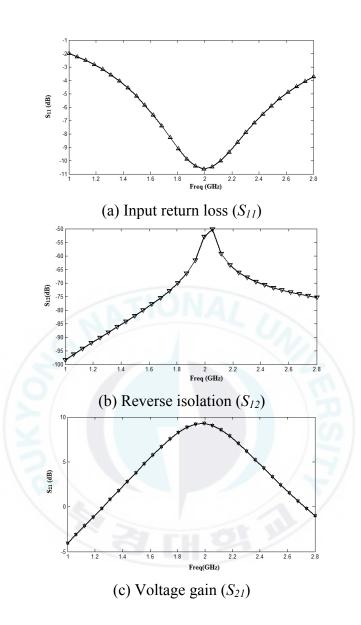

|   | 2.9.1   | S-parameters and Noise Figure Measurement               |    |

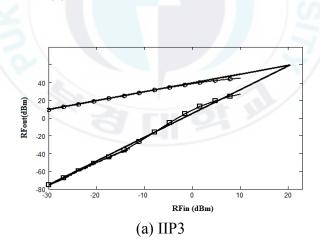

|   | 2.9.2   | IIP3 and Satbility Factor                               |    |

|   | 2.10 Su | mmary                                                   | 64 |

| 3 |         | n of Low Power and Low Voltage Mixer                    |    |

|   |         | ckground                                                |    |

|   |         | gh Linearity Techniques                                 |    |

|   | 3.3 Mi  | xer Fundamentals                                        | 70 |

|   | 3.4 Ma  | ain Characteristics of Mixers                           | 72 |

|   | 3.4.1   | Conversoin Gain                                         | 72 |

|   | 3.4.2   | Local Oscillator Power                                  | 73 |

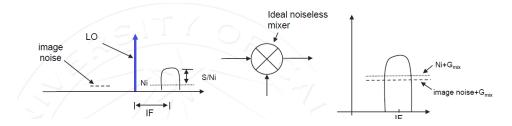

|   | 3.4.3   | Noise Figure                                            | 74 |

|   | 3.4.4   | Port to Port Isolation                                  | 76 |

|   | 3.5 Ac  | tive Mixer Architecture                                 | 72 |

ii

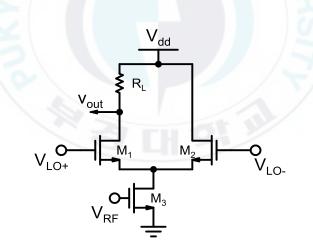

| 3.  | 5.1          | Unbalanced Mixer                              | 77  |

|-----|--------------|-----------------------------------------------|-----|

| 3.  | 5.2          | Single-balanced Mixer                         | 79  |

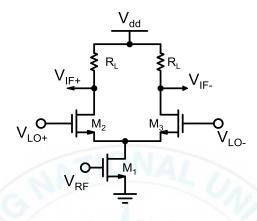

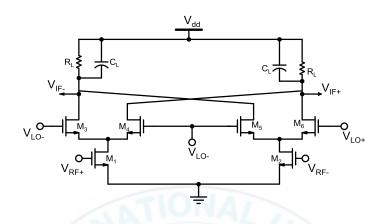

| 3.  | 5.3          | Double-Balanced Mixer                         | 81  |

| 3.6 | Des          | sign Consideratonis and Analysis              | 83  |

| 3.  | 6.1          | Mixer Description                             | 83  |

| 3.  | 6.2          | Mixer Analysis                                | 84  |

| 3.  | 6.3          | Results and Disscussions                      | 88  |

| 3.7 | Sur          | nmary                                         | 93  |

| 4 D | esign        | of Voltage-Controlled Oscillator              | 94  |

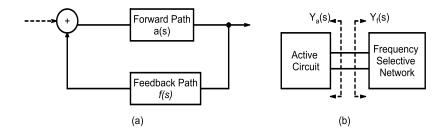

| 4.1 |              | ckground                                      |     |

| 4.2 |              | rt-up Considerations                          |     |

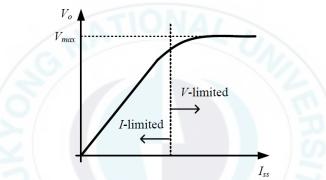

| 4.3 | Ste          | ady-state Considerations                      | 101 |

| 4.4 | Pha          | ase Noise in LC Oscillators                   | 103 |

| 4.  | 4.1          | Linear Time-Invariant Phase Noise Analysis    | 103 |

|     | 4.2<br>nalys | Linear Periodically Time-Varying (LPVT) Phase |     |

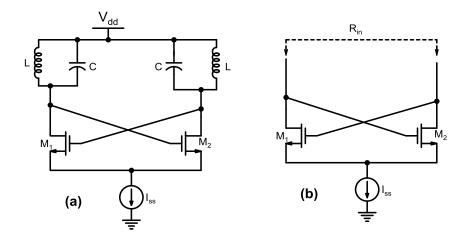

| 4.5 | LC           | VCO Topologies                                | 108 |

| 4.  | 5.1          | Single Cross-Coupled LC VCO Topology          | 109 |

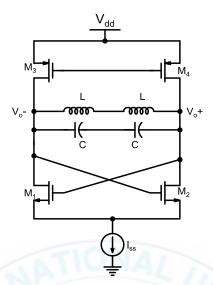

| 4.  | 5.2          | Complementary Cross-Coupled LC VCO Topology   | 111 |

| 4.6 | Des          | sign Trade-offs                               | 113 |

| 4.7 | VC           | O Description                                 | 116 |

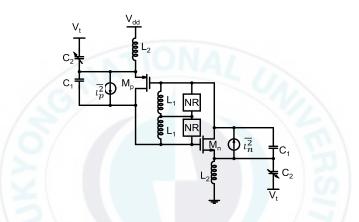

| 4.8 | Pro          | posed Current-reuse LC VCO                    | 119 |

| 4.  | 8.1          | Start-up Considerations                       | 120 |

| 4.  | 8.2          | Analysis of Output Voltage Swings             | 124 |

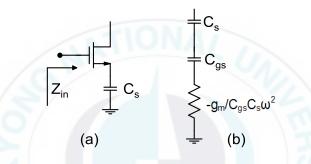

| 4.  | 8.3          | Frequency-Dependent Negative Resistance       | 128 |

## iii

|    | 4.8     | .4 Phase Noise Analysis                               | 131   |

|----|---------|-------------------------------------------------------|-------|

| 2  | 4.9     | Results and Discussions                               | 133   |

| 4  | 4.10    | Summary                                               | 139   |

| 5  | An      | Integarated High Linearity CMOS Receiver Frontend for | · 24- |

| GI | Hz Ap   | plicatoins                                            | 140   |

| 4  | 5.1     | Background                                            | 140   |

| 4  | 5.2     | Proposed Receiver Frontend Architecture               | . 141 |

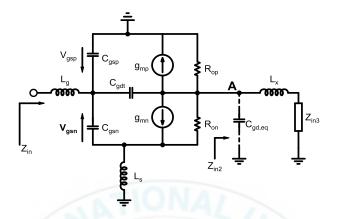

| -  | 5.3     | Design and Analysis of CMOS Circuit Blocks            | 144   |

|    | 5.3     | .1 LNA                                                | 144   |

|    | 5.3     |                                                       |       |

|    | 5.3     | 1                                                     |       |

|    | 5.3     |                                                       |       |

|    | 5.4     | Results and Discussions                               |       |

| -  | 5.5     | Summary                                               | 170   |

| 6  | Co      | nclusion                                              |       |

| (  | 6.1     | Conclusions                                           |       |

|    | 6.2     | Future Works                                          |       |

|    |         | ces                                                   |       |

| Li | st of I | Publications                                          | . 191 |

## iv

## List of Figure

| Figure 1.1: Proposed 24 GHz receiver frontend                                            | 5    |

|------------------------------------------------------------------------------------------|------|

| Figure 2.1: Two-port network for incident wavers $(a_1 \text{ and } a_2)$ and reflective | cted |

| waves (b <sub>1</sub> , b <sub>2</sub> ) used in S-parameters defenitions                | . 15 |

| Figure 2.2: Block diagram of single-stage RF amplifier                                   | . 18 |

| Figure 2.3: MOS model of two-port network for noise calculations                         | . 28 |

| Figure 2.4: Small signal model of a cascode topology with inductiv                       | vely |

| degenerated noise sources                                                                | . 33 |

| Figure 2.5: 1-dB compression point                                                       | . 36 |

| Figure 2.6: (a) Signal spectrum of a nonlinear system and (b) IIP3 concep                | tual |

| interpretation                                                                           | . 38 |

| Figure 2.7: Schematic of proposed LNA                                                    | . 47 |

| Figure 2.8: Rejection of Second-order and higher-order harmonics of t                    | t he |

| output power by using LC tank                                                            | . 48 |

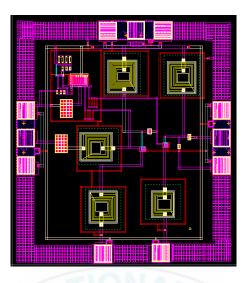

| Figure 2.9: Layout of the 2GHz LNA                                                       | . 53 |

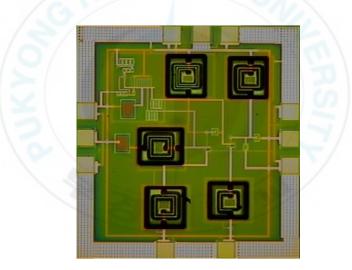

| Figure 2.10: Chip micrograph of the 2GH LNA                                              | . 53 |

| Figure 2. 11: S-parameters measurement set-up                                            | . 54 |

| Figure 2.12: On-chip measurement                                                         | . 55 |

v

| Figure 2.13: Measurement set-up for S-parameter of LNA                    | . 57 |  |  |

|---------------------------------------------------------------------------|------|--|--|

| Figure 2.14: S-parameter and noise figure of the LNA                      | . 60 |  |  |

| Figure 2.15: IIP3 and stability factor of the LNA                         | . 62 |  |  |

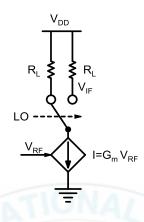

| Figure 3.1: Conceptual idea of active mixer                               | . 66 |  |  |

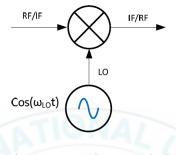

| Figure 3.2: Mixer symbol                                                  | . 71 |  |  |

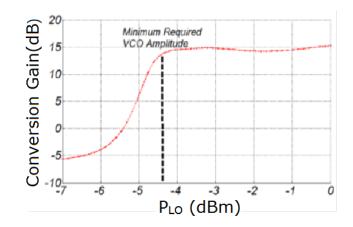

| Figure 3.3: Conversion gain versus amplitude of LO                        | . 74 |  |  |

| Figure 3.4: Noise sources in mixer                                        | . 75 |  |  |

| Figure 3.5: Different port to port leakagesin Mixer                       |      |  |  |

| Figure 3.6: Unbalanced mixer schematic                                    |      |  |  |

| Figure 3.7: Single-balanced mixer schematic                               |      |  |  |

| Figure 3.8: Doble-balanced mixer schematic                                | . 82 |  |  |

| Figure 3.9: (a) Conventional mixer with two stages and (b) proposed mixer |      |  |  |

| using folded architecture                                                 | 86   |  |  |

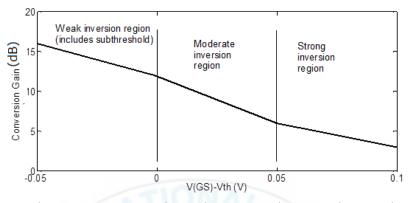

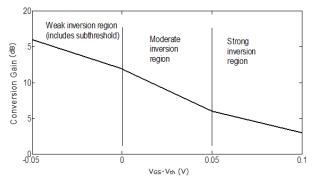

| Figure 3.10: Conversion gain versus mixer transistor regions              | . 88 |  |  |

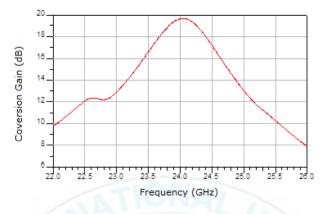

| Figure 3.11: Conversion gain versus frequency                             | . 89 |  |  |

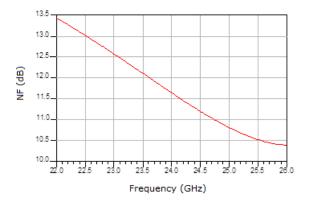

| Figure 3.12: Noise figure versus frequency                                | . 90 |  |  |

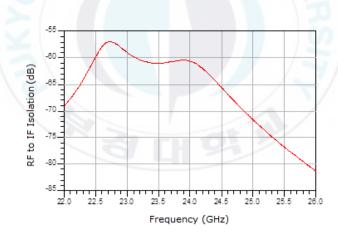

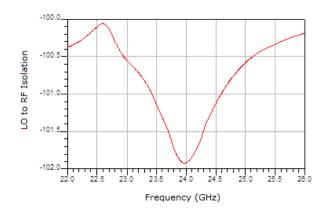

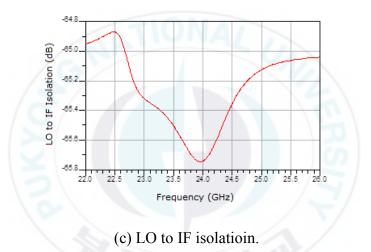

| Figure 3.13: Different port to port isolation versus frequency            | . 91 |  |  |

| Figure 3.14: Conversion gain versus low power                             | . 92 |  |  |

| Figure 4.1: (a) Feedback model (b) Negative resistance model              | . 97 |  |  |

vi

| Figure 4.2: Small signal LC oscillator model                                |

|-----------------------------------------------------------------------------|

| Figure 4.3: (a) Magnitudes, and (b) root lucas of transfer function for     |

| different values of loop gain                                               |

| Figure 4.4: Start-up requiremnts of cross-coupled LC VCO 101                |

| Figure 4.5: (a) Root locus of LC oscillator and (b) LC oscillator output    |

| waveform                                                                    |

| Figure 4.6: Noise sources in LC VCO schematic 103                           |

| Figure 4.7: Single cross-coupled LC VCO 110                                 |

| Figure 4.8: Complementary cross-coupled LC VCO 113                          |

| Figure 4.9: Voltage amplitude versus Iss for typical LC VCO in steady-state |

| mode                                                                        |

| Figure 4.10: The proposed current-reuse LC VCO with capacitive feedback     |

| technique 120                                                               |

| Figure 4.11: Small signal half circuit of the LC VCO 121                    |

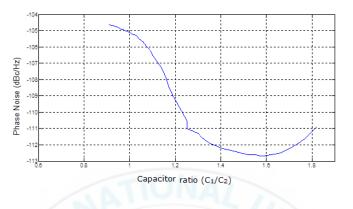

| Figure 4.12: Simulated phase noise versus capacitance ratio at 1 MHz offset |

| frequency                                                                   |

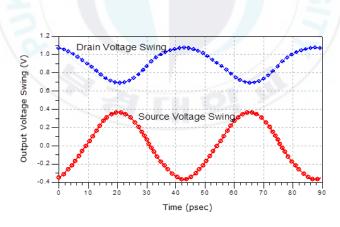

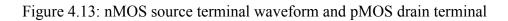

| Figure 4.13: nMOS source terminal waveform and pMOS drain terminal          |

| waveform                                                                    |

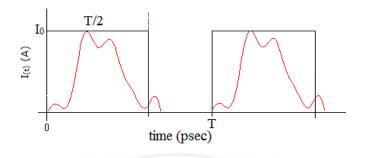

| Figure 4.14: Drain current waveform of M <sub>1</sub> 127                   |

## vii

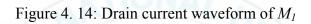

| Figure 4.15: Simulated peak-to-peak amplitude at the VCO output 127                              |

|--------------------------------------------------------------------------------------------------|

| Figure 4.16: (a) Capacitively source-degenerated negative resisstor (b)                          |

| Equivalent input impedance                                                                       |

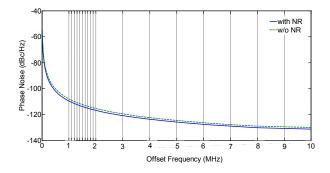

| Figure 4.17: Effect of negative resistance on the phase noise of the current-                    |

| reuse VCO                                                                                        |

| Figure 4.18: Current-reuse LC VCO with source noises                                             |

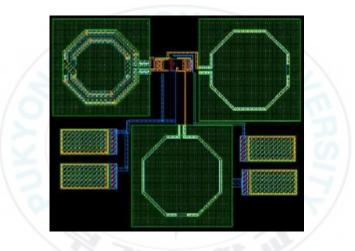

| Figure 4.19: The proposed current-reuse LC VCO layout                                            |

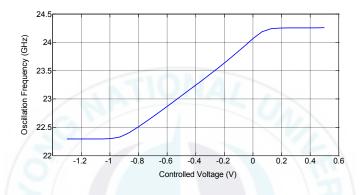

| Figure 4.20: V Simulated result of the tuning range of the current-reuse LC                      |

| VCO                                                                                              |

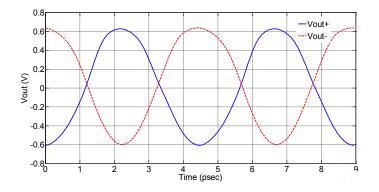

| Figure 4.21: Output waveforms of VCO at Vdd=0.9 V and Vt=-0.9 V 136                              |

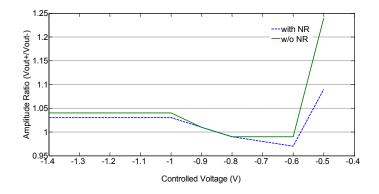

| Figure 4.22: Amplitude imbalance ratio of the VCO for controlled voltage                         |

| (Vt)                                                                                             |

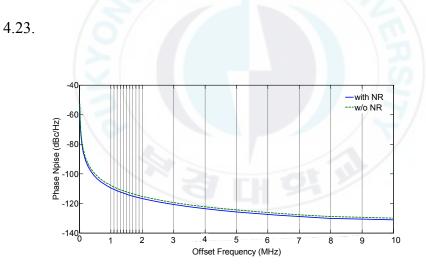

| Figure 4.23: Phase noise characteristic of the proposed current-reuse LC                         |

| VCO                                                                                              |

| Figure 5.1: Proposed 24 GHz receiver frontend                                                    |

| Figure 5.2: Schematic of t he prposed complementary push-pull LNA 145                            |

| Figure 5.3: Small-signal circuit of the LNA                                                      |

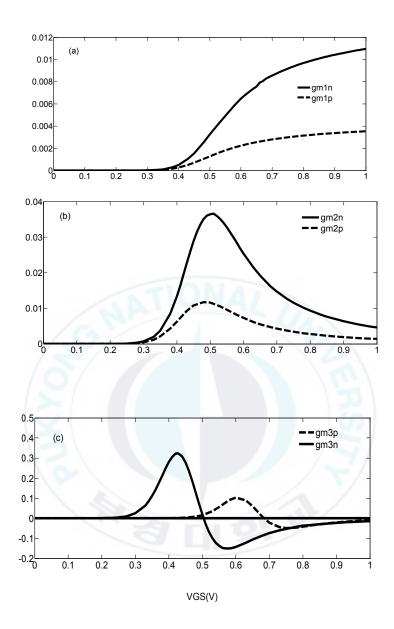

| Figure 5.4: (a) Simulated $gm_{1n}$ and $gm_{1p}$ ,(b) simulated $gm_{2p}$ and $gm_{2p}$ and (c) |

| simulated gm <sub>3n</sub> and gm <sub>3p</sub> 151                                              |

viii

| Figure 5.5: (a) Conventional mixer with two stage and (b) proposed mixer                |

|-----------------------------------------------------------------------------------------|

| using folded architecture                                                               |

| Figure 5.1: Conversion gain versus transuitor region                                    |

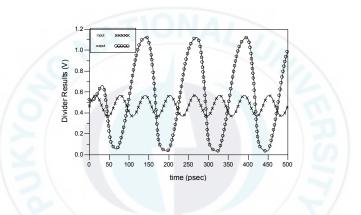

| Figure 5.7: Divided-by-2 E-TSPC frequency divider                                       |

| Figure 5.8: Input and output waveforms of the divided-by-2 frequency                    |

| divider with an input frequency of 16 GHz 158                                           |

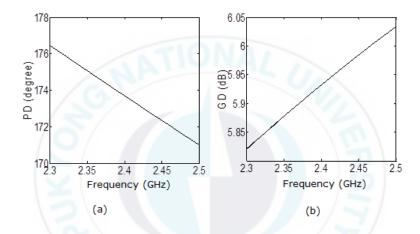

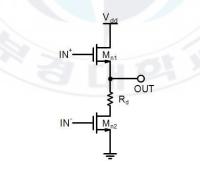

| Figure 5.9: Circuit schematic of single- to differential-ended balun 160                |

| Figure 5.10: (a) Phase difference (PD) and (b) gain difference (GD) between             |

| the output ports of S-D balun                                                           |

| Figure 5.11: Circuit schematic of the output differential-ended to single-              |

| ended balun                                                                             |

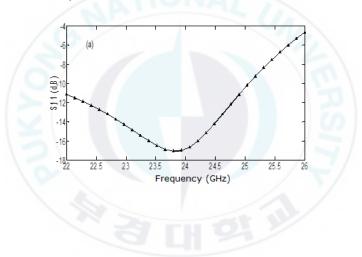

| Figure 5.12: Reflection coefficient of the proposed frontend versus                     |

| frequency: (a) Input return loss $(S_{11})$ , and (b) output return loss $(S_{22})$ 165 |

| Figure 5.13: Conversion gain versus frequency with 24-GHz LO signal 167                 |

| Figure 5.14: Total noise figure (NF) of the proposed frontend versus                    |

| frequency                                                                               |

| Figure 5.15: IIP3 of the proposed frontend versus RF Power                              |

## ix

## List of Table

| Table 2.1 Aspect ratio of transistors and the value of components       58 |

|----------------------------------------------------------------------------|

| Table 2.2 Comparison of the simulation results of the proposed LNA and     |

| therecently published works                                                |

| Table 4.1 Comparison of the simulation results of the proposed LNA and     |

| therecently published works                                                |

| Table 5.1 Circuit parameters of the LNA and mixers    162                  |

| Table 5.2 Circuit parameters of the divider and Baluns       163           |

| Table 5.3 Comparison of the results of the proposed receiver frontend and  |

| recently published works                                                   |

х

#### Acknowledgement

All glory is to God Almighty for his all-sufficient love for me all through my journey in this school and the successful completion of my PhD degree. I would never have been able to finish my dissertation without the guidance of my committee members, help from friends, and support from my family.

First and foremost, I would like to express my profound gratitude to my advisor, Prof. Jee-Youl Ryu, for the patient guidance, encouragement and advice he has provided throughout my time as his student. I have been extremely lucky to have an advisor who cared so much about my work, and who responded to my questions and queries so promptly. Moreover, I would like to thank the rest of my thesis committee members.

I am deeply grateful to all professors of the Department of Information & Communications Engineering and Korean Government for its full financial support during my PhD degree.

Finally, my deepest gratitude goes to my beloved family for their endless love, prayers, encouragement, spiritual and moral support without whom I would never have enjoyed so many opportunities.

xi

### Habibollah Rastegar

Department of Information & Communication Engineering

Pukyong National University, Busan, South Korea

xii

#### Low-Power High-Linearity CMOS Radio Frequency Receiver Frontend

for 24GHz Automotive Collision Avoidance Radar

Habibollah Rastegar

Department of Information and Communications Engineering,

The Graduate School,

Pukyong National University

#### Abstract

Communication has experienced explosive growth world-wide in the last decade and its huge market potential is driving relentless efforts in the information industry to improve the performance of wireless communication systems. Academia has also witnessed a flourish of research activities in communications, digital signal processing and radio frequency integrated circuit design.

Fuelled by the ever increasing demand for wireless products and the advent of deep submicron CMOS, RF ICs have become fairly commonplace in the semiconductor market. This has given rise to a new breed of Systems-On-Chip (SOCs) with RF front-ends tightly integrated along with digital, analog and mixed signal circuitry. However, the reliability of the integrated RF front-end continues to be a matter of significant concern and considerable

xiii

research. A major challenge to the reliability of RF ICs is the fact that their performance is also severely degraded by wide tolerances in on-chip passives and package parasitics, in addition to process related faults.

An RF front end receiver system refers to the analog down conversion stages of the wireless communication system. The Digital base-band signals cannot be transmitted directly through wireless channels due to the properties of electromagnetic waves. The baseband signals need to be converted to analog through a digital-to-analog converter (DAC), up converted to higher frequency using an up conversion mixer and then transmitted through the channel. The received signals are down converted to base band frequency and then converted to digital again using the analog to digital converter (ADC). The processes which the analog signal undergoes at the RF front end include amplification, mixing and filtering

The main wireless receiver task is to detect the desired modulated signals. Wireless receivers have to perform several functions such as tuning to the wanted signal carriers, filtering out the undesired signals, and amplifying the desired signal to compensate for power losses occurring during transmission. However, there are several receiver architectures, and the heterodyne and the direct conversion are the most popular.

In this dissertation, a modified IF receiver architecture is adopted as a compromise between the heterodyne and the direct conversion to have immunity against flicker noise, dc offset and I/Q mismatch, and to achieve higher integration. In a receiver frontend, either wired or wireless low noise amplifier (LNA) is the first gain stage after antenna. LNA should amplify all these signals without causing any significant distortion for the following

xiv

stage to handle. This sets the requirement of a certain gain to the LNA. Furthermore, the sensitivity of the receiver chain is determined by sensitivity of the LNA. This requires that a little noise from LNA must be introduced to the overall receiver.

Down conversion mixers as the next stage after LNAs in receiver frontend are more vulnerable than the other stages due to their configuration. They should translate the high frequency signals to either intermediate or baseband frequency ones.

Voltage-controlled oscillator (VCO) is an independent circuit, since some selfsustaining mechanism generates a periodic stable sinusoidal signal. VCO also can be used as a part of the frequency synthesizer to produce the local oscillator signal for both down/upconversion mixers. An ideal VCO should meet most of these specification such as low phase noise, low power, wide tuning range, high integration, small die area accuracy and low cost.

This dissertation shows that significant benefits are achieved with continued design innovations in spite to the general belief that RF circuit design is a mature subject. With the down scaling of CMOS process, efforts in CMOS RFIC design has been continuing the future for long time.

XV

#### **1** Introduction

#### 1.1 Motivation

Nowadays, road traffic crashes have become a major global concern. To enhance safety, automotive radar devices are now installing on many transport and luxury passenger vehicles. Automotive radars are utilized in advanced cruise control (ACC) systems which can provide information for driver, and actuate a motor vehicle's accelerator and/or brakes to control its distance separation behind another vehicle. Radar-based driver assistance systems also have other important functions such as collision warning systems, blind-spot monitoring, lane-change assistance, rear cross-traffic alerts and back-up parking assistance, collision mitigation systems and vulnerable road user detection.

Thanks to growing speed of radar-based collision avoidance systems, vehicles can see the other objects including pedestrian and other vehicles, anticipate accidents and collision, control the braking system and steering wheel to save the people life, and reduce the severity of collisions.

Radar transceivers are installed on the vehicles which operate in the all types of weather or sometimes both laser and camera are utilized to anticipate the imminent collision on the street or highways. At first, collision

avoidance systems search the surrounded area of the vehicles to detect the imminent crash. When the detection process is done, the system warns to the drivers by light, vibration in steering wheel or seat belt, and then the system based on the predefined distance fastens the seat belt and brakes, and finally controls the steering wheel to save the driver.

The main frequency bands of radar applications are 24GHz and 77GHz. For the sake of detection of other near vehicles in the medium-short range and wide beam, 24GHz is mainstream. The receiver for the automotive radar system operates in the band of 24 GHz frequency which is composed of low noise amplifier (*LNA*), downconversion mixer, and voltage-controlled oscillator (*VCO*).

#### **1.2 Proposed Receiver Frontend Architecture**

The main wireless receiver task is to detect the desired modulated signals. Wireless receivers have to perform several functions such as tuning to the wanted signal carriers, filtering out the undesired signals, and amplifying the desired signal to compensate for power losses occurring during transmission. However, there are several receiver architectures, and the heterodyne and the direct conversion are the most popular. Typically, a heterodyne receiver translates the desired input RF signal onto one or more preselected intermediate frequencies before modulation. In this architecture, image rejection and IF filters are vital to avoid folding of interfering signals. Because of presence of several bulky and expensive RF/IF filters, the heterodyne architecture is not suitable for monolithic integration. Enforced by the trends to the cost and size of the RF frontend, alternative heterodyne architecture has been proposed. For instance, direct conversion technique converts the RF signals to the IF-zero baseband in the first frequency downconversion. Therefore, the receiver frontend can be realized in low cost and low power architecture due to the unnecessary offchip IF filters. Despite superior performances of direct conversion architecture, it suffers from the dc offset and LO leakage which leads to complicate the design and implement of individual blocks to relax the specifications of system.

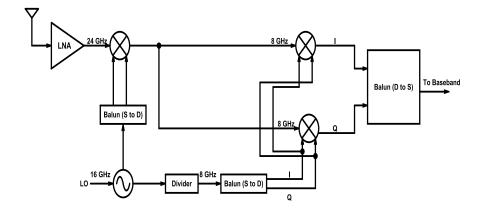

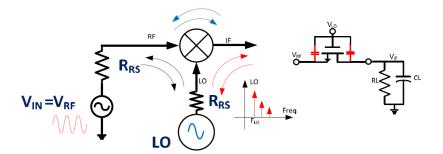

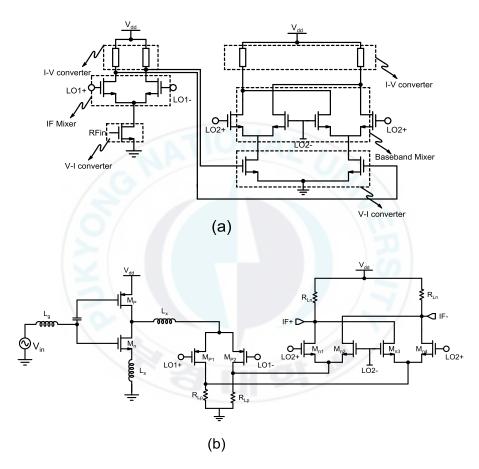

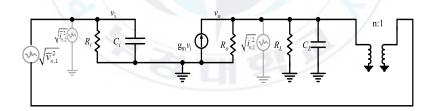

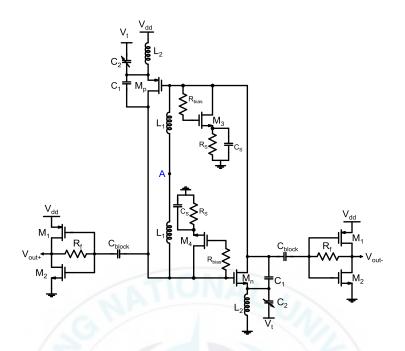

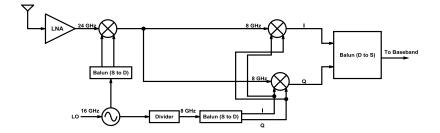

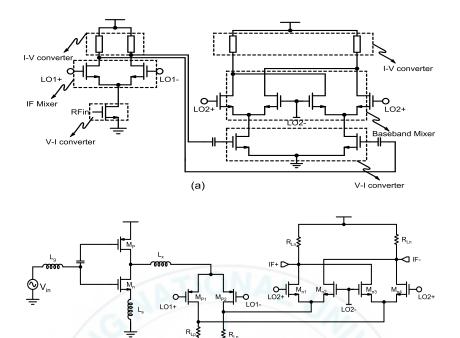

A modified IF receiver architecture is adopted as a compromise between the heterodyne and the direct conversion to have immunity against flicker noise, dc offset and I/Q mismatch, and to achieve higher integration. The block diagram of the proposed receiver frontend is illustrated in Figure 1.1. First, LNA amplifies the incoming RF signal at 24 GHz. Then the amplified

signal is down-converted to a low IF of 10 MHz by the first and second mixer stages. It is noted that the quadrature LO signals required for the second mixer are generated by dividing the first LO signal by 2.

The unwanted image signal can be attenuated approximately 20 dB by exploiting narrow band characteristic which is provided in the input port of LNA. A LO frequency of 16 GHz is applied to the first mixer to generate signals at an IF band of 8 GHz. Furthermore, the finite bandwidth of receiver frontend leads suppressing of the spurious band of 40 GHz which is generated by the first mixer stage. A divided-by-2 extended true-singlephase-clock (*E-TSPC*) frequency divider is also designed to provide the quadrature LO signals required for the second mixer stage. Therefore, the output signals of the second mixer stage are located at 10 MHz. In order not to use off-chip components such as buffer, balun and filters, an active balun is adopted to perform three tasks as follows: (*i*) convert the differential output of the second mixer to single-ended output for simulation of the frontend performances; (*ii*) match the output ports of the whole circuits to  $50\Omega$  to achieve  $S_{22}$  of less than -10 dB; (*iiii*) filter out the undesired image and spurious signals.

Figure 1.1: Proposed 24 GHz receiver frontend

#### 1.3 Objectives

The overall 24 GHz receiver frontend blocks including LNA, downconversion mixer, and VCO are presented in this dissertation. The proposed frontend aims to the radar-based collision avoidance applications. The objective of this dissertation is as follows:

• New receiver frontend architecture has been invented to fulfill the radarbased collision avoidance application criteria. Direct conversion receiver (*DCR*) is the best candidate among the various receiver architectures due to the low cost and low power issues. However, large dc offset, local oscillation (*LO*) leakage, flicker (*1/f*) noise, and I/Q mismatch are the bottlenecks of DCR receiver. To alleviate these problems, single intermediate frequency (*IF*) DCR architecture has been proposed with the advantage of both the super-heterodyne and DCR architectures. In this receiver type, at first, the incoming signal is converted to IF and then again it is converted to baseband frequency. This operation alleviates the specifications of the receiver backend and enables the analog-to-digital conversion at low frequencies

- To prove the validity of each block in the receiver frontend, a set of new mathematical formulas is given.

- New LNA has been designed, implemented, laid out and finally fabricated. The promising measurement results show that this LNA is potent for *RF* applications such as the radar-based collision avoidance. The designed LNA has unique structure and its features have been proved by mathematical equations The measurement results show the feasibility of the proposed circuit for wireless portable devices.

- The second block in receiver frontend is downconversion mixer. In the new implemented circuit, the LNA and mixer are combined to reduce the power consumption and increase the linearity of the overall receiver. The mixer circuit is employed in IF direct conversion receiver (*IF-DCR*) to

- 6

reach the predefined characteristics such as low noise, and low power consumption.

- New VCO is designed, implemented and laid out to generate the sine wave signal for the switching stage. To the best of author's knowledge, the proposed VCO has the lowest power consumption in comparison with the other similar works. High output swing and low phase noise as well are the great achievement from the new idea.

- Low power Baluns are designed to convert the differential input/output to single input/output or vice versa. The buffers are implemented by measuring purpose.

#### 1.4 Overview

The dissertation is organized as follows. In Chapter 2, the first block of receiver frontend known as LNA is presented. First, the background of LNA is presented and then the fundamental features of LNA are defined. These basic characteristics help the readers to get familiar with LNA parameters and the existing trade-offs between the output results of LNA which provide at the end of this chapter. After fundamental section, the new idea of LNA is proposed and proved with mathematical equations in depth detail. The

measurement results verify the validity of the new designed circuit for RF applications. The layout and die microphotograph of the proposed LNA are also presented. The comparison of the proposed idea with recently published works is given as well.

The overview of downconversion mixer is described and explained at the beginning of Chapter 3. Then different types of active mixer configurations are presented with pointing out to their advantages and disadvantages. At the end of Chapter 3, the new mixer topology is designed to reach the predefined characteristics such as low power consumption, high conversion gain (CG), and low noise figure (NF). The summary of this work is presented along with a table to bold the advantages of the new architecture.

Chapter 4 reviews the general features of the VCO. The background and fundamental issues of VCO are expressed in the first sections. On the continue, the major parameters of LC VCO are presented and the tradeoffs among them are given. The proposed circuit for RF application is presented. The implemented circuit is aimed for low power consumption, low phase noise and high output swing. To measure the result, two buffers are placed at the end of LC VCO.

In Chapter 5, the overall receiver frontend circuit is presented. The different blocks of receiver chain are integrated and placed on a single chip. Each block including LNA, mixer, and VCO is analyzed and explained in depth detail. The unique frontend architecture achieves high gain, low power consumption, and high linearity for the radar-based collision avoidance applications. The results of the proposed frontend with high level of integrity are illustrated at the end of this chapter. The layout of the receiver frontend is drawn as well.

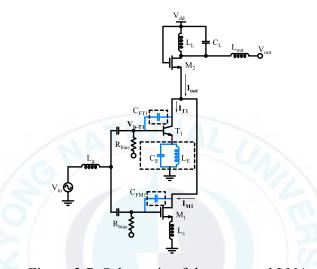

By integrating the two-stage LNA and downconversion mixers, the frontend has been designed in 130-nm CMOS technology. The LNA stage was adopted on complementary push-pull (*CPP*) topology to boost the gain and the linearity of whole circuit. Meanwhile, the LNA was realized in folded configuration to reduce power supply and to increase voltage headroom. The frontend was realized in IF-DCR architecture to increase integration level and alleviate the DCR problems. Two active baluns were also designed to increase the integrity of the frontend. Furthermore, the switch transistors were biased in subthreshold region to reduce the power consumption.

Chapter 6 concludes this dissertation and the further future investigation of this area is suggested at the end of this chapter.

#### 2 Design of Low Noise Amplifier

#### 2.1 Background

In a receiver frontend, either wired or wireless low noise amplifier (LNA) is the first gain stage after antenna. At the same time, it must meet several specifications which make its design really challenging. Signal coming from the receiver antenna at the input of LNA is very small and usually varies from less than -130dBm to -70dBm. Therefore, LNA should amplify all these signals without causing any significant distortion for the following stage to handle. This sets the requirement of a certain gain to the LNA. Furthermore, the sensitivity of the receiver chain is determined by sensitivity of the LNA. This requires that a little noise from LNA must be introduced to the overall receiver. According to Friis equation, gain of LNA should be as high as possible to suppress the noise of subsequent blocks. In other words, a certain signal-to-noise ratio (SNR) is required for the LNA to detect the coming signal reliably, and hence noise added by the circuit should be reduced as much as possible, which will set the noise requirement of the LNA.

Low-pass filter (LPF), high-pass (HPF) and band-pass filter (BPF) are located before and after LNA to delete and reduce the unwanted signals.

The transfer function of the filter is usually a dependent variable of termination impedance. Based on IEEE standards, there are specific input/output termination impedances, i.e.  $50\Omega$  or  $75\Omega$  on the LNA. The LNA noise is also a function of source impedance. It's noteworthy that the optimum source impedance for minimum noise figure might be different from the one required for the preceding stage, e.g.  $50\Omega$ . There are trade-offs between gain, noise figure and input/output matching impedance.

The receiver chain has to be able to minimize or cancel the adverse effects of large number in-band interferences and inter-modulation/crossmodulation caused by transmitter leakage or blockers. Thus, to have a reasonable signal reception the circuits should be sufficiently linear. Low power consumption is another constraint for mobile and portable applications.

LNA design involves trade-offs among many figures of merits such as gain, noise, power dissipation, input matching, stability, and linearity [1]. Such an amplifier must feature wideband input matching to a 50 $\Omega$  antenna, flat gain over the entire bandwidth, good linearity, minimum possible noise figure, and low power consumption [2].

A careful study is required to satisfy all the above-mention trade-offs in designing either narrowband or wideband LNA. To achieve this goal one

needs to provide an analytical model for the LNA and find the equations for the LNA characteristics such as gain, linearity and noise figure.

#### 2.2 S-parameters

Scattering parameters, which are commonly referred as S-parameters are widely used in design and analysis of microwave and RF circuits. A parameter set is used in S-parameters that relates to the traveling waves that are scattered or reflected when an n-port network is inserted into a transmission line.

To characterize an n-port linear network, S-parameter analysis is basically used as a modelling method. H-parameters, Y-parameters and Zparameters are other methods to characterize the n-port network. Since they are behavioural modelling methods, we can put all of them into the same category for a network. The device or n-port network is assumed as a black box, and only the interaction between the ports and outer environment is modelled. For instance, in low frequencies, H-, Y-, or Z-parameters are widely used since voltage and current are the variables to find the transfer function. However if we want to use H-, Y-, or Z-parameters, some problems arise for relatively high frequencies.

For applying short and/or open circuit condition at each port in H, Y or Z measurement, it is hard especially to RF bands. Active devices such as transistors and tunnel diode very often cannot be connected in stable short or open circuit conditions.

S-parameters, on the other hand, are usually measured with the device embedded between a 50 $\Omega$  load and source, and there is very little chance for oscillations to occur. Another important advantage of S-parameters stems from the fact that traveling waves unlike terminal voltages and currents do not vary in magnitude at points along a lossless transmission line. This means that S-parameters can be measured on a device located at some distance from the measurement transducers.

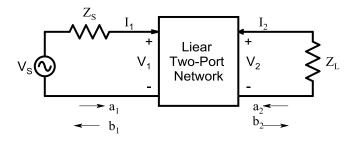

The behaviour of the two-port network in Figure 2.1 can be described by the linear equations using S-parameters as defined in Eqs. (2.1) and (2.2).

| $b_1 = S_{11}a_1 + S_{12}a_2$ | (2.1) |

|-------------------------------|-------|

| $b_2 = S_{21}a_1 + S_{22}a_2$ | (2.2) |

where  $a_1$ ,  $a_2$ ,  $b_1$  and  $b_2$  are traveling wave.

Figure 2.1: Two-port network for incident waves (a<sub>1</sub>, a<sub>2</sub>) and reflected waves (b<sub>1</sub>, b<sub>2</sub>) used in S-parameters definitions

The S-parameters are defined as defined in Eqs. (2.3) to (2.6).

$$S_{11} = \frac{b_1}{a_1} |_{a_2=0}$$

$$S_{22} = \frac{b_2}{2} |_{a_1=0}$$

$$S_{21} = \frac{b_2}{a_1} |_{a_2=0}$$

$$S_{12} = \frac{b_1}{a_2} |_{a_1=0}$$

(2.3)

(2.4)

(2.4)

(2.5)

(2.5)

(2.6)

For simplicity in measurement and calculation, we assume that both input and output ports are real and positive, and have same reference impedance of  $Z_{0}$ .

The independent variables  $a_1$ ,  $a_2$ ,  $b_1$  and  $b_2$  can be related to port voltages  $(V_1, V_2)$  and currents  $(I_1, I_2)$  as expressed in Eqs.v(2.7) to (2.10).

$$a_1 = \frac{V_1 + I_1 Z_0}{2\sqrt{Z_0}} = \frac{V_{i1}}{\sqrt{Z_0}}$$

(2.7)

$$a_2 = \frac{V_2 + I_2 Z_0}{2\sqrt{Z_0}} = \frac{V_{i2}}{\sqrt{Z_0}}$$

(2.8)

$$b_1 = \frac{V_1 - I_1 Z_0}{2\sqrt{Z_0}} = \frac{V_{r_1}}{\sqrt{Z_0}} \tag{2.9}$$

$$b_2 = \frac{V_2 - I_2 Z_0}{2\sqrt{Z_0}} = \frac{V_{r_2}}{\sqrt{Z_0}}$$

(2.10)

where  $V_{i1} = \frac{V_1 + I_1 Z_0}{2}$  and  $V_{i2} = \frac{V_2 + I_1 Z_0}{2}$  are incident voltage waves on port 1 and 2 respectively.

$V_{r1} = \frac{V_1 - I_1 Z_0}{2}$  and  $V_{r2} = \frac{V_2 - I_2 Z_0}{2}$  are reflected voltage waves from port 1 and poert 2 respectively.

$|a_1|^2$  is the incident power on the input of the network, and it is also the available power from source impedance  $Z_0$ .  $|b_1|^2$  is the reflected power from the input port of the network, or the available power from a  $Z_0$  source minus the power delivered to the input of the network.  $|a_2|^2$  is the incident power on the output of the network, and it is also the reflected power from the load.  $|b_2|^2$  is the reflected power from the output port of the network, or the incident power on the load which is also the power delivered to a  $Z_0$  load.

The expressed S-parameters related to the mentioned definition of  $a_1$ ,  $a_2$ ,  $b_1$  and  $b_2$  are as follows:

$$|S_{11}|^2 = \frac{\text{Refelected power from input network}}{\text{Incident power on the input network}}$$

(2.11)

$$|S_{22}|^2 = \frac{\text{Refelected power from output network}}{\text{Incident power on the output network}}$$

(2.12)

$$|S_{21}|^2 = \frac{Power \ deliverd \ to \ Z_0 \ load}{available \ power \ from \ Z_0 \ source}$$

=Transducer power gain with

$$Z_0$$

load and source (2.13)

$|S_{22}|^2 = Reverse trabsducer power gain with z_0 load and source (2.14)$

#### 2.3 Power Gain

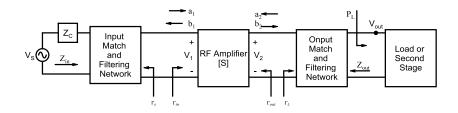

The input/output impedance matching network and RF transistor are the parameters which determine and control the gain performance for a RF amplifier such as LNA. Consider the basic block diagram of an amplifier shown in Figure 2.2. The amplifier is modeled by its S-parameters and terminated by arbitrary source and load impedance,  $Z_S$  and  $Z_L$ .  $S_{11}$  and  $S_{22}$  are the input and output reflection coefficients with  $Z_0$  source and load terminations, respectively.

Figure 2.2: Block diagram of single-stage RF amplifier

The input and output reflection coefficients  $\Gamma_{in}$  and  $\Gamma_{out}$  for a network with an arbitrary impedance termination can be described as Eqs. (2.15) and (2.16) [3].  $\Gamma_{in} = \frac{b_1}{a} = S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 + S_{12}\Gamma_L}$  (2.15)

$$\Gamma_{out} = \frac{b_2}{a_2} = S_{22} + \frac{S_{11}S_{21}\Gamma_s}{1 - S_{11}\Gamma_s}$$

(2.16)

where  $\Gamma_s = \frac{Z_s - Z_0}{Z_s + Z_0}$  and  $\Gamma_L = \frac{Z_L - Z_0}{Z_L + Z_0}$  are the source and load reflection coefficients, respectively.

The amplifier reaches its maximum power transfer function if at the same time the input and output are complex conjugate matched, i.e.  $\Gamma_{in} = \Gamma_S^*$  and  $\Gamma_{out} = \Gamma_L^*$ . When  $S_{12}$  is approximately or practically zero, the amplifier is so called bilateral  $(S_{12}=0)$ . In bilateral case,  $\Gamma_{in} = S_{11}$  and  $\Gamma_{out} = S_{22}$  which means impedance matching at the input and output ports can be done separately and these ports are decoupled from the other one.

There are several gain definitions for an amplifier. Power gain (G) is defined as the power delivered to the load divided by the power inserted to the network. Available power gain (GA) shows the maximum possible power amplification of the amplifier.

The voltage gain  $(A_v)$  is defined as the voltage at the output port divided by the voltage at the input port of the amplifier as expressed in Eq. (2.18) [3].

$$A_{\nu} = \frac{V_2}{V_1} = \frac{S_{21}(1+\Gamma_L)}{(1-S_{22}\Gamma_L)(1+\Gamma_{in})}$$

(2.17)

The transducer power  $(G_T)$  is defined as the power delivered to the load divided by the power available from the source [3]

(2.18)

$$G_T = \frac{P_L}{P_{AVS}}$$

where  $P_L$  is defined as:

$$P_L = |b_2|^2 (1 - |\Gamma_L|^2). \tag{2.19}$$

$P_{AVS}$  is also defined as

$$P_{AVS} = \frac{|b_2|^2}{1 - |\Gamma_S|^2}.$$

(2.20)

where

$$b_s = \frac{V_s \sqrt{Z_0}}{Z_s + Z_0}$$

.

Thus,

$$G_T = \left| \frac{b_2}{b_s} \right|^2 (|1 - \Gamma_s|^2) (|1 - \Gamma_L|^2)$$

(2.21)

Using the signal flow chart, the ratio  $\frac{b_2}{b_s}$  can be given as

$$\frac{b_2}{b_s} = \frac{S_{21}}{(1 - S_{11}\Gamma_s)(1 - S_{22}\Gamma_L) - S_{12}S_{21}\Gamma_s\Gamma_L}$$

(2.22)

Finally, the transducer power gain is expressed as

$$G_T = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2) (1 - |\Gamma_L|^2)}{(1 + S_{11}\Gamma_S) (1 + S_{22}\Gamma_L) - S_{12}S_{21}\Gamma_S\Gamma_L}$$

(2.23)

For a bilateral, i.e.  $S_{12}$  is very small and effectively zero, Eq. (2.23) can be approximated as Eq. (2.24).

$$G_T = \frac{1 - |\Gamma_S|^2}{|1 + S_{11} \Gamma_S|^2} |S_{21}|^2 \frac{1 - |\Gamma_L|^2}{|1 + S_{22} \Gamma_L|^2} = G_S |S_{21}|^2 G_L$$

(2.24)

This current formula is in terms of reflection coefficients and input/output return losses. We offer to re-write the above equation in terms of impedances to explicitly reflect the effect of IMF. It can be obtained maximum power gain when both the input and output ports are complex conjugate matched (i.e.,  $\Gamma_S = S_{11}^*$  and  $\Gamma_L = S_{22}^*$ ). The maximum power gain ( $G_{max}$ ) is given as:

$$G_{max} = \frac{1}{1 - |S_{11}|^2} |S_{21}|^2 \frac{1}{1 - |S_{22}|^2}$$

(2.25)

Now available power gain of the LNA can be written as the multiplication of the maximum power gain and IMF, if there is an impedance mismatch at the input port of the LNA.

$$G_{LNA} = \underbrace{\frac{4R_s R_{in}}{(Z_{in} + Z_s)^2}}_{IMF} G_{max}$$

(2.26)

where  $Z_{in}$  are  $Z_S$  are the input and source impedances shown in Figure 2.2.

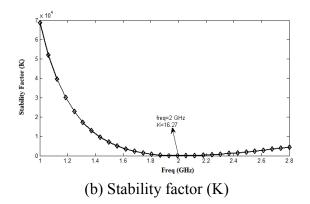

## 2.4 Stability Factor

Stability is also a very important parameter of RF amplifier. The other parameters such as gain, noise figure are meaningful when the amplifier is stable. By assuming the input impedance at the input port of the amplifier  $Z_i$ =  $R_i + jX_i$ , then the  $\Gamma_{in}$  is expressed in Eq. (2.27):

$$\Gamma_{in} = \left| \frac{Z_i - Z_0}{Z_i + Z_0} \right| = \sqrt{\frac{(R_i - Z_0)^2 + X_i^2}{(R_i + Z_0)^2 + X_i^2}}$$

(2.27)

If the real part of the input resistance  $R_i$  is negative, i.e.  $R_i < 0$ , then  $|\Gamma_{in}| > 1$ . Oscillation can occur if the loss coms from the input termination network compensated by negative resistance. The amplifier is potentially unstable. We have same scenario for the stability issue of output port. Therefore, the amplifier is unconditionally stable if for all the passive terminations at the input and output ports, Eqs (2.28a) and (2.28b) would be satisfied. Otherwise, it is potentially unstable or conditionally stable.

$$|\Gamma_{in}| < 1$$

(2.28a)

$|\Gamma_{out}| < 1$  (2.28b)

In term of S-parameters, it can be expressed that the amplifier are unconditionally stable if it has the following conditions.

| $ S_{11}  < 1$ | (2.29a) |

|----------------|---------|

| $ S_{22}  < 1$ | (2.29b) |

| K > 1          |         |

(2.29c)

where k is the stability factor given by Eq. (2.30).

$$K = \frac{1 - |S_{11}|^2 + |S_{22}|^2 + |S_{11} + S_{22} - S_{12} + S_{21}|^2}{2|S_{12} + S_{21}|} > 1$$

(2.30)

Adding a shunt conductance or a series resistance to the unstable port is the simple method to stabilize an active device. Practically, since the input and output ports of the amplifier are coupled to the other, it is usually enough to stabilize one of the ports. One should not add a series resistance or a shunt conductance to the input port of the amplifier, since it will cause additional noise to be amplified. Therefore, the best way is to stabilize the output port.

## 2.5 Noise

In communication systems, undesired signal is called noise, and noise reduces the sensitivity of the overall system. There are a variety of noise sources with different noise generation. In the integrated circuits the dominant sources of noise are shot noise, flicker noise, and thermal noise. Shot noise is mainly caused by the hopping of electric charges over a potential barrier, and it is specific to nonlinear devices such as diodes and transistors. In MOS devices, the only source of shot noise is the dc gate leakage current, and hence it is not considered a major problem [4]. In Bipolar Junction Transistor (BJT) base and collector shot noise are the main

sources, and they may significantly degrade the performance of the overall receiver.

Flicker noise, also known as pink noise, occurs due to the trapping of charges in the defects and impurities of the channel region in MOS devices [4]. As can be seen from the Eq. (2.31), flicker noise is inversely proportional to the operational frequency (f). In the other words, larger MOS devices with large W lead to less flicker noise. The spectral density of this noise is given by Eq. (2.31).

$$\overline{\iota_{fn}^2} = \frac{K.g_m^2}{fWLC_{ox}^2}$$

(2.31)

where K is a device geometric constant, W and L are the width and length of the MOS device, ,  $C_{ox}$  is the gate-oxide capacitance per unit area, and  $g_m$  is the trans-conductance of the MOS device, respectively.

Therefore, at very low frequencies the dominant noise source is flicker noise. Flicker noise does not play an important role LNAs because the frequency range of the received signal is several gigahertzes, and hence it can be ignored. It is noteworthy that in mixers or voltage controlled

oscillators (*VCOs*) flicker should be considered and it can be a major problem.

### 2.5.1 Noise Sources

The generic small signal model of a cascode topology with noise sources is shown in Figure 2.3. There are four sources of noise. It contains the thermal noise of source resistance  $(i_{n,Rs})$ , thermal noise of the channel current  $(i_{n,d})$ , the gate-induced current noise  $(i_{n,g})$ , and the

thermal noise of the output resistance  $(i_{n,out})$ . The power spectral densities

$$(PSDs) \text{ of } i_{n,Rs}^{2} \text{ and } i_{n,Rout}^{2} \text{ are as Eqs. (2.32) and (2.33).}$$

$$i_{n,Rs}^{-} = 4kT \frac{1}{R_s} \Delta f \qquad (2.32)$$

$$i_{n,Rout}^{-} = 4kT \frac{1}{R_{out}} \Delta f \qquad (3.33)$$

where *T* is the absolute temperature in Kelvin,  $\Delta f$  is the noise bandwidth in Hz and *k* is the Boltzmann constant.

The PSDs of channel current thermal and gate-induced noises are given by Eqs. (2.34) and (2.35)[5-6].

$$i_{n,d}^2 = 4kT\gamma g_{d0}\Delta f \tag{2.34}$$

$$i_{n,g}^2 = 4kT\delta g_g \Delta f \tag{2.35}$$

where  $g_g$  is the equivalent shunt gate conductance, given by Eqs. (2.36) [5].

$$g_{g} = \frac{(\omega C_{gs})^{2}}{5g_{d0}}$$

(2.36)

where  $g_{d0}$  is the drain conductance for zero drain-source voltage and  $\gamma$  is a technology-dependent parameter with a value of approximately 2/3 for longchannel devices in saturation region (in short channel devices  $\gamma$  is larger and its value is between 2 and 3) [7].  $\delta$  is the gate noise coefficient and is also a technology-dependent parameter. The value of  $\delta$  is 4/3 for long channel devices and it is augmented by a factor of 2 in short channel devices.

## 2.5.2 Noise Figure

Noise figure (*NF*) is measurement factor of degradation of signal-to-noise ratio (*SNR*) as the incoming signal from antenna traverses the receiver frontend. Mathematically, noise figure is defined as the ratio of the input SNR to the output SNR of the system as expressed in Eq. (2.37).

$$NF = \frac{SNR_{in}}{SNR_{out}} = \frac{output \text{ noise power due to source}}{total output \text{ noise power}}$$

(2.37)

NF can be defined in two ways, for each block separately or the entire receiver. The LNA noise  $NF_{LNA}$  determines the inherent LNA noise, added to the desired or wanted signal during the process of amplification.

According to the classical two-port network, NF of a noisy two-port network can be written as Eq. (2.38).

$$NF = NF_{min} + \frac{R_n}{G_s} \left[ \left( G_s - G_{opt} \right)^2 + \left( B_s - B_{opt} \right)^2 \right]$$

(2.38)

where  $NF_{min}$  is the minimum achievable NF,  $B_{opt}$  and  $G_{opt}$  are the optimum source susceptance and conductance corresponding to  $NF_{min}$ , and  $R_n$  is an equivalent noise resistance, which quantifies the sensitivity of NF to departure from optimum conditions and  $B_S$  and  $G_s$  are the source susceptance and conductance.

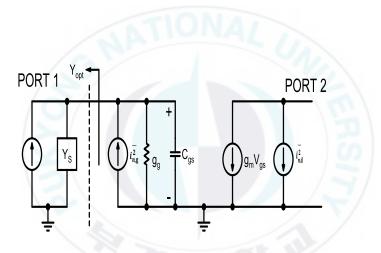

NF is a function of source admittance looking into the input terminal of the two-port network. To achieve the  $NF_{min}$ , an optimum admittance, namely  $Y_{opt}$ , should be introduced to the network. The expressions for  $NF_{min}$  and  $Y_{opt}$ can be derived for a MOS device by considering a two-port network model for the MOS device. In this model the gate-source terminal is the input port, and the drain-source terminal is the output port.

The small signal model of a MOS device which consists of all noise sources connected to the noise source  $i_s^2$  and the source admittance  $Y_s=G_s+jB_s$  are shown in Figure 2.3.

We assume that in MOS devices  $i_{n,g}^2$  and  $i_{n,d}^2$  are dominant noise sources and for the noise parameters and  $NF_{min}$  can be obtained in Eqs. (2.39) to (2.42).

Figure 2.3: MOS model of two-port network for noise calculations

$$R_n = \frac{\gamma g_{d0}}{g_m^2} \tag{2.39}$$

$$G_{opt} = \alpha \omega C_{gs} \sqrt{\frac{5}{5\gamma}} (1 - |c|^2)$$

(2.40)

$$G_{opt} = -\omega C_{gs} (1 - \alpha |c| \sqrt{\frac{\delta}{5\gamma}})$$

(2.41)

$$NF_{min} \approx 1 + \frac{2}{\sqrt{5}} \frac{\omega}{\omega_t} \sqrt{\frac{\delta}{5\gamma} (1 - |c|^2)}$$

(2.42)

where  $\alpha = g_m/g_{d0}$  equal to one for long channel devices and, it decreases as devices shrink to smaller dimensions.

It is obvious from Eq. (2.42) that with the increasing transition frequency  $(f_t)$  the minimum noise figure decreases. It should be noted that as CMOS scaling down, the transion frequency increases. Therefore, employing CMOS technology will be an advantage for having low noise figure.

## 2.5.3 Output Noise of the First Stage

The input impedance of the cascode topology using inductively degenerated technique will explain in Section 2.7. Figure 2.4 shows small-signal model of a cascade topology with inductively degenerated noise sources. The input impedance should be equal to the source impedance  $R_s$ , and it can be expressed as Eq. (2.43).

$$Z_{in} = g_m \frac{L_s}{C_t} = R_s = 50\Omega \tag{2.43}$$

where  $L_s$  is the source inductor,  $C_t$  is the total capacitance seen from source.

The quality factor of input circuit is then

$$Q = \frac{1}{(R_s + g_m \frac{L_s}{C_t})\omega_0 C_t} = \frac{1}{2R_s \omega_0 C_t}$$

(2.44)

where  $\omega_0$  is the resonance frequency of input matching network.

The output noise  $(i_{n,out})$  of four noise sources (shown in Figure 2.4) at  $\omega_0$  is as described in Eq. (2.45) to (2.48).

$$i_{n,out,Rs} = \frac{g_m}{j2\omega_0 C_t} i_{n,Rs} \tag{2.45}$$

$$i_{n,out,Rout} = i_{n,Rout} \tag{2.46}$$

$$i_{n,out,d} = \frac{1}{2}i_{n,d}$$

(2.47)

$$i_{n,out,g} = \frac{g_m}{j\omega_0 C_t} \frac{jR_s\omega_0 C_t - 1}{j2R_s\omega_0 C_t} i_{n,g}$$

(2.48)

Now the correlation coefficient between  $i_{n,g}$  and  $i_{n,d}$  is given by Eq. (2.49) [8-9].  $c = \frac{\overline{i_{n,g}.i_{n,d}^*}}{\sqrt{i_{n,g}^2.i_{n,d}^2}}$ (2.49)

For a long channel device, c = -0.395j, and its magnitude decreases as the channel length scales down [5].

The *PSD* of output current due to  $i_{n,g}$  and  $i_{n,d}$  can be calculated as Eq. (2.50).

$$\vec{i_{n,out,g+d}} = \overline{(A\iota_{n,g} + B\iota_{n,d})(A\iota_{n,g} + B\iota_{n,d})^*}$$

$$= |A|^2 \vec{i_{n,g}} + |B|^2 \vec{i_{n,d}} + AB^* \overline{\iota_{n,g}} \cdot \vec{\iota_{n,d}} + A^* B \overline{\iota_{n,g}} \cdot \iota_{n,d}$$

(2.50)

where, B and A are the transfer function of Eqs. (2.47) and (2.48), respectively.

The last two terms of Eq. (2.50) are output noise due to correlation, and can we obtain by using Eqs. (2.48), (2.49) and (2.5).

$$\vec{i_{n,out,c}} = (jcAB^* - jcA^*B) \sqrt{\vec{i_{n,g}} \cdot \vec{i_{n,d}}^2}$$

$$= \frac{g_{m,c}}{2\omega_0 c_t} \sqrt{\vec{i_{n,g}} \cdot \vec{i_{n,d}}^2}$$

(2.51)

By using Eq. (2.44), the total noise factor of cascode topology at  $\omega_0$  is calculated as Eq. (2.52).

$$F_{firs \, tstage} = \frac{\frac{i_{n,out,Rs}^{-} + i_{n,out,d}^{2} + i_{n,out,g}^{2} + i_{n,out,Rout}^{2} + i_{n,out,Rout}^{2} + i_{n,out,c}^{2}}{i_{n,out,Rs}^{2}}$$

(2.52)

After simplification of Eq. (2.52), we can obtain as Eq. (2.53) to (2.55).

$$F_{first \, stage} = 1 + \frac{g_{g1}(Q^2 + \frac{1}{4})P^2 \, \frac{g_m^2}{g_{dn}} + \gamma_1 \frac{g_{dn}}{4} + \sqrt{\frac{\gamma_1 g_{g1}}{4}} \, cPg_m + \frac{1}{R_{out}}}{R_s Q^2 g_m^2}$$

(2.53)

$$P = \frac{c_{\rm gs}}{c_t} \tag{2.54}$$

$g_{dn} = \gamma g_{d0} \tag{2.55}$

The long-channel values for  $g_{g1}$  and  $\gamma_1$  are 8/45 and 1, respectively. Parameter *P* is always less than unity, since  $C_t$  is always greater than  $C_{gs}$  due to the additional capacitance ( $C_{ex}$ ).

According to Friis equation, the total noise factor of the designed CMOS LNA is as defined by Eq. (2.56).

$$F_{total} = F_{first-stage} + \frac{F_{subsequent}-1}{G_F}$$

(2.56)

where,  $F_{first-stage}$  is the noise factor of the cascode topology,  $F_{subsequent}$  is the noise factor of the subsequent stages of LN A, and  $G_F$  is gain of first stage of LNA.

Therefore, due to high  $G_F$ , the dominant noise source of the LNA is the first stage noise. For this reason, *NF* is minimized at the first stage by using source inductive degeneration and inserting  $L_x$ . According to Eq. 34, it can be seen that by increasing  $g_m$ , F (or *NF* in *dB*) of the first stage can be improved.

Figure 2.4: Small signal model of a cascode topology with inductively degenerated and noise sources

# 2.5.4 Sensitivity

The frontend noise figure determines the sensitivity of the overall receiver. This relation is analytically given by Eq. (2.57). Sensitivity(dBm) =  $-174 \frac{dBm}{Hz} + 10 \log(BW) + NF_{tot} + 10 \log(SNR_{out})$  (2.57)

where -174dBm/*Hz* is the available noise power from the antenna and *BW* is the bandwidth of the desired signal, and the last term is the minimum acceptable *SNR* at the receiver output. As its obvious from (2.17), low NF of the LNA significantly leads to reduce the sensitivity of the whole receiver.

## 2.6 Linearity

Dynamic range (*DR*) is usually defined as the ratio of the maximum input signal without significant distortion that the circuit can tolerate to the minimum input signal which circuit provides adequate signal quality. Since the input signal of LNA is in the range of nano-volt (*nV*) or micro-volt ( $\mu V$ ), the LNA should possess a large DR to guarantee that it remains linear in the presence of strong distortions. In high frequency, the amplifiers in the receiver chain have to be able to minimize/cancel the adverse effects of large number in-band interferences and inter-modulation/cross-modulation caused by transmitter leakage or blockers. In high frequency amplifiers, nonlinear distortions including inter-modulation, cross-modulation and signal compression may be important and restrict the upper band of DR. However, in low frequency the upper limit of DR is generally defined as maximum input power that the circuit can handle without going into saturation region.

A large in-band blocker tends to desensitize the circuit. It is measured by the 1-dB compression point ( $P_{1dB}$ ). DR measures the signal handling circuit

capacity, which is limited by the third-order intercept point (*IIP3*) which will explain in details in next section and system noise floor. For high frequency circuits, there are plenty of methods of linearity measurement, but the most common ones are the 1-dB compression point and third-order intercept point.

## 2.6.1 1-dB Compression Point

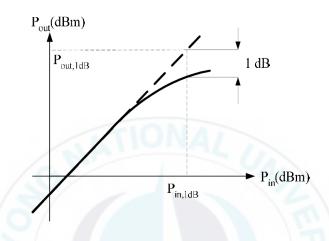

The input 1-dB compression point is generally defined as the amplitude of the input/output signal that causes fundamental gain to drop by 1dB from the ideal (or normal) small-signal gain at the specific frequency shown in Figure 2.5. Compression point is considered as an upper bound on the dynamic range of the LNA. Therefore, input signals at the out-of-band of the compression point are usually clipped or saturated at the output.

A nonlinear system can be approximated by using Taylor series described in Eq. (2.58).

$$y(t) = \alpha_1 x(t) + \alpha_2 x^2(t) + \alpha_3 x^3(t) + \cdots$$

(2.58)

The input-referred 1-dB compression point referred in [10] can be calculated as Eq. (2.59).

$$P_{1dB} = \sqrt{0.145 \left| \frac{\alpha_1}{\alpha_3} \right|} \tag{2.59}$$

where  $\alpha_1$  and  $\alpha_3$  are the first-order and third-order coefficients of Taylor series expansion.

Figure 2.5: 1-dB compression point

### 2.6.2 Third-order Input Intercept Point (IIP3)

Due to the nonlinear nature of the realistic systems, multiplication of the input signal with its harmonics may cause distortion.

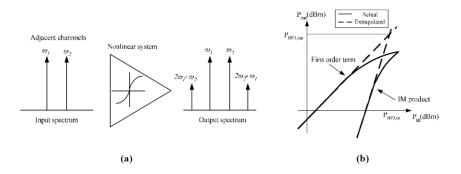

This multiplication leads producing output terms known as intermodulation products (IMP). For example, if two adjacent sinusoidal signals (also known as "two tones") are feed to the nonlinear system input of an LNA, due to the nonlinearity of the circuit the mixing of the harmonics of these signals will produce the  $2^{nd}$ - and  $3^{rd}$ - order inter-modulation products at the output and they may lie within the pass band thus, degrading the desired output signal.

To further investigate the effect of inter-modulation, consider a realistic system with the input-output relation given in Eq. (2.58). Now assume that the input signal has the same amplitude but two closely-spaced sinusoidal components as expressed in Eq. (2.60)

$$\mathbf{x}(\mathbf{t}) = \mathbf{A}(\cos(\omega_1 \mathbf{t}) + \cos(\omega_2 \mathbf{t})) \tag{2.60}$$

Then at the output of the system, the following terms described in Eqs. (2.61) and (2.62) exist in the vicinity of  $\omega_1$  and  $\omega_2$ .

First – order terms:

$$\begin{cases} at \ \omega_1 : y_{\omega_1} = \left(\alpha_1 A + \frac{9}{4}\alpha_3 A^3\right)\cos(\omega_1 t) \\ at \ \omega_2 : y_{\omega_2} = \left(\alpha_1 A + \frac{9}{4}\alpha_3 A^3\right)\cos(\omega_2 t) \end{cases}$$

(2.61)

Third – order IMP terms:

$$\begin{cases} at \ 2\omega_1 - \omega_2 : y_{2\omega_1 - \omega_2} = \left(\frac{3}{4}\alpha_3 A^3\right)\cos(2\omega_1 - \omega_2)t\\ at \ 2\omega_2 - \omega_1 : y_{2\omega_2 - \omega_1} = \left(\frac{3}{4}\alpha_3 A^3\right)\cos(2\omega_1 - \omega_2)t \end{cases}$$

(2.62)

The input point that fundamental signal and IMP have the same output power is called third-order input intercept point depicted in Figure 2.6. Mathematically, this can be expressed in Eq. (2.63).

Figure 2.6: (a) Signal spectrum of a nonlinear system and (b) IIP3 conceptual

interpretation

$$IIP3 = \sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|}$$

(2.63)

These calculations are valid if we assume that in  $y_{\omega 1}$  and  $y_{\omega 2}$  of Eq. (2.62) terms  $(\frac{9}{4}\alpha_3 A^3)$  expressions are negligible. However, this assumption no longer holds at the intercept point where the amplitude of signals is quite large. Therefore, the calculated value of *IIP3* in Eq. (2.63) is just an extrapolation of the small input signal.

## 2.6.3 Linearity Consideration of System Level

Generally a receiver chain consists of several cascaded blocks such as LNA, mixer, VCO etc. Therefore, the overall linearity of a receiver chain

depends on the linearity and gain of each stage. The worst-case *IIP3* of a receiver chain with different gain and *IIP3* of each individual blocks is given as Eq. (2.64) [11].

$$\frac{1}{A_{IIP3,tot}^2} = \frac{1}{A_{IIP3,1}^2} + \frac{\alpha_1^2}{A_{IIP3,2}^2} + \frac{\alpha_1^2 \alpha_2^2}{A_{IIP3,3}^2}$$

(2.65)

where  $A_{IIP3,i}$  and  $\alpha_i$  are the *IIP3* and gain of the *i*-th stage, respectively.

A careful examination of Eq. (2.64) reveals that if each stage in a cascade has a gain greater than unity, then the nonlinearity of the following stage becomes more critical [11]. This means that the nonlinearity of stages after LNA, e.g. mixer(s) have the significant effect on the overall nonlinearity rather than the nonlinearity of LNA. This above equation shows that as the LNA gain increases, the linearity degradation is more and more. As we know by increasing the LNA gain, the NF decreases. Therefore, linearity characteristic is in contrast with the NF scenario and there is a trade-off among linearity and NF. Designers typically try to maximize the LNA gain to get a better NF.

#### **2.7 Input Impedance Matching Network**

To deliver the maximum power from the antenna to the LNA, the input port of the LNA must be matched to the impedance of antenna, e.g.,  $50\Omega$ . For narrowband applications, it's required to match the input impedance of LNA with antenna impedance in a single frequency with very narrow bandwidth. However, for wideband circuits, the impedance matching should be achieved over a wide range of frequency at the LNA input port and is usually a major challenge considering the noise and power consumption requirements.

It is typically to know voltage standing wave ratio (*VSWR*) defined in Eq. (2.6) to measure the degree of the impedance matching [12].

$$VSWR = \frac{1+|\Gamma|}{1-|\Gamma|}$$

(2.65)

where  $\Gamma$  is the reflection coefficient and is defined as Eq. (2.66).

$$\Gamma = \left| \frac{Z - Z_0}{Z + Z_0} \right| \tag{2.66}$$

In this equation,  $Z_o$  is the source characteristic impedance, which generally equals to  $50\Omega$  and Z is the actual input impedance. Perfect matching with  $Z=Z_o$  results in  $\Gamma=0$  (or  $-\infty$  dB) and equivalently VSWR=1.

However  $\Gamma$  should be les than -10dB and it's usually sufficient to meet the matching requirement.

## 2.8 Design Considerations and Analysis

## 2.8.1 Design Considerations and Analysis

The LNA is a crucial component for radio receivers, and it must meet several requirements such as good input matching, adequate gain and reasonably low noise figure to elevate received signal-to-noise ratio as well as energy-efficiency for battery-powered portable devices [13-14]. In the modern wireless communication systems such as WLAN, UMTS, PCS and 4G LTE, due to the large-scaled interference signals at the input port of the LNA, high linearity is an important requirement for broadband receivers. For narrowband LNA design, one may only need high third-order linearity, while for UWB LNA design we need to consider both the second-order and thirdorder distortions due to the large numbers of in-band interferences and the cross-modulation/inter-modulation caused by blockers or transmitter leakage [15].

Several techniques have been proposed to achieve high linearity. The pre-distortion method adds a nonlinear element (also called linearizer) prior

to an amplifier such that the combined transfer characteristic of the two devices is linear. In practice, it is impossible to cancel all orders of nonlinearity simultaneously. Therefore, the linearizer is usually designed to cancel the nonlinearity of a certain order. Optimum gate biasing technique is based on the bias condition of the transistors at zero crossing point. The LNA achieves high linearity but the bottlenecks of this technique are that the bias point is bound to change due to the process variations, and the region which this linearity boost can be obtained is very narrow [16].

The feedforward system has been used in many applications because of its unconditionally stable characteristics and ability to provide a broad-band and highly linear amplifier [17-18]. However, the feedforward technique is very sensitive to component tolerance and drift, and it requires adaptive control [18]. Derivative superposition (DS) is the most favourite linearization technique to achieve high linearity [19-20]. The DS is a special case of the feedforward technique. It consists of two parallel transistors. Main transistor operates in the strong inversion region and the auxiliary transistor operates in the weak inversion region. In DS method, by tuning the sizes and bias conditions of the transistors, the third-order nonlinear transconductance coefficient ( $g_{m3}$ ) can be closed to zero. However, it is not necessary to completely eliminate the second-order nonlinear transconductance coefficient  $(g_{m2})$  contribution from third-order intermodulation (IM<sub>3</sub>). It is noteworthy that since DS method employs multiple transistors in parallel with their gates connected together, it is also called the "multiple gated transistor technique (MGTR)". Since in the DS technique the auxiliary transistor is biased in the triode region, the negative peak magnitude of  $g_{m3}$  is much smaller than the positive peak of the main transistor.

Therefore, the proposed LNA can improve both power gain and linearity in high-data-rate standards such as WiMAX and 4G LTE for handsets, and it can be tuned to the desired frequency band. Examples of applications in include radio frequency these ISM bands process heating and medical diathermy machines. The powerful emissions of these devices can create electromagnetic interference and disrupt radio communication using the same frequency, so these devices were limited to certain bands of frequencies. In general, communication equipment operating in these bands must tolerate any interference generated by ISM equipment, and users have no regulatory protection from ISM device operation.

In the proposed MBDS technique a parallel LC tank is used in the emitter of bipolar transistor to reduce the effect of  $g_{m2}$  on the third-order input

intercept point. Furthermore, MBDS technique is used in the cascode configuration to further reduce the  $g_{m2}$ . By paralleling two capacitances with the gate-to-drain and base-to-collector capacitances of the MOS and bipolar transistors, the phase of  $g_{m3}$  can be adjusted respectively, and then the *IIP3* of the whole LNA can be enhanced. The proposed LNA has several applications such as UMTS, PCS and 4G LTE.

#### 2.8.2 Design Considerations and Analysis

## 2.8.2.1 Fundamentals

In transistors the major factor for nonlinear behavior of the RF blocks is the nonlinear voltage-current relationship, and it is further degraded as the scaling down of the technology. The voltage-current relationship of transistors is expressed as Eq. (2.67).

$i = g_{m1}v + g_{m2}v^2 + g_{m3}v^3$ (2.67)

where  $g_{mi}$  (*i*=1,2,3) is the *i*<sup>th</sup>-order nonlinear coefficient.

The *IIP3* is the most important parameter for monitoring the linearity performance of the whole LNA circuit and it is expressed as in Eq. (2.63) [18].

Therefore,  $g_{m3}$  is the main source of non-linearity in LNAs and by cancelling out it, the linearity can be enhanced. The Taylor expansion series of bipolar transistor can be approximated Eqs. (2.68) and (2.69).

$$i_{CE} = \alpha_1 v_{be} + \alpha_2 v_{be}^2 + \alpha_3 v_{be}^3$$

(2.68)

$$i_{CE} = I_{S0}e^{\frac{V_{BEQ} + v_{be}}{\varphi_t}} = I_{S0}e^{\frac{V_{BEQ}}{\varphi_t}}e^{\frac{v_{be}}{\varphi_t}} = I_Qe^{\frac{v_{be}}{\varphi_t}}$$

(2.69)

where  $V_{BEQ}$  is the base-to-emitter bias voltage,  $I_{S0}$  is saturation current, and  $\varphi_t$  is the thermal voltage. The third-order coefficient can be written as Eq. (2.70).

$$\alpha_3 = \frac{I_Q}{6\varphi_t^3} \tag{2.70}$$

According to Eq. (2.70),  $\alpha_3$  has positive value due to the exponential relationship between the collector current and base-to-emitter voltage. For MOS transistor with negative third-order coefficient the voltage-current relationship is as described in Eqs. (2.71) to (2.74):

$$i_{DS} = \beta_1 v_{gS} + \beta_2 v_{gS}^2 + \beta_3 v_{gS}^3$$

(2.71)

$$i_{DS} = K \frac{x^2}{1+\theta x} \tag{2.72}$$

$$x = 2\eta\phi_t \ln(1 + exp(\frac{V_{gs} - V_{th}}{2\eta\phi_t}))$$

(2.73)

$$\beta_3 = -\frac{\theta K}{(1+\theta V_{eff})^4} \tag{2.74}$$

where  $K = 0.5\mu_o C_{ox}W/L$ ,  $\mu_0$  is the mobility,  $C_{ox}$  is the gate capacitance per unit area,  $\theta$  is the normal field mobility degradation factor,  $V_{eff} = V_{gs0} - V_{th}$ , and  $V_{gs0}$  is the gate source dc bias voltage.

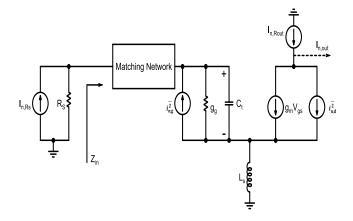

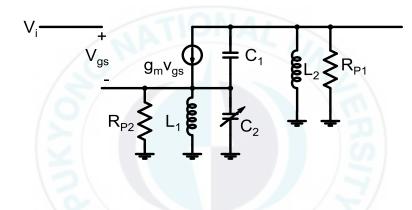

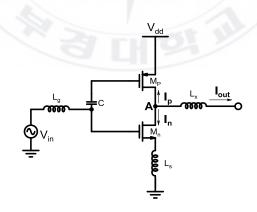

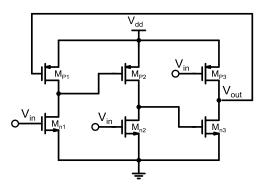

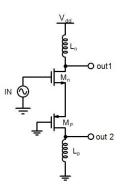

Figure 2.7 shows schematic of proposed LNA using MBDS technique. As can be seen from Figure 2.7, the bipolar current can be added to the MOS current at the output port to cancel out the  $g_{m3}$  of the entire LNA. The output current is expressed as Eq. (2.75).

$$i_{out} = i_{DS} + i_{CE} = (\alpha_1 + \beta_1)v_{in} + (\alpha_2 + \beta_2)v_{in}^2 + (\alpha_3 + \beta_3)v_{in}^3$$

$$= g_{m1}v_{in} + g_{m2}v_{in}^2 + g_{m3}v_{in}^3$$

(2.75)

From Eq. (2.71) to Eq. (2.75) it appears that the sign of  $\beta_3$  and  $\alpha_3$  is opposite. To get maximum cancellation of third-order term, the magnitude of  $\beta_3$  and  $\alpha_3$  must be equal. The third-order term of bipolar transistor is usually more than  $\beta_3$  of MOS transistor. At the resonance frequency, the emitter LC tank shows a resistance which is used to optimize the value of  $\alpha_3$  and hence

to achieve high linearity. The phase and magnitude of  $g_{m3}$  in Eq. (2.75) are dependent on the biasing and the size of the transistors. By tuning the sizes and bias conditions of the transistors, the phase and magnitude of third-order nonlinear transconductance coefficient can be closed to zero.

Figure 2.7: Schematic of the proposed LNA

#### 2.8.2.2 Nonlinear Base Capacitance in Bipolar Transistor

Although the bipolar transistor has power-handling capabilities, it has highly nonlinear capacitance at the base junction [9]. This capacitance results in a large second-order harmonic, and it degrades the linearity performance.

A parallel LC tank ( $L_E$ ,  $C_E$ ) in Figure 2.7 is used in the emitter of bipolar transistor ( $T_I$ ) resonating at the second harmonic of fundamental tone to

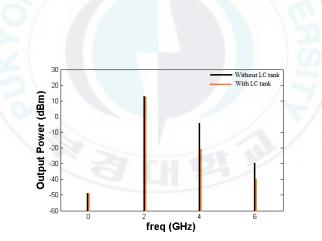

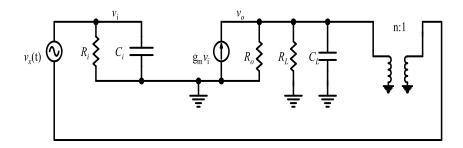

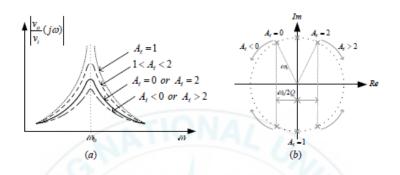

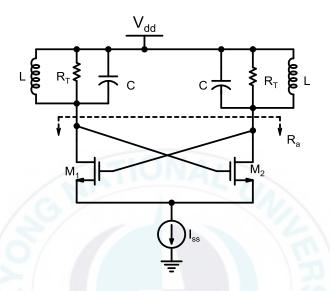

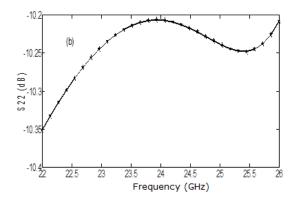

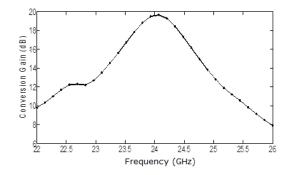

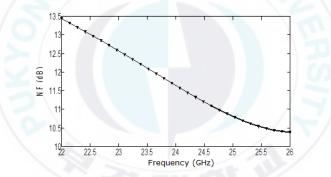

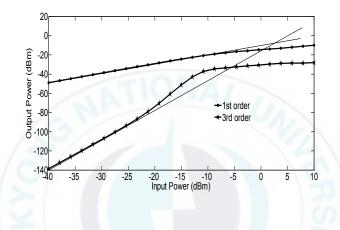

overcome the degradation of base capacitance. The LC network is employed as source degeneration circuit, and it decreases the current at 4GHz. Since the  $L_E$  degenerates the fundamental tone which results in a lower power, the inductor ( $L_E$ ) should be chosen enough small. The  $L_E$  also should be small to have a high quality factor (Q), since the gain does not drop greatly. Thus, the values of the  $L_E$  and  $C_E$  are chosen to be 0.14nH and 11.2pF, respectively.