## 공학석사 학위논문

# 부궤환 역할을 하는 커패시터를 포함한 두 개의 부궤환 위상고정루프

전 자 공 학 과

박 종 윤

## 공학석사 학위논문

# 부궤환 역할을 하는 커패시터를 포함한 두 개의 부궤환 위상고정루프

지도교수 최 영 식 이 논문을 공학석사 학위논문으로 제출함

2014 년 2 월

부 경 대 학 교 대 학 원

전 자 공 학 과

박 종 윤

# 박종윤의 공학석사 학위논문을 인준함

2014 년 2 월

주 심 공학박사 최 혁 환 (인)

위 원 공학박사 최영식 (인)

위 원 공학박사 권 태 하 (인)

# 목 차

# Abstract

| I . 서론1                                              |

|------------------------------------------------------|

| Ⅱ. 위상고정루프의 기본 이론 ··································· |

| Ⅱ. 위상고정루프의 기본 이론3                                    |

| 2.1 위상고정루프의 구조 및 이론4                                 |

| 2.2 기본 블록들의 동작특성5                                    |

| 2.2.1 위상 검출기7                                        |

| 2.2.2 전하펌프와 루프필터9                                    |

| 2.2.3 전압 제어 발진기10                                    |

| 2.2.4 주파수 분주기10                                      |

| 2.3 전하펌프 위상 고정 루프의 선형적 분석11                          |

|                                                      |

| Ⅲ. 부궤환 역할을 하는 커패시터를 포함한 두 개의 부궤환 위상고                 |

| 정루프 설계16                                             |

| 3.1 제안한 위상고정루프의 구조16                                 |

| 3.2 부궤환 역할을 하는 커패시터 해석17                             |

| 3.3 잡음 해석22                               |

|-------------------------------------------|

| 3.4 회로 설계27                               |

| 3.4.1 위상-주파수 검출기27                        |

| 3.4.2 전하 펌프29                             |

| 3.4.3 전압제어 발진기31                          |

| 3.4.4 주파수-전압 변환기33                        |

| 3.4.5 주파수 분주기36                           |

| 3.5 루프필터 스위치 타이밍에 대한 고찰37                 |

| 3.5.1 스위치 타이밍의 영향37                       |

| 3.5.2 공정변화에 대한 스위치 타이밍39                  |

|                                           |

| IV. 시뮬레이션 결과                              |

| 4.1 시뮬레이션 결과42                            |

| अ टा छा गा                                |

| V. 결론 ··································· |

|                                           |

| 참고문헌48                                    |

A phase-locked loop having two negative-feedback loops involving a capacitor working effectively as the negative-feedback function.

Jong-yoon Park

Department of Electronic Engineering, Graduate School,

Pukyong National University

#### **Abstract**

In this thesis, We propose a phase-locked loop having negative-feedback loops involving a capacitor working effectively as the negative-feedback function. A behavior of the capacitor, which is controlled by a switch operated by high frequency signal, dramatically suppress reference spur and also improve a phase noise characteristic. A frequency-voltage converter is introduced to make the PLL more stable, resulting in much better phase noise characteristic. The proposed phase-locked loop has been fabricated in a 0.18µm CMOS process and proved by HSPICE simulation.

# I. 서 론

현대 무선통신 시스템을 비롯한 이동통신 기기 등과 같은 디지털 제품에는 고성능의 주파수 합성기를 필요로 한다. 주파수 합성기로 널리 사용되고 있는 위상고정루프의 경우 빠른 고정시간, 넓은 대역폭, 그리고 좋은 잡음특성이 요구된다. 또한 한정된 통신 주파수를 효과적으로 사용하기 위해서는 다른 채널에 영향을 미치는 기준 주파수 의사 잡음을 최소화 하는 것도점점 중요해 지고 있다. 기준 주파수 의사 잡음은 전하펌프의 전류량과 전압제어 발진기의 이득을 감소시켜 줄일 수 있지만, 루프 대역폭이 증가하고 위상고정루프의 고정시간이 증가하게 된다.

위상고정루프의 이러한 특성을 극복하여 기준 주파수 의사 잡음을 줄이기 위한 연구들이 활발하게 진행되고 있으며 다양한 구조들이 제안되었다. 일반적으로 전하펌프 구조 개선을 통해 전류 부정합을 최소화 시켜 기준 주파수 의사 잡음을 줄이는 구조가 사용된다[1]~[3]. 이 구조에서는 여러 개의 op-amp를 사용하여 전류 부정합을 줄일 수 있지만 설계가 복잡하고, 칩의면적이 커지며, 전력 소비가 증가하게 된다. [4]는 여러 개의 위상주파수 검출기와 전하펌프 쌍을 사용하여 각 쌍들은 정확히 ΔΤ시간 뒤에 동작하도록한 구조이다. 하지만 딜레이 셀은 공정, 온도(PVT) 변화에 민감하기 때문에 정확한 시간만큼 지연시키기가 상당히 어렵다. 또 다른 방법으로는 전류 부정합에 의해 발생하는 전하가 루프필터로 유입되는 시간을 분산 시켜 기준주파수 의사 잡음을 줄인 구조도 발표되었다[5][6]. [5]은 스위치 커패시터를 사용하여 전하펌프로부터 유입된 전하를 저장한 다음 몇 번에 걸쳐 루프필터로 전하를 이동시키는 구조를 보여주고 있다. 스위치 커패시터에 의해 기

준 주파수 의사 잡음은 줄었지만, 스위치 동작마다 클록피드스루와 전하공유 현상이 루프필터 전압에 발생하게 된다. [6]의 경우 지연고정루프를 기반으로 한 edge interpolator를 사용한다. edge interpolator는 기준 신호와 피드백 신호를 입력으로 받아 각각의 신호를 지연고정루프를 통해 고주파의신호로 변화시켜 위상-주파수 검출기의 입력으로 전달한다. 지연 고정 루프를 사용한 정확히 지연시간이 계산된 신호의 발생은 일반적인 딜레이 셀을사용한 경우 보다 공정, 온도(PVT)변화에 덜 민감 할 수 있다. 하지만 기준신호와 피드백신호 경로에 위치하는 두개의 지연고정루프 사이에 전압 제어 지연 단 비대칭 문제가 발생하면 기준 주파수 의사 잡음 억제를 기대하기 어렵다.

본 논문에서는 기준 주파수 의사 잡음을 줄이기 위해 부궤환 역할을 하는 커패시터를 포함한 루프팰터를 사용하여 간단하게 기준 주파수 의사 잡음을 줄일 수 있음을 보여준다. 또한 주파수-전압 변환기를 함께 사용하여 잡음특성 또한 획기적으로 향상시킬 수 있음을 보여 준다. 제안된 구조는 루프필터에 스위치가 사용되기 때문에 [5]의 구조와 마찬가지로 클록피드스루와 전하공유 현상이 발생하게 된다. 하지만 본 구조의 스위치는 고주파의 출력주파수에 의해 동작하기 때문에 이 현상에 대한 영향은 출력 주파수 대역에서 멀리 떨어진 주파수 대역에서 발생한다. 따라서 위상고정루프의 성능에 영향을 미치지 못한다. 또한 위상고정 루프 출력 신호로 스위치를 제어하기 때문에 추가되는 회로가 없어 설계가 용이하다. 제안한 위상고정루프는 0.18µm CMOS 공정을 사용하여 HSPICE 시뮬레이션을 통해 결과를 검증하였다.

# Ⅱ. 위상고정루프의 기본 이론

### 2.1 위상고정루프의 구조 및 이론

주파수 합성기 또는 클록 신호 생성기를 구현하는 방법에는 여러 가지가 제안되어 왔다. 그중에 가장 보편적으로 사용하는 방법이 위상 고정 루프(PLL: Phase-Locked Loop)를 이용 하는 것인데, 그 이유는 위상 고정루프는 낮은 위상잡음, 낮은 스퍼 분포 등 여러 가지 장점을 가지고 있기때문이다.

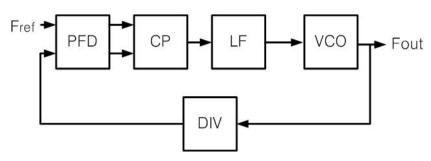

위상 고정 루프는 기준 주파수에 대해 주파수와 위상이 같은 신호를 만들어 내는 회로이다. 위상 고정 루프의 여러 특성 중 위상 고정루프로서 위상 고정 루프의 동작특성을 나타내는 지표는 위상잡음(phase noise), 위상 고정 시간, 스퍼 등이 있다. 이들 모두 위상 고정 루프의 대역폭에 의해 영향을 받는다. 대역폭이 넓어지면, 위상 고정 시간은 짧아지나 잡음특성이나빠지고, 대역폭이 줄어들면 반대의 효과가 나타나는 상충 관계이다. 대역폭은 위상 고정 루프에 인가되는 기준 주파수에 의존한다. 본 논문에서 다루고 있는 위상 고정 루프는 전하 펌프 위상 고정 루프로 기본적인 블록다이어그램은 그림2.1과 같다.

그림 2.1 기본 위상 고정 루프 블록 다이어그램

위상 고정 루프는 위상 주파수 검출기(PFD), 전하 펌프(CP), 루프 필터 (LF), 전압 제어 발진기(VCO), 주파수 분주기(DIV)의 주요 부분으로 나누어져 있다. 위상 고정 루프의 동작을 살펴보면, 위상 주파수 검출기는 외부로부터 입력되는 기준 주파수 신호와 전압 제어 발진기에서 생성되는 신호의 위상과 주파수를 비교하여 위상 및 주파수의 차이에 해당하는 신호를 출력하여 전하 펌프를 구동한다. 전하 펌프는 입력 신호의 펄스폭에 비례하는 전류를 구동하여 루프 필터의 커패시터를 충전 또는 방전시킴으로써 전압 제어 발진기의 출력신호와 위상을 기준 주파수의 위상과 주파수에 동일하게 만드는 전압 제어 발진기의 제어전압을 발생시킨다.

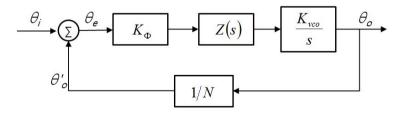

위상 고정 루프가 위상 고정되는 과정은 비선형적 과정이지만 위상 고정된 후에는 위상 고정 루프를 선형 모델링 할 수 있다. 그림2.2는 위상 고정상태에서 위상 고정 루프의 선형모델을 나타낸다.

그림 2.2 위상 고정 상태에서의 위상 고정 루프 선형 모델

#### 2.2 기본 블록들의 동작특성

#### 2.2.1 위상 주파수 검출기 (phase frequency detector)

일반적으로 두 클록의 위상을 비교하는 블록은 위상 주파수 검출기 이다. 이 위상 주파수 검출기의 특성에 따라 정적 스큐, bang-bang 지터 등의 크기가 결정된다. 가장 쉽게 생각할 수 있는 것은 D Flip-Flop을 위상주파수 검출기로 생각하는 것인데 이 경우 D Flip-Flop의 셋/홀드 시간만큼의 불확실 영역이 있어 이로 인해 지터가 증가할 수 있고, 위상 오차가양(+)인지 (-)인지만 판단하기 때문에 bang-bang 지터가 발생할 수 있는 단점을 가진다.

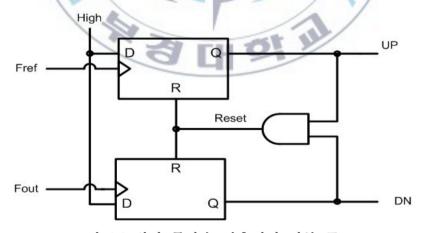

현재는 위상과 주파수 차이를 동시에 검출하는 순차회로인 3-상태 (3-state) 위상 주파수 검출기 구조가 가장 보편적으로 사용되고 있다. 그림 2.3는 3-상태 위상 주파수 검출기의 구조를 나타낸다.

그림 2.3 위상 주파수 검출기의 기본 구조

3-상태 위상 주파수 검출기는 2개의 D Flip-Flop과 1개의 AND 게이트로 구성되어 있다. 이 구조는 edge-triggered 순차회로로 2개의 D Flip-Flop의 입력으로 기준 주파수 신호(Fref)와 전압 제어 발진기(VCO)의 출력 주파수 신호 (Fout)의 이행 조건에 따라 동작하기 때문에 두 입력 신호의 듀티비(duty ratio)에 대해 무관한 특성을 나타낸다.

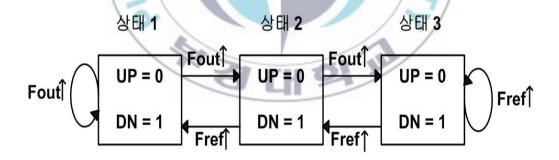

그림 2.4는 3-상태 위상 주파수 검출기의 상태도를 나타낸다. 위상 주파수 검출기는 기준 신호와 전압 제어 발진기의 출력신호의 위상 차이에 비례하는 폭을 가진 출력 펄스를 생성하고, 두 입력 중 빠른 위상을 가진 입력이 어떤 것인가에 따라 UP, DN 펄스를 출력 신호로 내보낸다.

예를 들어, 기준 신호가 전압 제어 발진기의 출력 신호보다 위상이 빠르다고 하면, 그 위상차에 해당하는 펄스폭을 가지는 UP 신호를 출력한다. 반대로 기준 신호가 전압 제어 발진기의 출력 신호보다 위상이 느리다고하면, 마찬가지로 그 위상차에 해당하는 DN 신호를 출력한다.

그림 2.4 위상 주파수 검출기의 상태도

위상주파수 검출기의 출력 UP 신호는 전하펌프를 구동시켜 루프필터의 커패시터를 충전하여 전압을 상승시킨다. 마찬가지로 DN 신호는 루프필터 의 충전된 전하를 방전하여 전압을 하강시킨다. 기준신호와 전압 제어 지연단의 출력 신호가 같아지면 이상적인 경우 위상주파수 검출기의 출력인 UP, DN 신호가 없고, 이에 따라 전하펌프의 구동이 없게 된다. 그리고 전하펌프의 전류 구동이 없기 때문에 루프필터의커패시터에 충전, 방전이 없게 되므로, 전압 제어 발진기의 입력제어전압은항상 일정한 값을 유지하게 된다. 그러나 실제의 경우, 위상주파수 검출기의 D Flip-Flop의 리셋 시간에 의해 리셋 펄스가 생성된다.

위상 주파수 검출기에 입력되는 두 입력 위상간의 위상차를  $\Delta \Theta$ 라디안이라 하면, 위상 주파수 검출기는 주기가  $1/f_{PFD}$  이고 펄스의 크기가 (duration)  $|\Delta \theta|/\omega_{PFD} (= 2\pi f_{PFD})$  인 펄스를 발생시킨다. 전하펌프의 전류가  $I_p$ 라 할 때, 이는 전하펌프에 인가되어 한 주기 당  $I_p \Delta \theta/2\pi$ 의 전류를 루프필터에 전달해 준다. 이를 루프필터는 전압으로 바꾸어 주는 역할을 한다. 이를 수식으로 표현하면 식2-1과 같다.

$$V_{cont}(s) = \frac{1}{2\pi} \cdot I_p \cdot G_{LF}(s) \cdot \Delta\theta(s)$$

(2-1)

위의 수식에서  $V_{cont}$  는 루프필터의 출력 전압이며,  $G_{LF}$  는 루프필터의 전달함수이다.

#### 2.2.2 전하 펌프와 루프 필터

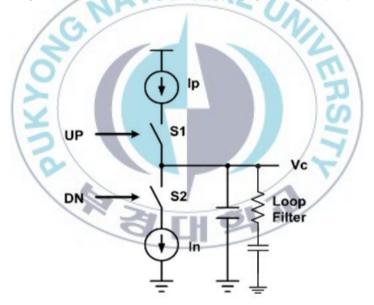

그림 2.5는 위상 고정 루프에서 사용되는 전하펌프(CP: Charge Pump) 와 루프필터(LF: Loop filter)의 구성을 나타낸다. 전하펌프는 위상 주파수 감지기의 출력인 UP, DN 신호를 입력으로 받아서 전류를 공급하거나 빼는 역할을 한다. 전하펌프는 전류원, 싱크(sink) 그리고 UP, DN 신호에 의해 전류원을 ON/OFF 시키는 스위치로 구성된다. 전하펌프의 UP, DN 동작에 의한 전류 공급은 위상 고정 루프 특성에 매우 중요한 역할을 하는데이는 위상 고정 루프 출력 주파수의 지터에 영향을 끼치기 때문이다.

그림 2.5 전하펌프와 루프필터

전하펌프의 동작을 살펴보게 되면 UP신호가 'high'일 경우 전하펌프의  $S_1$  스위치가 'turn on'이 되어 루프필터에 전류  $I_P$ 가 흐르게 되고, 이 루프필터의 커패시터에 전하가 충전되어, 전압 제어 발진기의 입력제어전압인  $V_C$  전압이 서서히 상승하게 된다. 반대로, DN 신호가 'high'일 경우 전하

펌프의  $S_2$  스위치가 'turn on'되어 루프필터에 전류  $I_N$ 이 흐르게 되고, 루프필터의 커패시터에 충전되어 있던 전하가 방전되어 전압 제어 발진기의 입력제어전압인  $V_C$ 가 서서히 하강하게 되는 메커니즘을 갖는다.

또한 위상 고정 상태에서 리셋 시간에 스위치  $S_1$ ,  $S_2$ 가 동시에 'turn on'되어 접지로 전류 경로가 형성되므로, 루프필터의 커패시터의 충전, 방전이 없게 된다. 따라서 전압 제어 발진기의 입력제어전압의 변동 없이 일정한 값을 갖게 된다.

전하펌프에 사용되는 스위치 소자는 MOSFET으로 스위치  $S_1$ 의 경우는 P형 MOSFET, 스위치  $S_2$ 의 경우는 N형 MOSFET을 사용하게 된다. 지연고정루프가 위상 고정이 된 경우, 전하펌프에 흐르는 전류량  $I_P$ ,  $I_N$ 의 크기는 같아야 한다. 그러나 스위치로 사용되는 P형 MOSFET, N형 MOSFET 소자의 이동도 차이, 위상주파수 검출기의 출력인 UP, DN신호에 의한 스위치 'turn on' 시간차이, MOSFET 스위치의 클록 피드스루(Clock Feedthrough), 전하공유(Charge Sharing)에 따른 전류 미스매치(mismatch)가 발생한다.

이러한 요소들에 의해 발생하는 전류 미스매치는 전압 제어 발진기의 입력제어전압이 출렁거리는 원인이 되고, 궁극적으로 지터를 발생하게 하는 주요 원인이 된다.

#### 2.2.3 전압 제어 발진기 (voltage controlled oscillator)

전압 제어 발진기는 입력전압에 비례하는 주파수를 발생하는 블록으로, 그 수식은 식2-2와 같다.

$$\omega_{out} = \omega_{free} + K_{vco} \cdot V_{cont} \tag{2-2}$$

위의 수식에서  $\omega_{free}$  는  $V_{cont}$  전압이 인가되지 않았을 경우의 전압 제어 발진기 자주 주파수(free running frequency),  $K_{VCO}$  는 전압 제어 발진기의 이득을 의미한다. 위의 수식에서 전압 제어 발진기의 전달함수를 구하면 다음과 같다.

$$\Phi_{out}(s) = \frac{1}{s} \cdot K_{vco} \cdot V_{cont}$$

(2-3)

#### 2.2.4 주파수 분주기(Divider)

출력 주파수를 입력 기준 주파수에 비해 높은 주파수를 가지도록 하기 위해서는 전압 제어 발진기의 주파수를 그대로 사용하지 못하고, 주파수 분주기를 이용해서 주파수를 분주하게 된다. 이때 사용되는 주파수 분주기 의 특성에 따라 정수비, 분수비 방식으로 나누어진다.

## 2.3 전하펌프 위상 고정 루프의 선형적 분석

루프의 동작특성을 s-domain에서 분석하면 개루프 전달함수와, 폐루프 전달함수는 식2-4 와 식2-5 같이 나타낼 수 있다.

$$H_{open} = K_{PFD} \cdot \frac{K_{VCO}}{s} \cdot G_{LF}(s) \tag{2-4}$$

$$H_{closed}(s) = \frac{K_{PFD} \cdot K_{VCO} \cdot G_{LF}(s)}{s + K_{PFD} \cdot K_{VCO} \cdot G_{LF}(s)}$$

(2-5)

위의 수식을 바탕으로 위상 고정 루프의 개루프 전달함수는 식2-6과 같 고, 폐루프의 전달함수는 식2-7로 나타낸다.

$$\frac{\theta_o(s)}{\Delta\theta(s)} = \frac{1}{2\pi} \cdot I_p \cdot G_{LF}(s) \cdot \frac{K_{VCO}}{s}$$

(2-6)

$$\frac{\theta_o(s)}{\Delta\theta(s)} = \frac{1}{2\pi} \cdot I_p \cdot G_{LF}(s) \cdot \frac{K_{VCO}}{s} \qquad (2-6)$$

$$\frac{\theta_o(s)}{\theta_i(s)} = \frac{\frac{K_{VCO}}{s} \cdot \frac{I_p}{2\pi} \cdot G_{LF}(s)}{1 + \frac{K_{VCO}}{s} \cdot \frac{I_p}{2\pi} \cdot G_{LF}(s)}$$

$G_{LF}(s)$  는 루프 필터의 전달함수를 나타내고, 저역 통과 필터가 사용된 다.

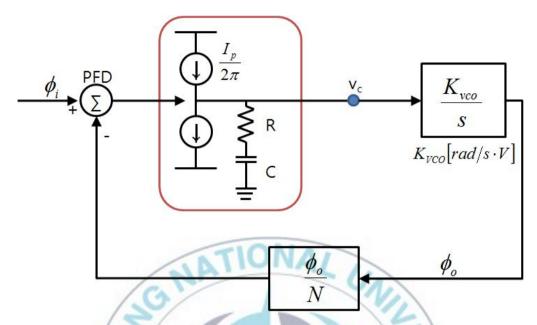

그림 2.6 2차 구조의 전하펌프 위상고정루프

그림 2.6은 루프필터에서 1차의 전달함수를 가지고 전압제어발진기에서 1차의 전달함수를 지니는 가장 기본적인 위상고정루프를 보인 것이다. 이 구조는 식2-7을 이용하여 전개하면 식2-8과 같이 나타난다.

$$\frac{\phi_o}{\phi_i} = \frac{N\left(\frac{1}{N} \cdot \frac{I_p}{2\pi} \cdot R \cdot K_{VCO} \cdot s + \frac{1}{N} \cdot \frac{I_p}{2\pi} \cdot K_{VCO} \cdot \frac{1}{C}\right)}{s^2 + s \cdot \frac{1}{N} \cdot \frac{I_p}{2\pi} \cdot R \cdot K_{VCO} + \frac{1}{N} \cdot \frac{I_p}{2\pi} \cdot K_{VCO} \cdot \frac{1}{C}}$$

$$= \frac{2\zeta \omega_n \cdot s + \omega_n^2}{s^2 + 2\zeta \omega_n \cdot s + \omega_n^2}$$

(2-8)

그림 2.6과 같은 구조는 저항의 성분이  $I_P$ 에 의해 빠른  $V_C$  전압의 변화를 보이므로 전체 위상 고정 루프의 출력에 원치 않는 신호(spur)가 크게 나타나는 등의 문제가 많이 발생하므로 거의 사용하지 않는 구조이다.

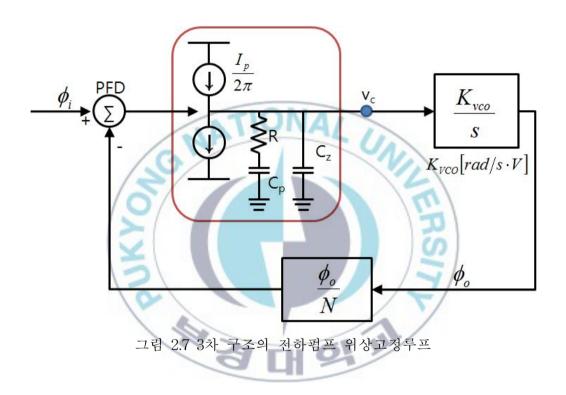

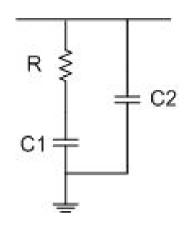

이에 비해 그림 2.7과 같이 2차 필터를 사용하여 3차의 루프를 구성하는 경우는 스퍼의 감소와 안정성을 기대 할 수 있다. 전달 함수에 있어서 2차 필터를 사용하면 두 개의 극점은 원점에 존재하고 나머지 하나의 극점과한 개의 영점을 이용하여 위상 마진을 고려하여 루프의 안정성을 보장하게하고, 대역폭을 조절하게 된다. 2차 필터는 그림 2.8과 같다.

그림 2.8 2차 루프 필터

2차 필터를 이용한 전체 위상 고정 루프의 개루프와 폐루프의 전달함수 를 구하면 다음과 같다.

$$H_{open}(s) = \frac{1}{2\pi} \cdot I_p \cdot \frac{1 + s \cdot R \cdot C_1}{s(C_1 + C_2) + s^2 \cdot R \cdot C_1 \cdot C_2} \cdot \frac{K_{VCO}}{s}$$

(2-9)

$$H_{closed}(s) = \frac{K_{VCO} \cdot I_p \cdot (1 + s \cdot R \cdot C_1)}{K_{VCO} \cdot I_p + K_{VCO} \cdot I_p \cdot R \cdot C_1 \cdot s + 2\pi (C_1 + C_2) s^2 + 2\pi \cdot R \cdot C_1 \cdot C_2 \cdot s^3} \quad (2-10)$$

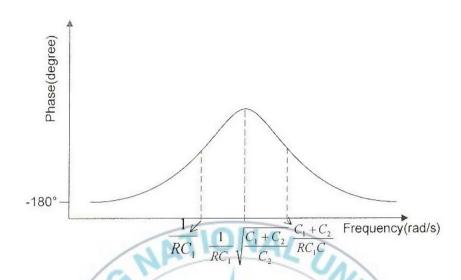

위의 식2-9에서 원점에 2개의 극점이 존재하고,  $\frac{C_1+C_2}{R\cdot C_1\cdot C_2}$  에 극점이 하나 존재하고,  $\frac{1}{R\cdot C_1}$ 에 하나의 영점이 존재한다. 위의 개루프 전달함수에 대한 위상에 대한 보드선도를 그리면 그림 2.9와 같다.

그림 2.9 3차 위상 고정 루프의 위상특성

루프 필터의 차수에 따라, 그리고 R과  $C_1$ ,  $C_2$ 의 값에 따라 위의 식의 특성이 달라지므로 원하는 대역폭과 안정성을 고려하여 필터를 설계해야 한다.

# Ⅲ. 부궤환 역할을 하는 커패시터를 포함한 두 개의 부궤환 위상고정루프 설계

### 3.1 제안한 위상고정루프의 구조

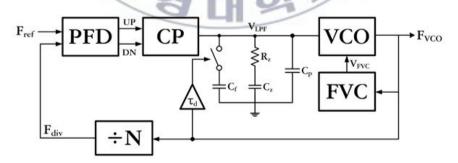

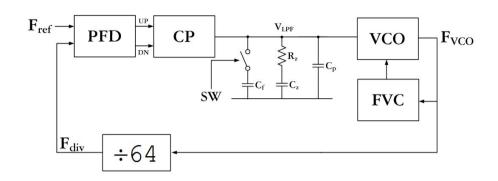

본 논문에서 제안한 위상 고정 루프 구조가 그림 3.1에 나타나 있다. 제안한 구조는 위상-주파수 검출기, 전하펌프, 일반적인 위상고정루프에 사용하는 2차 루프필터에 스위치와 커패시터가 추가된 루프필터, 전압제어 발진기, 주파수-전압 변환기(FVC: Frequency to Voltage Converter), 그리고 분주기로 구성 된다. 일반적인 2차 루프필터를 가진 위상고정 루프는하나의 부궤환을 가진다. 제안된 구조는 주파수-전압 변환기를 통해 또 하나의 부궤환 루프가 추가된 구조이며, 부궤환 효과를 제공하는 커패시터가추가된 루프필터를 사용한다. 이 커패시터는 높은 주파수를 가지는 출력신호에 의해 동작하는 스위치로 인해 제어된다.

그림 3.1 제안한 위상고정루프의 구조

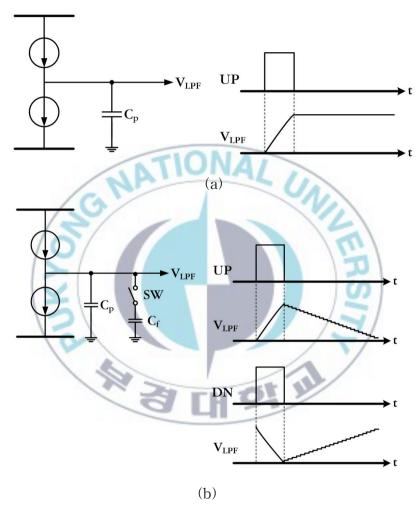

#### 3.2 부궤환 역할을 하는 커패시터 해석

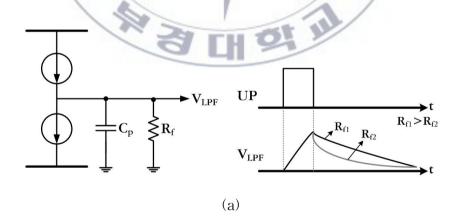

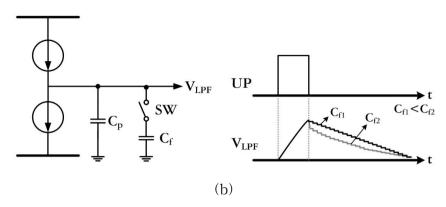

기존 위상고정루프에 그림 3.2(a)와 같이 하나의 커패시터로 구성된 루프 필터를 연결하면 두 개의 극점만 존재하여 위상고정루프가 불안하게 동작하여 위상고정이 되지 않는다. 그림 3.2(a)와 같이 하나의 커패시터로 구성된 루프필터에 그림 3.2(b)와 같이 스위치와 또 하나의 커패시터를 연결하면 안정하게 동작한다. 그림 3.2(b)는 UP/DN 신호에 따른 루프필터 전압의 변화를 나타내고 있다. 여기에 사용된 스위치의 동작 속도는 위상고정루프에 포함되어 있는 전압제어 발진기의 출력신호이다. 이 신호는 기준주파수 보다 아주 높은 주파수 이다. 루프필터 출력전압이 증가하면 추가된스위치와 커패시터에 의해 루프필터 출력전압은 기준신호 한 주기에 걸쳐 감소하며, 루프필터 출력 전압이 감소하면 기준신호 한 주기에 걸쳐 증가하게 된다. 추가 된 스위치와 커패시터에 의해 루프필터 출력전압은 부궤환을 가진 것처럼 동작하게 된다.

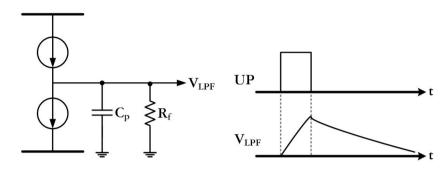

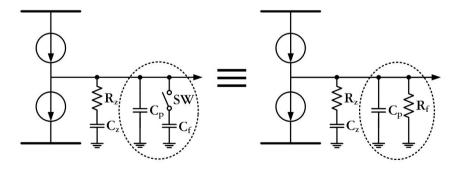

그림 3.3은 루프필터에 부궤환 효과를 제공하는 스위치와 커패시터를 저항으로 모델링 한 그림이다. 기준신호 한 주기 동안 발생하는 루프필터 출력 신호의 변화가 모델링 전과 동일함을 확인 할 수 있다. 그림 3.3의 루프필터의 전달함수를 구하면 식(3-1)과 같다.

$$LF(S) = \frac{1}{C_p} \cdot \frac{1}{S + 1/R_f C_p}$$

(3-1)

하나의 커패시터로 구성된 루프필터에 존재했던 원점의 극점이 저항에 의해 높은 주파수 대역으로 이동하게 된다. 따라서 위상고정루프가 안정적 인 동작이 가능하게 해준다. 또한  $R_t$ 가 작을수록 극점은 더욱 높은 주파수

대역으로 이동하여 위상고정루프는 더욱 안정적으로 동작한다.

그림 3.2 (a) 하나의 커패시터로 구성된 루프필터 (b) 부궤환 역할을 하는 커패시터가 포함된 루프필터

그림 3.3 저항으로 모델링된 부궤환 역할을 하는 커패시터

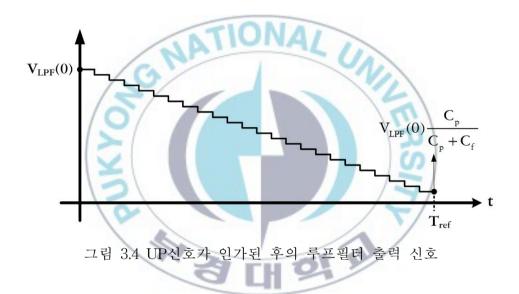

그림 3.4는 UP신호가 인가된 후 루프필터 출력 신호의 모양을 나타낸다. 이 경우 루프필터 출력신호  $V_{\mathrm{LPF}}(t)$ 를 나타내면 다음과 같다.

$$V_{LPF}(0) = \frac{I_p \cdot t_{up}}{C_p} \tag{3-2}$$

$$V_{LPF}(t) = V_{LPF}(0) \cdot e^{-\frac{1}{C_p R_f} t}$$

(3-3)

이때 Ip는 전하펌프의 전류량 이고,  $t_{up}$ 은 UP신호가 발생된 시간이다. 위식을 이용하여  $R_f$ 의 값을 구하면 식(3-4)과 같다.

$$R_f = \frac{T_{ref}}{C_p} \cdot \frac{1}{-\ln\left(\frac{C_p}{C_p + C_f}\right)}$$

(3-4)

그림 3.5(a)는  $R_f$  크기에 따른 루프필터 출력신호의 변화를 나타내고, 그림 3.5(b)는  $C_f$ 크기에 따른 루프필터 출력신호의 변화를 나타낸다. 그림 3.5(b)에 나타난 바와 같이  $C_f$ 가  $C_p$ 에 비해 크면 클수록 위상고정루프는 더욱 안정적인 동작이 가능하다. 이는 기준신호 한 주기( $T_{ref}$ ) 동안 발생하는 전체 위상변화(루프필터 출력신호의 면적)가 작아지는 것을 나타낸다.  $C_f$ 가 크다는 것은  $R_f$ 가 작은 것을 의미함으로,  $R_f$ 가 작을수록 위상고정루프가 안정된다는 것과 같다.

그림 3.5 (a) $R_f$  크기에 따른 루프필터 출력 신호의 변화 (b) $C_f$  크기에 따른 루프필터 출력 신호의 변화

그림 3.6은 제안된 구조의 루프필터 구조로서 기존 2차 루프필터에 부궤 환 역할을 하는 커패시터를 추가한 루프필터를 나타낸다.

위와 같은 방법으로 부궤환 역할을 하는 커패시터를 저항으로 모델링하여 그 전달함수를 구하면 식(3-5)과 같다.

$$LF(S) = \frac{1}{C_p} \bullet \frac{S + \frac{1}{R_z C_z}}{S^s + S \frac{C_p R_f + C_z R_z + C_z R_f}{C_p C_z R_z R_f} + \frac{1}{C_p C_z R_z R_f}}$$

(3-5)

그림 3.6 제안된 루프필터 모델

## 3.3 잡음 특성

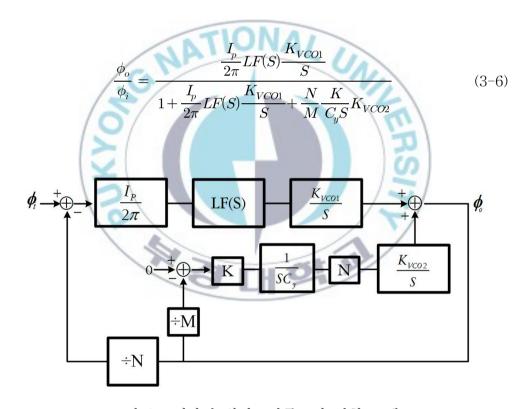

그림 3.7은 제안된 위상고정루프의 선형 모델이다. 선형 모델을 이용하여 위상고정루프의 폐루프 전달함수를 구하면 다음과 같다.

식 (6)의 LF(S)는 루프필터의 전달함수,  $K_{VCO1}$ 은 루프필터 출력에 대한 전압제어 발진기의 이득,  $K_{VCO2}$ 는 주파수-전압 변환기 출력에 대한 전압제어 발진기의 이득이다.

그림 3.7 제안된 위상고정루프의 선형 모델

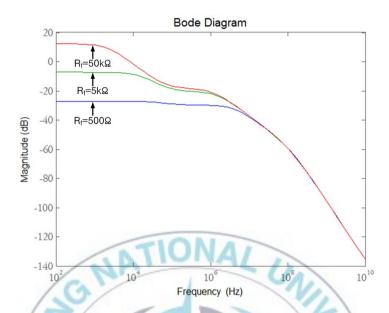

제안된 위상고정루프 구조의 잡음 특성을 알아보기 위해 폐루프 전달함수를 매트랩으로 시뮬레이션 한 결과가 그림 3.8에 나타나 있다.

그림 3.8에 나와 있는 번호는 다음과 같은 조합을 나타낸다. ①번은 기존 2차 루프필터를 가진 위상고정루프 이다. 대역폭 근처에서 영점에 의한 peak 현상을 보여주고 있다. 영점이 위상고정루프를 안정하게 해주지만 대역폭 근처에서 잡음의 크기를 증가시킨다. ②번은 기존 2차 루프필터를 가진 위상고정루프에 주파수-전압 변환기를 사용해서 부궤환 루프를 추가한 구조의 위상고정 루프이다. 이 구조는 대역폭 근처에서 영점에 의한 peak 현상을 억제하고 잡음 특성을 획기적으로 개선하였다. ③번은 기존 2차 루프필터를 가진 위상고정루프에 부궤환 역할을 하는 커패시터를 포함한 위상고정루프이다. ④번은 기존 2차 루프필터를 가진 위상고정루프에 주파수 -전압 변환기를 통한 부궤환 루프를 추가하고, 부궤환 역할을 하는 커패시

터를 포함한 위상고정 루프의 결과를 나타낸다. 모든 조합들이 기존 2차루프필터를 가진 위상고정루프보다 우수한 잡음 감쇠 특성을 가지고 있음을 보여주고 있다.

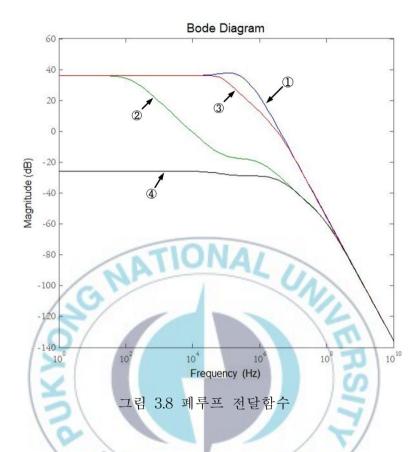

그림 3.9 ②번 조합의 위상고정루프에서 K/Cy 변화에 따른 폐루프 전달함수의 매트랩 시뮬레이션 결과

그림 3.9는 ②번 조합의 위상고정루프에서  $K/C_y$ 의 변화에 따른 잡음감쇄특성을 나타낸다.  $K/C_y$ 의 값이 커질수록 잡음 감쇠 특성이 좋아 지는 것을확인 할 수 있다. 하지만  $K/C_y$ 의 값의 크기는 주파수-전압 변환기의 설계상의 문제로 인해 한계를 가진다.

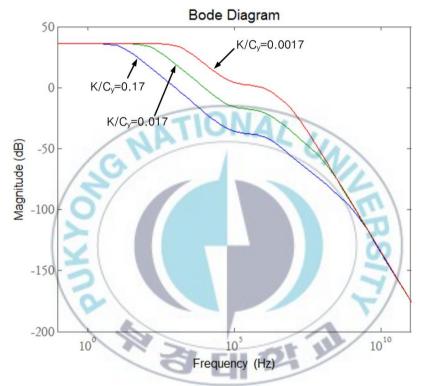

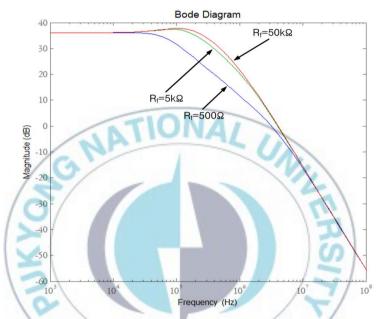

그림10, 그림11는 각각 ③,④조합에서  $R_f$ 크기에 따른 잡음감쇄 특성을 보여주고 있다.  $R_f$ 의 크기가 작을수록, 즉  $C_f$ 가 클수록 잡음감쇄 특성이 향상됨을 알 수 있다.

그림 3.10 ③번 조합의 위상고정루프에서  $R_{\rm f}$  변화에 따른 폐루프 전달함수의 매트랩 시뮬레이션 결과

그림 3.11 ④번 조합의 위상고정루프에서  $R_f$  변화에 따른 폐루프 전달함수의 매트랩 시뮬레이션 결과

#### 3.4 회로 설계

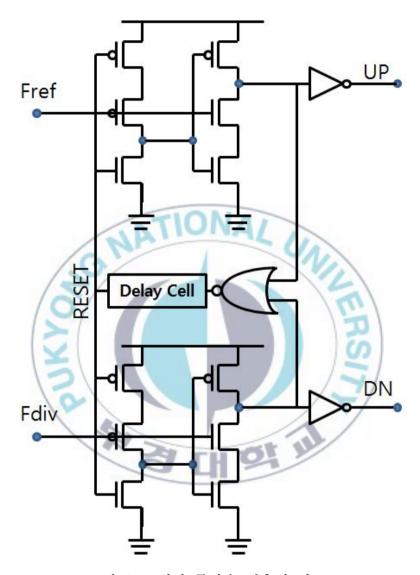

#### 3.4.1 위상 주파수 검출기 (Phase Frequency Detector)

시스템이 고속화, 집적화됨에 따라 위상 주파수 검출기의 속도 향상을 위해서 본 논문에서는 간략화 된 TSPC(True Single Pluse Clock) CMOS 로직회로를 이용한 위상 주파수 검출기를 사용한다. 간략화 된 TSPC CMOS 로직회로를 이용하면 위상주파수 검출기에서 사용되는 전체 MOSFET의 개수를 감소시킬 수 있어서, 전체 칩 면적과 전력 소모를 줄일 수 있다는 장점을 가진다.

제안된 위상 주파수 검출기는 그림 3.12와 같이 TSPC회로로 구성되어있다. TSPC 회로는 간단한 구조, 적은 전력 소비와 빠른 스위칭 동작에 우수한 성능을 나타내기 때문에 널리 사용되어지고 있다. D-F/F은 6개의 MOSFET으로 구성되고, 리셋은 NOR 회로를 사용하였다. 기준신호와 전압 제어 발진기 출력 신호의 위상차가 매우 작은 경우에 위상 차이가 있음에도 불구하고 위상 차이를 검출하지 못하는 데드존(dead zone)문제와 위상 고정 근접 상태에서 위상주파수 검출기의 출력인 UP, DN 신호가 임펄스 형태의 파형을 갖기 때문에, 이 UP, DN 신호에 따른 전하펌프의 충분한 스위칭 시간을 확보하기 위해 NOR 게이트 출력에 인버터 형태의 지연셀을 달아 준다.

그림 3.12 위상 주파수 검출기 회로

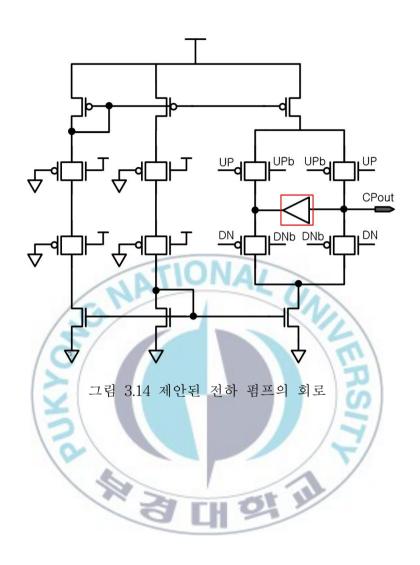

#### 3.4.2 전하펌프(Charge Pump)

전하펌프는 PFD에서 출력된 UP,DN 신호를 입력받아 루프필터에 전류를 흘려줌으로써 전압 제어 발진기를 제어하는데 필요한 전압을 만들어 준다. 전하펌프는 전압제어 발진기를 제어하는 전압에 직접적인 영향을 줌으로 신중히 설계해야 한다.

제안된 구조에서는 위상고정루프가 고정된 이후 UP신호와 DN신호의 타이밍 차이로 인해 발생하는 전류미스매치(current mismatch) 현상을 제거하기 위해 UP/DN신호를 래치버퍼를 통해 전하펌프의 입력으로 연결되도록 하였다. 따라서 공정이 변하더라도 UP/DN신호는 항상 같은 타이밍을 가지게 된다. 이러한 래치버퍼 회로가 그림 3.13에 나타나 있다.

제안된 전하펌프 회로가 그림 3.14에 나타나 있다. 스위치가 동작할 때마다 발생하는 클록피드스루(Clock-feedthrough)현상과 전하공급(charge injection)현상은 출력신호에 불필요한 잡음(spur)들을 생성한다. 전하펌프 출력 노드와 연결 된 단위이득버퍼(Unit Gain Buffer)는 이러한 현상에 의한 구조적 잡음을 억제한다.

그림 3.13 래치버퍼 회로

## 3.4.3 전압 제어 발진기 (Voltage Controlled Oscillator)

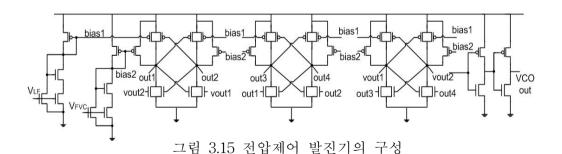

그림 3.15은 전압 제어 저항(Voltage Controlled Resistor)과 3단 ring 구조를 사용한 전압 제어 발진기를 보여주고 있다. 전압 제어 저항을 사용할경우 간단한 구조와 넓은 튜닝범위를 쉽게 변화시킬 수 있다는 것이 장점이다.

전압제어저항(VCR)은 그림 3.15 나타낸 전압 제어 발진기(VCO)의 지연시간을 제어하는데 사용된다. 루프필터와 주파수-전압 변환기의 출력 전압인 VLF과 VFVC는 전압제어저항을 통해 VCO의 지연시간을 제어하는 전류로 변환된다. 전압제어저항은 입력전압의 변화를 큰 전류의 변화로 변환시켜줌으로써 VCO가 넓은 출력주파수 범위를 가지도록 해준다. VCO는 최대출력 전압 진동 폭과 낮은 위상잡음의 출력을 갖는 차동구조 지연 단세개를 이용해 구성하였다. PMOS와 NMOS 한 쌍의 트랜지스터가 CMOS래치구조로 구성되어 지연 단에 추가되었다. 이 래치 구조는 VCO가 낮은 출력위상잡음을 가지도록하기 위해 지연 단이 빠르게 켜지는 시간(on-time)을 갖도록 해준다. VCO는 루프필터와 주파수-전압 변환기로부터입력되는 두 개의 전압제어저항을 가진다.

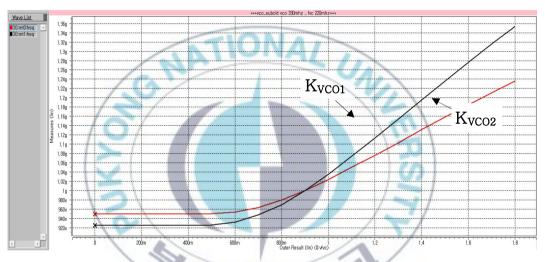

그림 3.16은 VLF(K<sub>VCO1</sub>)의 Gain값과 VFVC(K<sub>VCO2</sub>)의 Gain값을 동시에 나타내는 시뮬레이션 결과이다. 각각의 Gain은 기울기를 통해서 알 수 있고, K<sub>VCO1</sub>은 330Mhz/V, K<sub>VCO2</sub>는 220Mhz/V 의 값을 가진다. 시뮬레이션에서보듯이 두 입력전압이 0.9V 일 때, 두 Gain 그래프가 교차하게 되고, 이때의 출력이 목표한 VCO출력인 1Ghz이다.

그림 3.16 전압 제어 발진기의 전압-주파수 특성

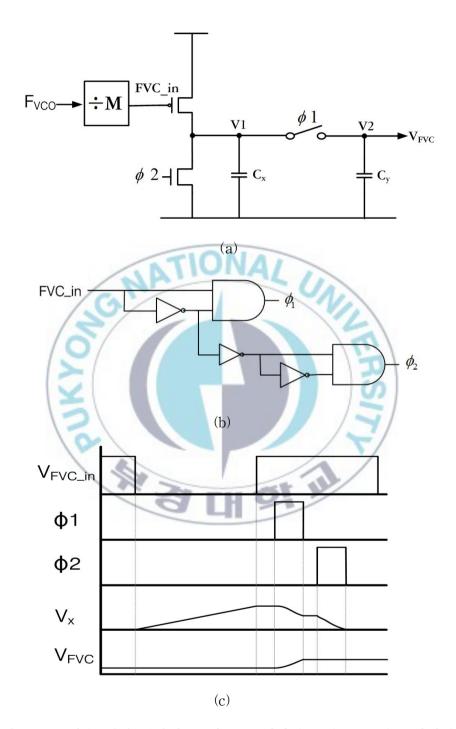

#### 3.4.4 주파수-전압 변환기(Frequency-Voltage Converter)

그림 3.17는 제안한 위상고정루프에 사용된 주파수-전압 변환기의 회로를 나타낸다. 사용된 변수 K는 식(3-7)과 같다.

$$K = I_{FVC} \frac{T_{OUT}}{2} \frac{1}{K' + 1} \tag{3-7}$$

여기서,  $I_{FVC}$ 는  $C_X$ 로 공급되는 전류량,  $T_{OUT}$ 은 PMOS로 입력되는 신호  $(FVC\_in)$ 의 주기, K'는  $C_Y/C_X$ 의 비율이다.

주파수-전압 변환기는 입력신호의 주파수가 낮아지면 출력 DC전압을 상승시키고, 입력신호 주파수가 높아지면 출력 DC전압을 하강시키는 동작을 한다. 따라서 루프필터 전압과 독립적으로 전압제어발진기를 제어 하도록 하여 루프필터 전압변화에 의한 출력 주파수의 변화를 주파수-전압 변환기의 출력전압의 변화로서 보상해 준다.

FVC는 VCO의 출력신호를 입력신호로 받아들인다. 그리고 1/M의 분주기를 통과하게 되는데 이 분주기는 FVC가 정확히 주파수의 변화를 감지하기 위해 duty ratio를 50%로 만들어주는 역할을 한다. Mp는 Vx전압을 상승시키고. Mn은  $\phi_2$ 신호의 제어를 받아 Vx를 0V로 리셋 시킨다.  $\phi_1$ 신호의 제어를 받는 스위치는 Cx에 충전된 전하를 Cy에 충전된 전하와 공유시켜  $V_{LPF}$ 를 변화시키는 역할을 한다.

칩의 크기를 고려한다면 커패시터의 크기는 작을수록 좋다. 하지만 Cy의 크기를 결정함에 있어서 FVC 출력 단에서 바라 본 VCO 입력 커패시턴스보다 10배 이상 크게 설계 하여야 VCO 입력 커패시턴스의 영향을 무시할수 있다. 또한 스위치 MOS소자의 on, off 타이밍 마다 발생하는 Clock

feedthrough, Charge injection의 영향을 고려하여 Cy의 크기를 결정해야 한다.

FVC의 동작이 그림 3.17(c)신호타이밍에 나타나 있다.  $V_{FVC\_IN}$ 신호가 "low" 값을 가질 때 Mp소자가 "on"이 되어 Cx로 전하가 공급되어 Vx가 상승하게 된다. 이 때 Vx의 크기는 입력인  $V_{FVC\_IN}$ 의 주파수와 반비례 관계가 있다. 그 후  $\phi_1$ 신호가 발생하여 Cx와 Cy의 전하를 공유시킴으로 VFVC 전압을 변화 시킨다. 스위치가 off가 되면  $V_{FVC}$ 는 고정되고,  $\phi_2$ 신호가 발생하여 Mn소자가 "on"이 되어  $C_x$ 의 전하를 모두 방전시켜 Vx 전압을 "0V"로 리셋 시키게 된다. 이러한 동작이  $V_{FVC\_IN}$ 의 때 주기마다 발생하게 된다.

결론적으로 위상고정루프의 분주비가 N이고, 주파수 전압 변환기의 입력 단 분주비가 M일 경우, 기준신호 한 주기 동안 루프필터의 전압은 변화 하게 되는데 이 시간동안 주파수 전압 변환기는 N/M번 주파수의 변화를 감지하여 보상해 준다.

그림 3.17 주파수-전압 변환기 (a)회로 (b)제어신호 블록 (c)신호 타이밍

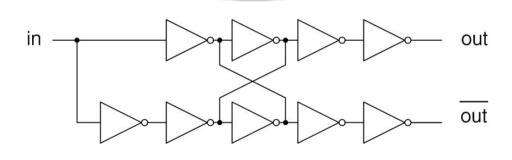

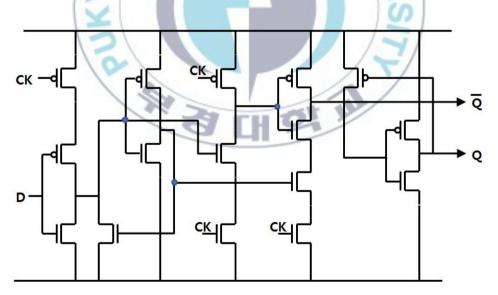

#### 3.4.5 주파수 분주기 (Divider)

본 논문에서 제안된 위상고정루프의 분주기는 그림 3.18에 표현된 다이나믹 E-TSPC (Expanded True Single Phase Clock)을 이용하여 4분주가되는 전치 분주기(Prescaler)를 구성하고 그 뒤에 디지털 P&R을 사용한디지털 제어 입력이 있는 1~16 분주가 가능한 메인 분주기로 구성 되어있다. 4분주의 전치 분주기는 전압 제어 발진기의 고주파수 출력을 저주파수로 떨어뜨리는 역할을 하고, 그 후에 메인 분주기는 낮아진 저주파수를다시 64분주까지 떨어뜨리는 역할을 한다. 이렇게 구성한 이유는 디지털 P&R로 레이아웃 된 블록은 고주파수에서 동작이 원활하지 않기 때문에고주파수에서도 동작이 원활한 전치 분주기를 사용하여 메인 분주기가 칩테스트에서 정상 동작하게 설계하였다.

그림 3.18 다이나믹 E-TSPC (Expanded True Single Phase Clock)

### 3.5 루프필터 스위치 타이밍에 대한 고찰

#### 3.5.1 스위치 타이밍의 영향

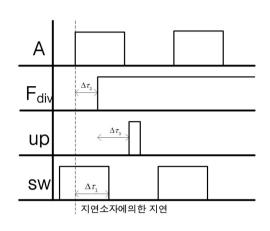

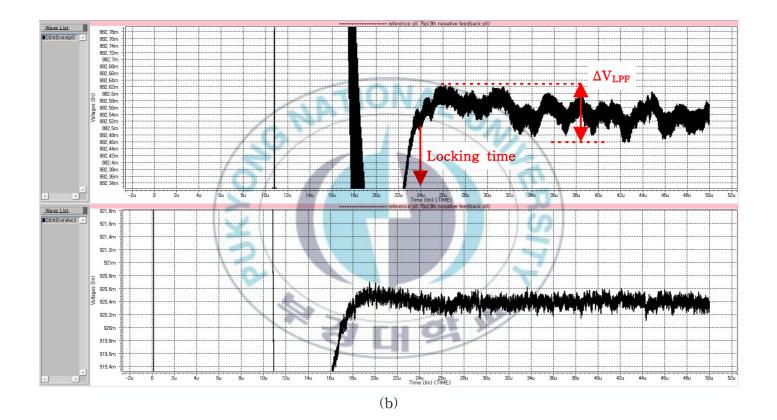

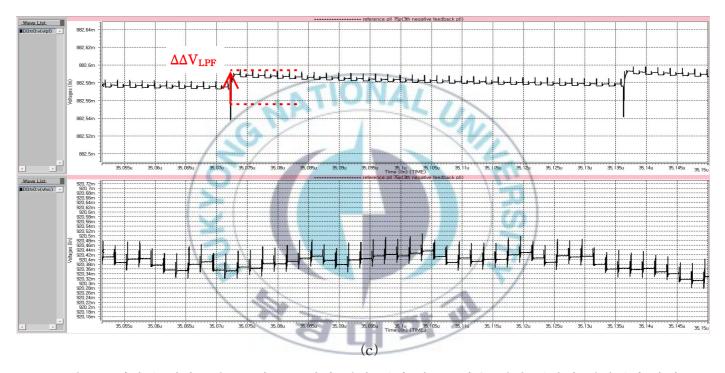

그림 3.19는 제안된 위상고정 루프의 블록다이어그램을 나타낸다. 표 3.1 에 위상고정루프의 위상고정 이후 UP/DN신호와 스위치 신호 타이밍에 대 한  $\Delta V_{LPF}$  값이 나타나 있다. 1번의 경우 UP/DN신호가 인가될 때 스위치 신호는 차단되어 스위치가 동작하지 않도록 스위치신호를 생성하였다. 2번 의 경우 제안된 위상고정루프의 경우로 UP/DN신호가 스위치신호와 겹치 지 않도록 지연소자를 사용하여 지연시간을 조절하여 스위치신호를 인가한 것이다. 3번은 임의로 지연시간을 조절하지 않았을 때 발생할 수 있는 UP/DN신호와 스위치신호가 겹치는 경우를 나타낸다. ΔV<sub>LPF</sub>는 위상고정루 프가 위상고정 이후 루프필터 전압의 peak-to-peak 전압을 나타낸다. 시뮬 레이션은 스위치 타이밍을 제외하고 모두 동일한 조건(Cz= 1.5nF, Rz=1.5k  $\Omega$ , Cp=100pF, Cf=75pF, Ip=200uA, N=64,  $K_{VCO1}$ =330MHz/V, K<sub>VCO2</sub>=220MHz/V)에서 진행하였다. 결과적으로 제안한 구조에서 사용한 2 번이 가장 작은 값을 갖는 것을 알 수 있다.

그림 3.19 제안된 위상고정루프 블록다이어그램

표 3.1 위상고정루프의 위상고정 이후 UP/DN신호와 스위치 신호 타이밍에 대한  $\Delta V_{LPF}$

|   | UP&DN 신호와 스위치 신호 타이밍 | $\Delta V_{LPF}$ |         |

|---|----------------------|------------------|---------|

|   |                      | FVC on           | FVC off |

| 1 | UP & DN SW           | 864µV            | 338µV   |

| 2 | UP & DN SW           | 367µV            | 205μV   |

| 3 | UP & DN SW           | 464µV            | 520µV   |

#### 3.5.2 공정변화에 대한 스위치 타이밍

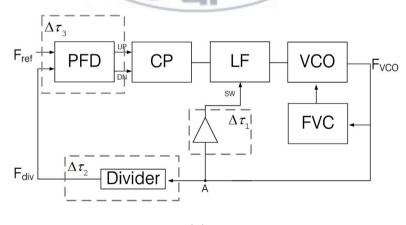

3.5.1에서 보인 것처럼 스위치 타이밍은 제안된 위상고정루프의 성능에 영향을 미치기 때문에 공정이 변하더라도 UP/DN신호와 스위치 신호는 겹치지 않아야 한다. SS/FF/TT 모든 공정에 대해 전체 회로를 시뮬레이션 하여 확인하는 방법이 가장 확실 하지만 시간이 오래 걸린다. 따라서 UP/DN신호와 스위치 신호와 관련된 블록만을 시뮬레이션 하여 확인 하는 방법을 선택했다.

그림 3.20은 제안된 구조의 전체 회로도와 각 노드 신호별 위상이 나타나 있다.  $\Delta \tau_1$ 은 스위치 지연소자의 지연시간,  $\Delta \tau_2$ 는 디바이더의 지연시간,  $\Delta \tau_3$ 은 위상-주파수 검출기의 지연시간을 나타낸다. 따라서 위상고정루프가위상이 고정 된 이후, UP/DN신호가 스위치 신호의 사이에 위치하기 위해서는 다음과 같은 식을 만족해야 한다.

$$\Delta \tau_1 < \Delta \tau_2 + \Delta \tau_3 < \Delta \tau_1 + \frac{T_{SW}}{2} \tag{3-8}$$

(a)

(b) 그림 3.20 (a)제안된 구조의 전체 회로도, (b)신호별 위상

표 3.2에 스위치 신호의 주파수별 각 공정상황에서의 지연 값의 시뮬레이션 결과가 나타나 있다. 이 결과들은 TT 상황에서 설계한 후 공정변화를 주어 지연 값을 계산 한 것이다. 표 3.2(a)는 스위치 신호의 주파수가 1GHz일 때의 결과 이다. 위상고정루프의 출력신호가 지연소자를 통해 스위치를 제어하게 된다. 위상고정루프의 출력신호는 Duty ratio가 50%가 아니라 약 30% 가량 되기 때문에 T<sub>SW</sub>에는 700ps를 대입한다. 그 결과 SS/FF상황에서는 위 식을 만족하지 않는 것을 알 수 있다. 즉, UP/DN신호와 스위치신호가 겹치게 된다. 표 3.2(b)는 스위치 신호로 위상고정루프의 출력신호에 2분주를 한 신호가 사용된다. 그 결과 TT/SS/FF에서 모두 만족하는 것을 알 수 있다. 따라서 스위치 신호를 위상고정루프의 출력신호에 2분주하여 사용하면 UP/DN신호와 스위치신호의 관계를 공정변화와 무관하게 할 수 있다.

표 3.2 스위치신호의 주파수별 각 공정 상황에서의 지연 값. 스위치신호의 주파수가(a)1GHz, (b)500MHz

| 스위치 신호의 주파수 Fsw = 1GHz |                |                  |                |  |

|------------------------|----------------|------------------|----------------|--|

|                        | $arDelta	au_1$ | $\varDelta	au_2$ | $arDelta	au_3$ |  |

| TT                     | 486ps          | 903ps            | 221ps          |  |

| SS                     | 619ps          | 1260ps           | 277ps          |  |

| FF                     | 362ps          | 727ps            | 170ps          |  |

| SS / FF 상황에서 만족하지 않는다. |                |                  |                |  |

(a)

| 스위치 신호의 주파수 Fsw = 500MHz |               |               |                |

|--------------------------|---------------|---------------|----------------|

| 3                        | $\Delta	au_1$ | $\Delta	au_2$ | $arDelta	au_3$ |

| TT                       | 580ps         | 834ps         | 221ps          |

| SS                       | 738ps         | 1070ps        | 277ps          |

| FF                       | 433ps         | 614ps         | 170ps          |

| TT/SS/FF 모두 위의 식을 만족한다.  |               |               |                |

# Ⅳ. 시뮬레이션 결과

### 4.1 시뮬레이션 결과

본 논문에서 제안하는 위상 고정 루프는 공급 전압 1.8V, 0.18μm CMOS 공정 변수를 이용하여 HSPICE로 시뮬레이션으로 회로의 동작을 검증하였다. 입력 주파수는 15.625MHz이고 출력 주파수는 1GHz이다. 다른 파라미터 들은 Cz= 1.5nF, Rz=1.5kΩ, Cp=100pF, Cf=75pF, Ip=200uA, N=64, K<sub>VCO1</sub>=330MHz/V, K<sub>VCO2</sub>=220MHz/V 이다.

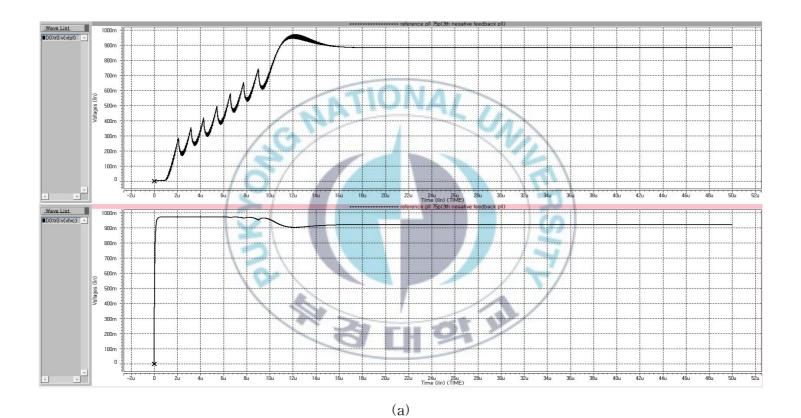

그림 3.1은 제안된 위상고정루프의 루프필터 전압 변화(위)와 주파수-전압 변환기 전압변화(아래)의 시뮬레이션 결과이다. 그림 3.1 (a), (b), (c)는 각각 확대한 그림이다.

표 4.1은 제안된 시뮬레이션 결과와 기본 위상고정루프 구조의 시뮬레이션 결과를 정리한 표이다. 부궤환 역할을 하는 커패시터를 포함한 제안된 구조에서는 고정시간이 24μs로 기본 구조의 위상고정루프보다 약 4μs가량길어 졌지만, ΔV<sub>LPF</sub>와 ΔΔV<sub>LPF</sub>가 크게 줄어 든 것을 확인 할 수 있다. 부궤환 역할을 하는 커패시터의 효과는 주파수-전압 변환기가 동작하지 않았을 경우 (FVC-off) 크게 나타남을 알 수 있다. 이는 위상고정루프 출력 주파수의 정확도 향상과 함께 기준 주파수 의사 잡음(reference spur)이 줄었다는 것을 의미한다.

그림 3.1 제안된 위상고정루프의 루프필터 전압 변화(위), 주파수-전압 변환기 전압변화(아래) (a)전체 파형, (b)고정시간 및  $\Delta V_{LPF}$ , (c) $\Delta \Delta V_{LPF}$

표 4.1 시뮬레이션 결과 (a)제안된 구조, (b)기본 위상고정루프 구조

|          | $t_{lock}$ | $arDeltaV_{LPF}$ | $\Delta\DeltaV_{LPF}$ |

|----------|------------|------------------|-----------------------|

| FVC(on)  | 24us       | 164uV            | 17uV                  |

| FVC(off) | 24us       | 172uV            | 19uV                  |

(a)

|     |          | $t_{lock}$ | $\Delta V_{LPF}$ | $\Delta\DeltaV_{LPF}$ |   |

|-----|----------|------------|------------------|-----------------------|---|

| /   | FVC(on)  | 20us       | 234uV            | 38uV                  | 1 |

| 3   | FVC(off) | 20us       | 1.2mV            | 188uV                 | 0 |

| Mil | nd M     |            | H 25             | III                   |   |

## V. 결론

제안된 위상 고정 루프는 Magna/Hynix 0.18um CMOS 공정을 사용하여 설계하였으며 Svnopsvs의 HSpice 시뮬레이션을 통해 동작을 검증하였다.

그 결과 제안된 위상 고정 루프는 15.625MHz의 입력 신호를 공급 받아 0.9V에서 고정이 되고, 전압 제어 발진기의 출력 신호는 1GHz가 나타나는 것을 확인하였다. 제안한 구조는 기본 위상고정루프 구조의 고정시간보다 4μs길어 졌지만 ΔV<sub>LPF</sub>,와 ΔΔV<sub>LPF</sub> 가 획기적으로 감소하는 것을 확인 할수 있었다. 이 부궤환 역할을 하는 커패시터가 포함된 루프필터의 효과는 주파수-전압 변환기가 없을 경우 더욱 두드러지게 나타났다. 이를 통해 부궤환 역할을 하는 커패시터를 사용한 위상고정루프는 기본 위상고정루프 구조 보다 출력 주파수의 정확도가 향상되었으며, 기준 주파수 의사 잡음 (reference spur)이 억제되었음을 확인 했다. 선형 모델을 통한 매트랩 시뮬레이션으로 잡음 특성 또한 향상 되는 것을 확인 했다. 하지만 스위치신호 타이밍에 대한 정확성 문제가 여전히 남아 있다. Pre-layout 시뮬레이션을 통해 공정변수에 대해 문제가 없다는 것을 확인 했지만, Post-layout 시뮬레이션 할 경우 기생 RC에 의한 지연까지 생각하여 스위치신호 타이밍을 맞춰야 함으로 정교한 layout 기술이 요구된다.

## 참 고 문 헌

- [1] Z. Yang, Z. Tang, and H. Min, "A fully differential charge pump with accurate current matching and rail-to-rail common-mode feedback circuit," in Proc. ISCAS, 2008, pp. 448.451.

- [2] M. S. Hwang, J. Kim, and D. K. Jeong, "Reduction of pump current mismatch in charge-pump PLL," Electron. Lett., vol. 45, no. 3, pp. 135.136, 2009.

- [3] S. Cheng et al., "Design and analysis of an ultrahigh-speed glitch-free fully differential charge pump with minimum output current variation and accurate matching," IEEE Trans Circuits Syst. II, Exp. Briefs, vol. 53, no. 9, pp. 843.847, Sep. 2006.

- [4] T.-C. Lee and W.-L. Lee, "A Spur Suppression Technique for Phase-Locked Frequency Synthesizers," in ISSCC Dig. Tech. Papers, Feb. 2006, pp. 2432.2441.

- [5] C. F. Liang, H. H. Chen and S. I. Liu, "Spur-Suppression Techniques for Frequency Synthesizers," IEEE Trans. on Circuits and Systems-II, vol. 54, pp. 653.657, Aug. 2007.

- [6] J. Choi, W. Kim, and K. Lim, "A Spur SuppressionTechnique Using an Edge-Interpolator for a Charge-Pump PLL," IEEE Trans. on VLSI Systems, pp. 1 5, 2011.

- [7] Floyd M.Gardner, "Charge-Pump Phase-Lock Loop", IEEE J. Tran, on Communications, vol. COM-28, nO,11, pp.1849-1858, Nov. 1980.

- [8] Jaeha Kim, Jeong-Kyoum Kim, Bong-Joon Lee, Namhoon Kim, Deog-Kyoon Jeong and Wonchan Kim, "A20-GHz Phase-Locked Loop for 40-Gb/s Serializing Transmitter in 0.13-µm CMOS", IEEE Journal of Solid-State Circuits, vol.41, no.4, April 2006.

[9] 최영식, 오정대, 최혁환, "자기잡음제거 전압제어발진기를 이용한 위상고정루프", 대한전자공학회 논문지-TC 제 47권, 제 8호, 47쪽-52쪽, 2010. 8.