#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

## Dissertation for the Degree of Doctor of Philosophy

## Development of High-Linearity CMOS

RF Front-End Technology for

Automotive Collision Avoidance Radar

Murod Kurbanov

Department of Information and Communications Engineering,

The Graduate School

Pukyong National University

February 2021

## Development of High-Linearity CMOS

RF Front-End Technology for

Automotive Collision Avoidance Radar

높은 선형성을 가진 차량충돌 방지

레이더용 CMOS 고주파 전단부 개발

Advisor: Prof. Jee-Youl Ryu

by

Murod Kurbanov

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in Department of Information and Communications Engineering,

The Graduate School

Pukyong National University

February 2021

# Development of High-Linearity CMOS RF Front-End for Automotive Collision Avoidance Radar

A dissertation

by

Murod Kurbanov

Approved by:

Professor Seok-Ho Noh,

(Chairman)

Professor Kyu-Chil Park, (Member)

Professor Sang-Hong Park,

(Member)

Dr. Sung-Woo Kim, (Member)

Professor Jee-Youl Ryu, (Member)

## **Table of Contents**

| List of Figures                               | V   |

|-----------------------------------------------|-----|

| List of Tables                                | IX  |

| Acknowledgements                              | X   |

| Abstract                                      | XII |

| CHAPTER 1                                     |     |

| INTRODUCTION                                  | 1   |

| 1.1 Motivation                                | 1   |

| 1.2 Short-Range Radar and Long-Range Radar    |     |

| 1.3 Proposed Front-End Receiver Architecture  |     |

| 1.4 Objective                                 | 5   |

| 1.5 Overview                                  |     |

| CHAPTER 2                                     | 9   |

| 2. Overview and Design of Low Noise Amplifier | 9   |

| 2.1 Background                                | 9   |

| 2.2 S-parameters.                             | 11  |

| 2.3 Gain                                      | 15  |

| 2.4 Stability Factor                          | 16  |

| 2.5 Noise                                     | 18  |

| 2.5.1 Noise Sources                           | 19  |

| 2.5.2 Noise Figure                                          | 21 |

|-------------------------------------------------------------|----|

| 2.5.3 First Stage output noise                              | 24 |

| 2.5.4 Sensitivity                                           | 27 |

| 2.6 Linearity                                               | 28 |

| 2.6.1. Compression Point 1-dB                               | 29 |

| 2.6.2 Third-order Input Intercept Point (IIP3)              | 30 |

| 2.6.3 Consideratrion of System Level Linearity              | 33 |

| 2.7 Input Impedance Matching Network                        | 34 |

| 2.8 Circuit Design and Analysis                             | 35 |

| 2.8.1 Overview of 24GHz Radar                               | 37 |

| 2.8.2 Design of the Proposed 24GHz CMOS LNA                 | 38 |

| 2.8.3 Small Signal Analaysis                                | 42 |

| 2.8.4 Implementation                                        | 51 |

| 2.9 Measurement Results and Discussions                     | 53 |

| 2.9.1 Measurement of S-Parameter and Noise Figure           | 53 |

| 2.9.2 IIP3 and Stability Factor                             | 57 |

| 2.10 Summary                                                | 62 |

| CHAPTER 3                                                   | 63 |

| 3. The Design of Low-Power Down-Conversion Mixer for 24 GHz |    |

| Automotive Radar                                            | 63 |

| 3.1  | Background                              | 63  |

|------|-----------------------------------------|-----|

| 3.2  | Linearity Methods                       | 67  |

| 3.3  | Important features of Mixers            | 73  |

|      | 3.3.1 Level in dBm                      | 73  |

|      | 3.3.2 Conversion Gain (CG)              | 74  |

|      | 3.3.3 Noise Figure (NF)                 | 74  |

|      | 3.3.4 Isolation                         | 79  |

| 3.4  | Topology of Active Transistor Mixers    | 80  |

|      | 3.4.1 Unbalanced Mixer                  | 81  |

|      | 3.4.2 Single Balanced Mixer             | 83  |

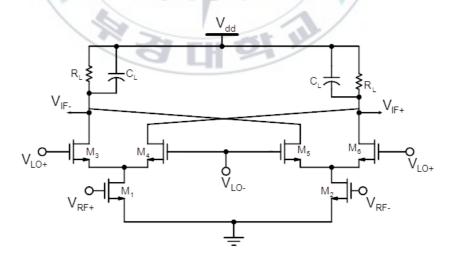

|      | 3.4.3 Double- Balanced Mixer            |     |

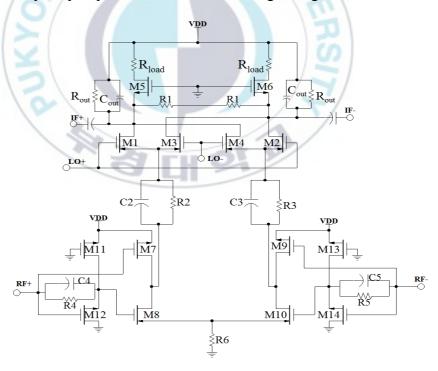

| 3.5  | Circuit Design and Analysis             | 88  |

|      | 3.5.1 Structure of 24GHz Radar          | 89  |

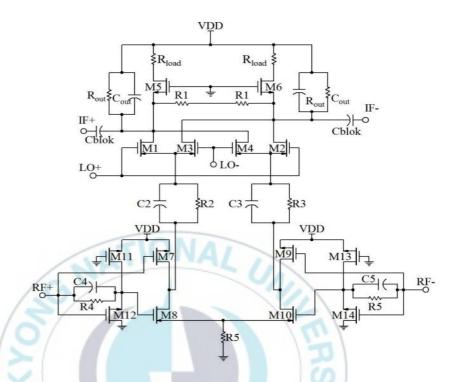

|      | 3.5.2 Design of 24GHz CMOS Mixer        | 89  |

| 3.6  | 6 Results and Discussions               | 97  |

|      | 3.6.1 Transient and Harmonics responses | 97  |

|      | 3.6.2 Noise Figure                      | 99  |

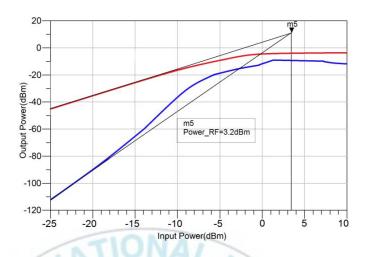

|      | 3.6.3 Order 3 interception point (IIP3) | 100 |

| 3.7  | 7 Summary                               | 104 |

| CHAP | ΓER 4                                   | 105 |

| 4. Design of Low Power and High Linearity CMOS RF Front-End |     |

|-------------------------------------------------------------|-----|

| Receiver in 65nm Technology for 24GHz Application           | 105 |

| 4.1 Background                                              | 105 |

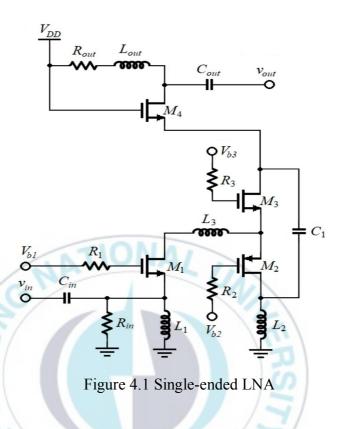

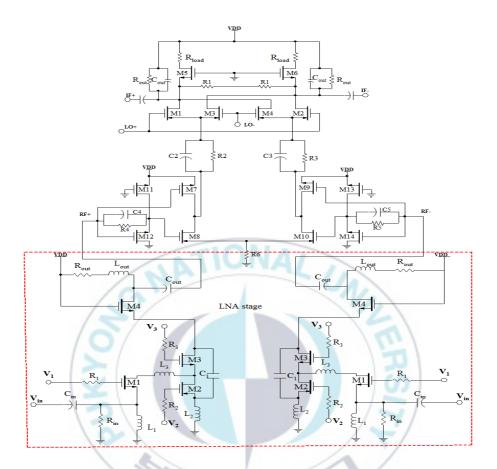

| 4.2 Differential Cascode LNA Design Procedure               | 106 |

| 4.3 Double-balanced down-conversion Mixer                   | 108 |

| 4.4 Analysis of the Proposed Front-End Receiver             | 111 |

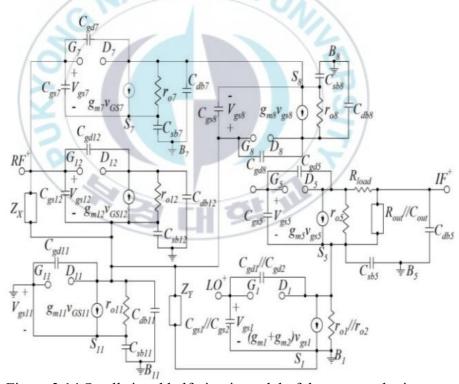

| 4.5 The Proposed Front-End Receiver                         | 112 |

| 4.6 Results and Discussions                                 | 123 |

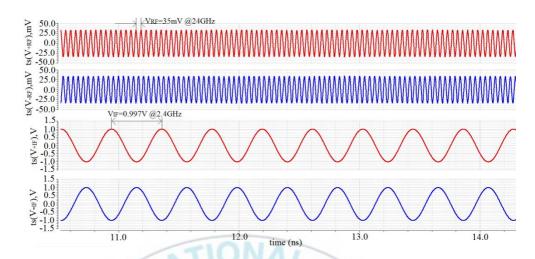

| 4.6.1 Transient signal                                      | 123 |

| 4.6.2 Power consumption                                     | 124 |

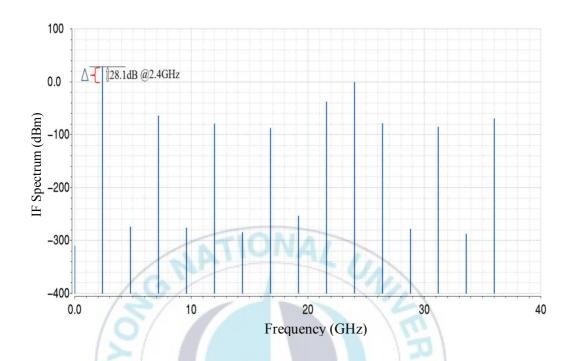

| 4.6.3 Harmonic response                                     |     |

| 4.6.4 S-Parameter response                                  |     |

| 4.6.5 Noise Figure                                          | 126 |

| 4.7 Summary                                                 | 131 |

| CHAPTER 5                                                   | 133 |

| 5. Conclusions and Future work                              | 133 |

| 5.1 Conclusion                                              | 133 |

| 5.2 Future work                                             | 133 |

| REFERENCES                                                  | 137 |

| [Appendix] Publication Paper List                           | 137 |

## **List of Figure**

| Figure 1.1: Combination of SRR and LRR                                                      | 2        |

|---------------------------------------------------------------------------------------------|----------|

| Figure 1.2: Possible application for automotive radar                                       | 3        |

| Figure 1.3: Frontend receiver                                                               | 4        |

| Figure 1.4: Schematic diagram of the frequency conversion                                   | 5        |

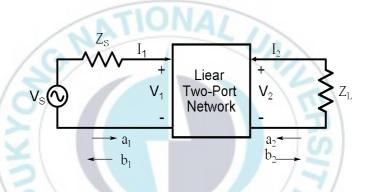

| Figure 2.1: Two-port network with incident waves (a <sub>1</sub> , a <sub>2</sub> ) and re- | eflected |

| waves (b <sub>1</sub> , b <sub>2</sub> )                                                    | 13       |

| Figure 2.2: Two-port MOS network configuration for measuring                                |          |

| the noise                                                                                   | 23       |

| Figure 2.3: Small signal model of a cascode configuration                                   |          |

| including inductively degenerated noise sources                                             | 27       |

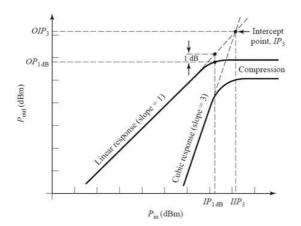

| Figure 2.4: Definition of 1-dB Compression Point                                            | 30       |

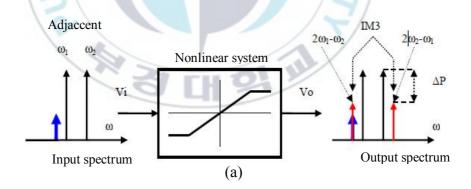

| Figure 2.5: (a) Nonlinear system signal spectrum, and (b) cor                               | nceptual |

| description of IIP3                                                                         | 32       |

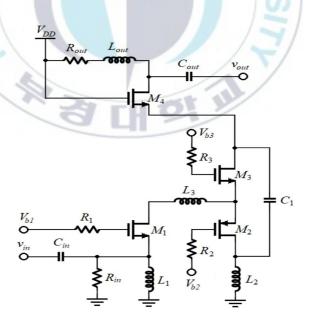

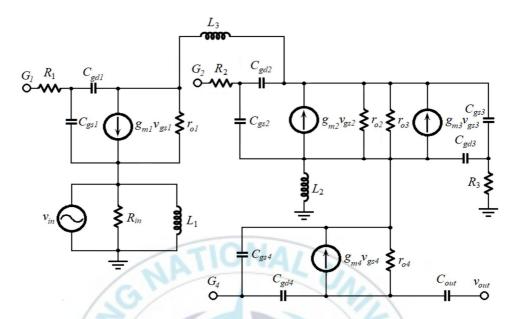

| Figure 2.6: 24GHz CMOS LNA                                                                  | 38       |

| Figure 2.7: Ideal view of the inverter stage                                                | 40       |

| Figure 2.8: High-frequency small signal models for the LNA                                  | 43       |

| Figure 2.9: Layout of the 24 GHz LNA                                                        | 52       |

| Figure 2.10: Die photograph of the proposed LNA                                             | 52       |

| Figure 2.11: (a) Return losses ( $S_{11}$ , $S_{22}$ ) and (b) reverse isolation ( $S_{12}$ )55 | 5 |

|-------------------------------------------------------------------------------------------------|---|

| Figure 2.12: Voltage gain (S <sub>21</sub> )5                                                   | 6 |

| Figure 2.13: Noise Figure                                                                       | 7 |

| Figure 2.14: IIP3 of the LNA                                                                    | 8 |

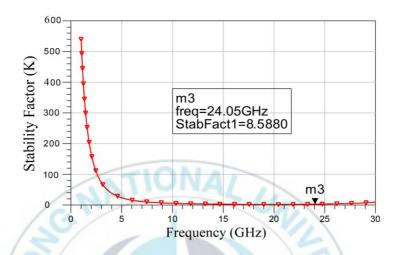

| Figure 2.15: Stability Factor of the LNA                                                        | 9 |

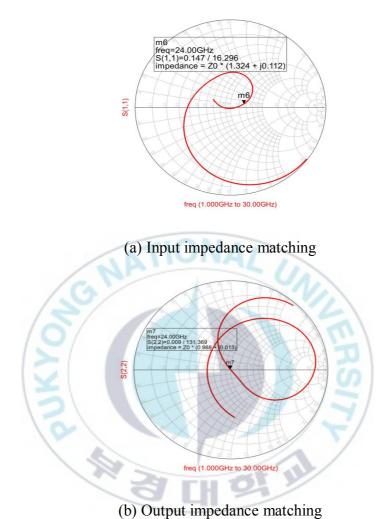

| Figure 2.16: Simulation result of proposed LNA, a) input impedance and                          |   |

| b) output impedance6                                                                            | 0 |

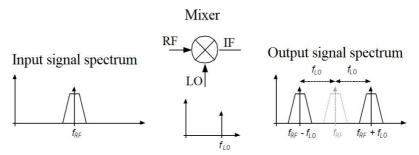

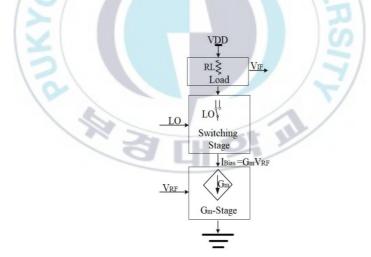

| Figure 3.1: Block diagram of frequency conversion                                               | 3 |

| Figure 3.2: Block diagram of a frequency mixer6                                                 | 4 |

| Figure 3.3: Specific concept of active mixing                                                   |   |

| Figure 3.4: Non-linear system                                                                   | 8 |

| Figure 3.5: Spectrum at the output of nonlinear system                                          | 2 |

| Figure 3.6: Representation of noise in a nonlinear system                                       | 6 |

| Figure 3.7: Cascading non-linear stages                                                         | 7 |

| Figure 3.8: Leakage of LO in RF chain                                                           | 0 |

| Figure 3.9: Specific concept of unbalanced mixing (a) and Unbalanced                            | 1 |

| mixer (b)8                                                                                      | 2 |

| Figure 3.10: Single-Balanced Mixer                                                              | 4 |

| Figure 3.11: Double-Balanced Mixer                                                              | 6 |

| Figure 3.12: Proposed 24GHz CMOS down-conversion mixer                                          | 1 |

| Figure 3.13: High-frequency small-signal model for the mixer          | 93  |

|-----------------------------------------------------------------------|-----|

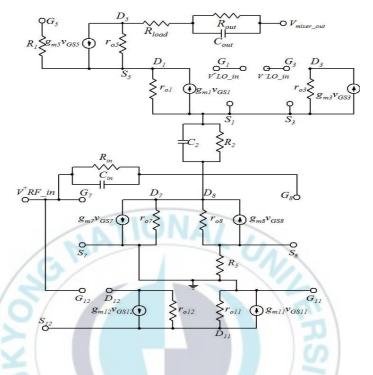

| Figure 3.14: Small signal half-circuit model of the proposed mixer    | 96  |

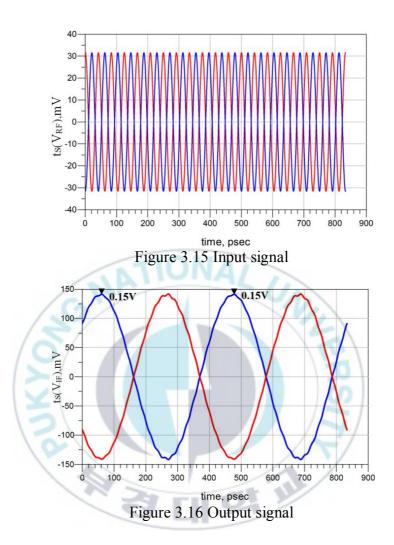

| Figure 3.15: Input signal                                             | 98  |

| Figure 3.16: Output signal                                            | 98  |

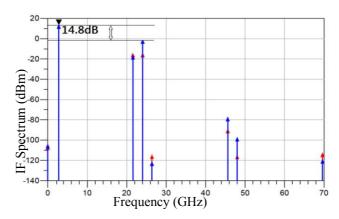

| Figure 3.17: Conversion gain of proposed mixer                        | 99  |

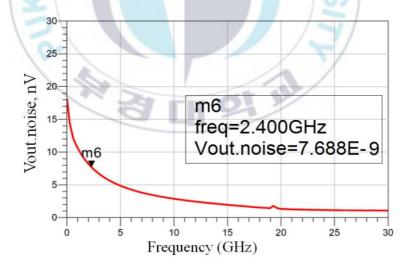

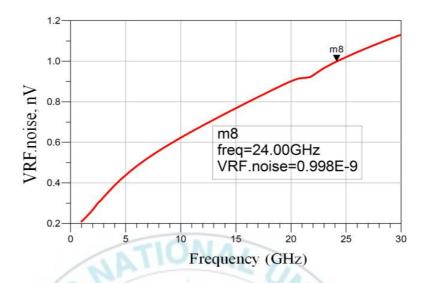

| Figure 3.18: Output noise                                             | 99  |

| Figure 3.19: Input noise                                              | 100 |

| Figure 3.20: Third order interception point (IIP3)                    | 101 |

| Figure 3.21: The proposed mixer layout                                | 102 |

| Figure 4.1: Single-ended LNA                                          |     |

| Figure 4.2: 24 GHz CMOS down-conversion mixer                         | 109 |

| Figure 4.3: Conversion gain versus mixer transistor regions           | 111 |

| Figure 4.4: Possible application for automotive radars                | 112 |

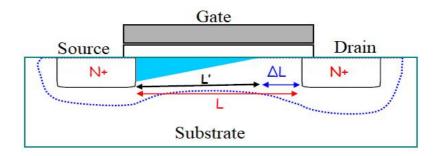

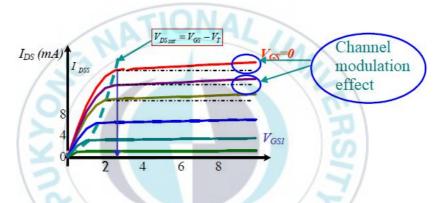

| Figure 4.5: Modulation of $L$ when $V_{ds}$ varies                    | 114 |

| Figure 4.6: Saturation of the MOS as a function of L                  | 114 |

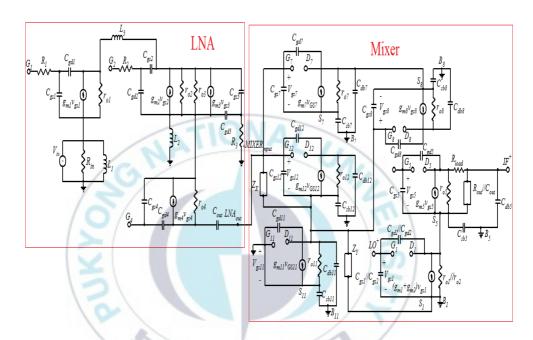

| Figure 4.7: Proposed differential LNA connected to down-conversion    | 117 |

| Figure 4.8: Small signal half-circuit model of the proposed LNA-mixer | 118 |

| Figure 4.9: Input and Output signal                                   | 124 |

| Figure 4.10: Conversion gain of proposed LNA-mixer                    | 125 |

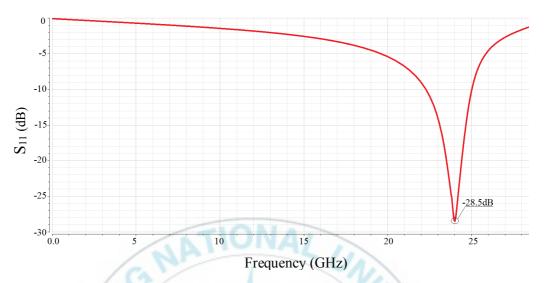

| Figure 4.11: Simulation result of input S <sub>11</sub> loss          | 126 |

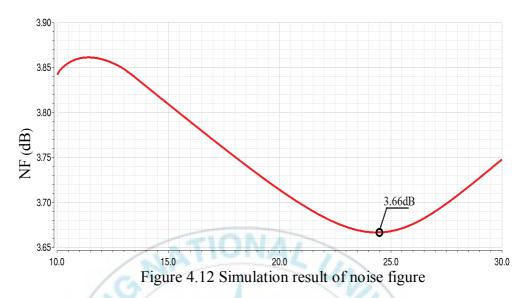

| Figure 4.12: Simulation result of noise figure | . 127 |

|------------------------------------------------|-------|

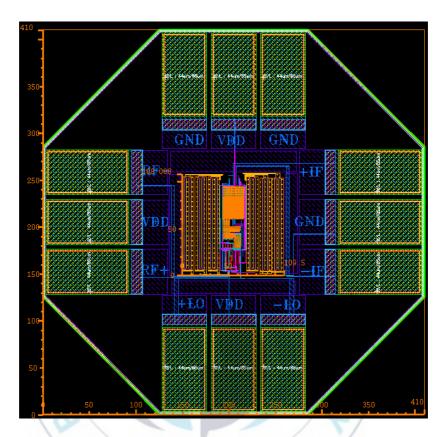

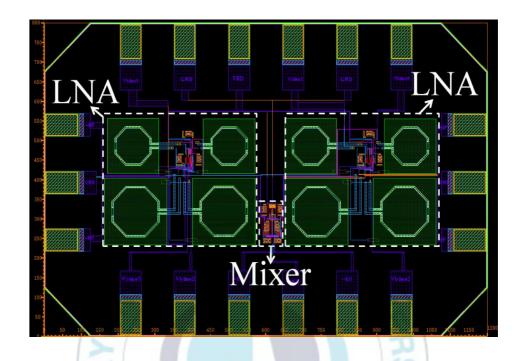

| Figure 4.13: Layout of front-end receiver      | 128   |

## List of Table

| Table 2.1: Comparison summary for recently reported res        | search |

|----------------------------------------------------------------|--------|

| results                                                        | 61     |

| Table 3.1: Shows the comparison of this work and some of the 2 | 24GHz  |

| CMOS mixers, reported in the recent literature                 | 103    |

| Table 4.1: Measured results for the receiver front-end.        | 129    |

| Table 4.2: Shows the comparison of this work and some of the 2 | 24GHz  |

| front-end receiver reported in the recent literature.          | 130    |

## Acknowledgments

First and foremost, I would like to present my utmost gratitude to my supervisor, Professor Jee-Youl Ryu, for providing me with the opportunity to pursue the Ph.D degree in System on Chip Laboratory, Pukyong National University, Busan, South Korea. His thorough supervision and appreciable support have enabled me to materialize my objective of successful completion of Ph.D degree in Korea.

I would like to thank the members of the Office of International Relations and other department offices in Pukyong National University for the facilities and supports given me for the stay in Korea.

I would like to thank and appreciate my colleagues in the SoC laboratory and the other friends I met in Korea for their support given me in one way or another throughout my precious life in Korea.

Last but not least, my sincere love and thanks to my parents who lives in Samarkand Uzbekistan and my wife who motivated me for my study, for their words of encouragement and love which brought me faith and a happy life while staying away from home.

## **Murod Kurbanov**

Department of Information and Communication Engineering

Pukyong National University, Busan

#### **ABSTRACT**

In recent issues, an RFIC is being more popular due to stability, compactness, and small dimension. Especially, an RF circuit in the mm-wave band is convenient to design it from the spectrum regulations and technology availability. Transceiver design in CMOS technologies is always a matter of challenges to get higher performance. The demand of RF frontends increases which should be firmly incorporated with analog, digital, and mixed signal hardware. However, the reliability of the incorporated RF frontend receiver keeps on involving significant concern and impressive research.

In this thesis, we propose a new approach of design and performance analysis of an RF frontend receiver. It consists of a differential low noise amplifier (LNA) and, a down-conversion mixer for automotive collision avoidance radar application. The LNA and mixer is designed and implemented using 65nm RF CMOS technology with the supply voltage of 1.5V at 24GHz. The LNA is designed with cascode inductive source degeneration technique. The bias offset method is adopted in mixer design to boost its conversion gain and to reduce power consumption. This RF frontend receiver is improved by features with a trade-off between linearity and gain. The work is performed on Cadence Virtuoso design and

simulation platform.

The proposed frontend showed very high third-order input intercept point (IIP3) of 4.3dBm to verify excellent linearity. The circuit also showed high conversion gain of 28.1dB, low noise figure of 3.66dB, and a very low power consumption of 6.03mW. This frontend showed a small die area of  $0.80\times1.2$ mm<sup>2</sup> and  $0.32\times0.89$ mm<sup>2</sup> with and without pads, and input and output return losses of -28.5dB and -28dB, respectively.

## Chapter 1

#### 1. Introduction

#### 1.1. Motivation

Road traffic collisions have become a significant global concern over the past few years. To increase road safety and comfort by informing the driver for obstacles or slowdowns on the road, automotive collision avoidance radar applications are being implanted on a lot of transport systems and deluxe passenger cars for many years. During the last decade, so many researches have been conducted in 24GHz and 77GHz band radars [1], [2]. For the sake of detection of other near vehicles in the medium-short range and wide beam, 24GHz is the main stream in the design of an automotive collision avoidance radar. In fact, this choice of frequency involves trade-offs between several factors such as transmitted power and received power [3]. The advanced cruise control (ACC) introduces automotive radar, it consists of two types of radar such as short range radar (SRR) and long range radar (LRR) [4].

### 1.2. Short-Range Radar and Long-Range Radar

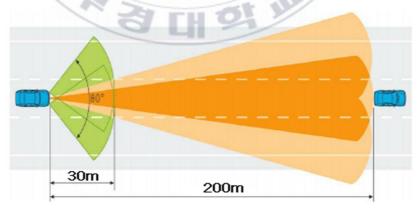

Figure 1.1 shows that the opening angles for each one of the two types of radar are different. It goes from 30° to 180° in the case of the SRR

whereas a value of lower than 10° is generally required for the LRR. The SRR aims to detect objects in the immediate vicinity of the vehicle with a detection distance of up to 30 meters in maximum. This radar is intended to warn the driver for the risk of collisions. It can be coupled to passive safety systems that can be triggered such as pre-crash detection, parking aid side object detection and blind spot detection. It also provides information on obstacles in blind spots detection during lane changes, and it can help with parking. Finally, systems provide recognition of traffic signs and the detection of pedestrians on road. The LRR provides the capability to complement the SRR capability by allowing detection of upstream vehicles to maintain a minimum safe distance on the road. The LRR works in pulse mode with a covered distance of approximately 200 meters.

Figure 1.1. Combination of SRR and LRR

Figure 1.2 shows all applications for automotive collision avoidance

radar, the radar aims to improve the safety of drivers, and to anticipate driving in case of danger. The radar also controls the braking system and steering wheel to save the people's life, and reduce the severity if collisions. Future generations of vehicles should be able to communicate with each other for their relative positions, and to alert each other for traffic status or weather. In near future, all applications should be developed at 24GHz and 77GHz. All of these predictive security applications are part of the Intelligent Transportation System (ITS) at 24GHz [5].

Figure 1.2 Possible application for automotive radar

## 1.3. Proposed Frontend Receiver Architecture

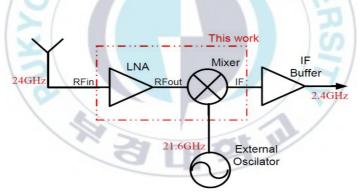

Several silicon technologies are eligible for millimeter-wave

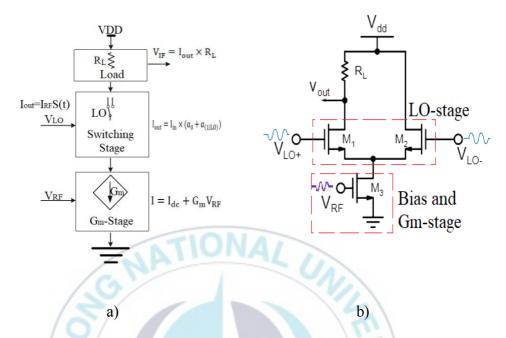

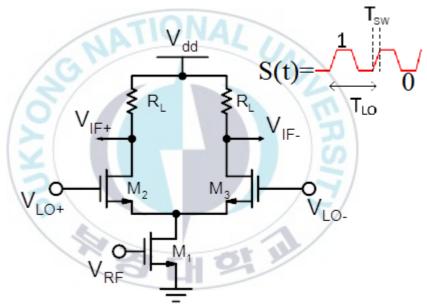

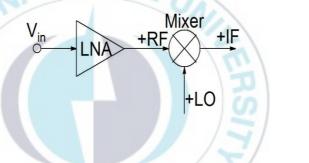

applications. CMOS technology achieves a high level of integration. BiCMOS technology is more complex than CMOS technology. The schematic frontend receiver is shown in Figure 1.3. The transmitted signal from the antenna has a very low power level since the wireless communication provides a lot of losses in long distance. In a receiver, an LNA is used after antenna to amplifier voltage level of the received signal [6]. The mixer is used to convert the amplified signal into the desired lower frequency to enable channel filtering. The mixer also effectively multiplies the signal to another signal provided by a local oscillator (LO).

Figure 1.3 Frontend receiver

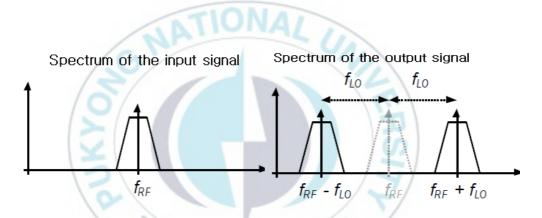

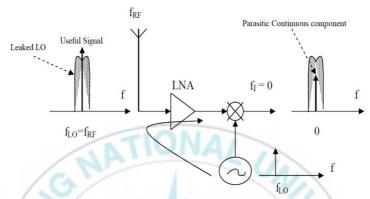

Figure 1.4 shows basic mixing principle for the mixer. In the mixer, a modulated RF signal is inserted, while a second signal from the LO performs the frequency transposition. At the output, an intermediate frequency (IF) signal contains the sum and difference frequencies of  $f_{RF}+f_{LO}$

and f<sub>RF</sub>-f<sub>LO</sub>. The principle of a mixing requires the use of nonlinearities of components to realize the conversion into lower frequency. The nonlinear mixer is able to apply at any frequency where the device presents a known nonlinearity. At low frequencies excellent switches can be realized, so the switching mode mixer is preferred because it generates lesser spurs. These nonlinearities are controlled by the amplitude of the signal.

Figure 1.4 Basic principle of the frequency conversion

#### 1.4. Objective

The main objective of this work is to design RF front-end receiver with a low noise amplifier(LNA) and mixer using 65nm RF CMOS technology for 24 GHz automotive radar [7]. This front-end receiver provides short distances applications. The conventional building style of RF front-end receiver is generally merged and coupled jointly with matching

network, filters, or balun. This study reports low-power and high-linearity fully-differential LNA connected to downconversion mixer. The objectives of this work are as follows:

- To design a new RF front-end receiver architecture to perform the collision avoidance. Due to a low-power and low-cost issue, the RF receiver is the best among the different architectures. The leakage, mismatch, and flicker(1/f) noise from local oscillation(LO) are several issues of the receiver. To solve these issues, the double balanced mixer architecture of single intermediate frequency(IF) is proposed. Initially, the incoming signal is converted into an IF in this type of receiver, and then it is converted into a baseband frequency again. This process softens the receiver back-end requirements and allows low-frequency analog-to-digital conversion.

- > To prove the validity of each block in the receiver frontend, a set of new mathematical formulas is given.

- ➤ New LNA has been designed, implemented, laid out, and finally fabricated. The designed LNA has unique structure and its features have been proved by mathematical equations and the measurement results.

- The second block in front-end receiver is downconversion mixer.

LNA and mixer are combined to reduce the power consumption and to increase the linearity of the overall receiver. The mixer circuit is employed in an IF receiver(*IF downconversion mixer*) to reach the predefined characteristics such as low noise and low power consumption.

#### 1.5. Overview

The study is structured as follows. The first block in the receiver front-end, known as the low noise amplifier(LNA) is introduced in Chapter 2. The background of LNA is presented, and then the fundamental features of LNA are defined. These fundamental characteristics assist the readers to get LNA parameters, and present trade-offs between the output effects of LNA which provide at the end of this chapter. After this, the new concept of LNA is proposed and proved with mathematical equations as well. The measurement outcomes verify the validity of the newly designed circuit for RF applications. The design of layout and die microphotograph of the proposed LNA is additionally presented. The evaluation of the proposed concept as compared with the conventional research results is given as well [8].

The definition and clarification of downconversion mixer is addressed in Chapter 3. Various types of active mixer configurations are

discussed with their advantages and disadvantages. The new mixer structure is established to achieve the predefined parameters such as noise figure(NF), conversion gain, and power consumption at the end of Chapter 3.

The complete front-end receiver is discussed in Chapter 4. The different blocks of the receiver chain on a single chip are assembled together in this chapter. Each block of LNA and mixer is analyzed in detail and clarified. At the end of this chapter, the results of the proposed front-end with a high level of integrity are shown. Additionally, we show the layout and die microphotograph of the receiver front-end [9], [10].

## Chapter 2

#### 2. Overview and Design of Low Noise Amplifier

#### 2.1. Background

The most demanding component is the low noise amplifier(LNA), which is normally the first component in RF receiver. At the same time, it must meet several specifications that make its architecture difficult. The signal from the receiver antenna at the input of the LNA is very low and typically ranges from under -130dBm(for GPS signals) to -70dBm. Therefore, the LNA amplifies these signals without creating any noticeable disruption to the handling of the following stage such as mixer and filter. It sets the LNA's requirement for a certain benefit. The sensitivity of the receiver chain is further determined by the sensitivity to the LNA [11]. This needs that the overall receiver must be integrated with minimal noise from the LNA. Based on IEEE standards, there are specific input/output termination impedances, i.e.  $50\Omega$  or  $75\Omega$  on the LNA. LNA noise is a function of source impedance as well. It's noteworthy that the optimum source impedance for minimum noise figure from the one is required for the input impedance of the preceding stage with  $50\Omega$  [12].

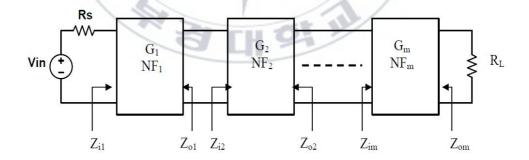

Therefore there are trade-offs between gain, noise figure, and input/output matching impedance. The LNA sets the receiver's minimum noise number based on Friis' equation. The Friis' equation is used to measure a successive system's total noise figure, and each stage with its noise figure and gain. The Equation (2.1) expresses the total noise figure [13].

$$F_{total} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \frac{F_4 - 1}{G_1 G_2} + \dots + \frac{F_n - 1}{G_1 G_2 \dots G_n}$$

(2.1)

where the  $F_i$  and  $G_i$  are a noise figure and gain of the  $i_{th}$  stage, respectively. Because of this equation, a receiver's total noise is mainly dominated by the first stage of the system when the LNA has high voltage gain( $G_1$ ). As expressed in Equation (2.2), the noise of subsequent stages degrades by LNA gain.

$$F_{receiver} = F_{LNA} + \frac{F_{rest} - 1}{G_{LNA}},\tag{2.2}$$

where  $F_{rest}$  is a noise figure of next stage. Therefore, the LNA provides adequate gain to transcend the noise of the next stages, although it can compromise the receiver's sensitivity. The significant problem as well as the noise figure and gain is sufficiently wide bandwidth [14], [15]. To cover the entire reception band with a certain margin of size, but narrow enough to

eliminate unwanted interferers, only a good input impedance matching with source input is needed to fulfill LNA's filtering function. In addition, overall front-end or receiver linearity efficiency usually depends on the linearity of this stage(LNA). Linearity such as bandwidth should be adequate to accommodate broad blockers and not to create undesirable intermodulation tones within the band being considered.

Therefore, there are many conditions to be fulfilled to build a proper LNA. While meeting all specifications together is difficult due to simultaneous parameter optimization, designers need to find solutions according to their own desires. A great number of different topologies of LNA are already presented in open literatures.

#### 2.2. S-Parameter

Scattering parameters usually called by S-parameter are widely used in the design and study of microwave and RF circuits. In S-parameter a set of parameters is used which is connected to the moving vibrations that are scattered or mirrored whenever an n-port network is placed in a transmission line.

To characterize an n-port linear network, S-parameter analysis is basically used as a modelling method. H-parameter, Y-parameter, and Z- parameter are other methods to characterize the n-port network. Since they are behavioral modelling methods, we can put all of them into the same category for a network. The device or n-port network is assumed as a black box, and only the interaction between the ports and outer environment is modelled. For example, H-, Y-, or Z-parameter are commonly used in low frequencies, because voltage and current are the variables for finding the transfer function. However, if we want to use H-, Y-, or Z-parameter, some problems arise for relatively high frequencies.

It is difficult particularly for RF bands to apply short and/or open circuit conditions at each port in H, Y or Z measurement. In stable short or open circuit settings, active devices such as transistors and tunnel diode are not most often connectable.

On the other hand, S-parameters are typically measured with the system embedded between a load and a source of  $50\Omega$ , so oscillations are very unlikely to occur. The main advantage of S-parameter is that the moving waves do not differ in magnitude at every points along a lossless transmission line, unlike terminal voltages and currents. This ensures that S-parameter can be calculated at a distance from measuring transducers on a system.

The behavior of the two-port network in Figure 2.1 can be described by

the linear equations using S-parameter as defined in Equations (2.3) and (2.4).

$$b_1 = S_{11}a_1 + S_{12}a_2 (2.3)$$

$$b_2 = S_{21}a_1 + S_{22}a_2 \tag{2.4}$$

where  $a_1$ ,  $a_2$ ,  $b_1$  and  $b_2$  are traveling waves.

Figure 2.1. Two-port network with incident waves  $(a_1, a_2)$  and reflected waves  $(b_1, b_2)$

The S-parameter is defined as Equations  $(2.5)\sim(2.8)$ .

$$S_{11} = \frac{b_1}{a_1} |_{a_2 = 0} \tag{2.5}$$

$$S_{22} = \frac{b_2}{2} |_{a_1 = 0} \tag{2.6}$$

$$S_{21} = \frac{b_2}{a_1} \big|_{a_2 = 0} \tag{2.7}$$

$$S_{12} = \frac{b_1}{a_2} \big|_{a_1 = 0} \tag{2.8}$$

For simplicity in measurement and calculation, we assume that the input and the output are both real and positive, and have same reference impedance of  $Z_0$ .

The independent variables  $a_1$ ,  $a_2$ ,  $b_1$  and  $b_2$  can be related to port voltages  $(V_1, V_2)$  and currents  $(I_1, I_2)$  as expressed in Equations (2.9)~(2.12).

$$a_1 = \frac{V_1 + I_1 Z_0}{2\sqrt{Z_0}} = \frac{V_{i1}}{\sqrt{Z_0}} \tag{2.9}$$

$$a_2 = \frac{V_2 + I_2 Z_0}{2\sqrt{Z_0}} = \frac{V_{i2}}{\sqrt{Z_0}}$$

(2.10)

$$b_1 = \frac{V_1 - I_1 Z_0}{2\sqrt{Z_0}} = \frac{V_{r1}}{\sqrt{Z_0}} \tag{2.11}$$

$$b_2 = \frac{V_2 - I_2 Z_0}{2\sqrt{Z_0}} = \frac{V_{r2}}{\sqrt{Z_0}}$$

(2.12)

where  $V_{i1} = \frac{V_1 + I_1 Z_0}{2}$  and  $V_{i2} = \frac{V_2 + I_1 Z_0}{2}$  are incident voltage waves on port 1 and port 2, respectively.  $V_{r1} = \frac{V_1 - I_1 Z_0}{2}$  and  $V_{r2} = \frac{V_2 - I_2 Z_0}{2}$  are both mirrored voltage waves from port 1 and port 2.

$|a_I|^2$  is the occurrence power at the input of the system and the available source impedance power  $Z_0$ .  $|b_I|^2$  is the power reflected from the

network port in input port, or the available power from a  $Z_0$  source minus the power supplied to the network.  $|a_2|^2$  is the incident power on the network in output, and also the reflected power from load.  $|b_2|^2$  is the power reflected from the network in output port, or the incident power on the load, which is also the power supplied to the  $Z_0$  load.

The expressed S-parameter related to the mentioned definition of  $a_1$ ,  $a_2$ ,  $b_1$  and  $b_2$  are as follows:

$$|S_{11}|^2 = \frac{Refelected\ power\ from\ input\ network}{Incident\ power\ on\ the\ input\ network}$$

(2.13)

$$|S_{22}|^2 = \frac{Refelected\ power\ from\ output\ network}{Incident\ power\ on\ the\ output\ network}$$

(2.14)

$$|S_{21}|^2 = \frac{Power\ deliverd\ to\ Z_0\ load}{available\ power\ from\ Z_0\ source}$$

(2.15)

= Transducer power gain with  $Z_0load$  and source  $|S_{22}|^2$

(2.16)

= Reverse trabsducer power gain with  $z_0$  load and source

#### 2.3. Gain

The input/output impedance matching network and RF transistor are the parameters that determine and control the gain performance for an RF amplifier such as LNA. The amplifier is modeled by its S-parameter and terminated by arbitrary source and load impedance,  $Z_S$  and  $Z_L$ .  $S_{11}$  and  $S_{22}$

are the input and output reflection coefficients with  $Z_{\theta}$  source and load terminations, respectively.

The voltage gain is defined as Equation (2.17).

$$A_v = \frac{V_{out}}{V_{in}} \tag{2.17}$$

The output voltage of a load impedance is  $V_{out} = I_{out}Z_L$ , and  $I_{out}$  is the output current at input stage, so the voltage gain can be presented as Equation (2.18).

$$A_v = \frac{V_{out}}{V_{in}} = \frac{I_{out}Z_L}{V_{in}} = g_{m,eff}Z_L$$

(2.18)

### 2.4. Stability Factor

Stability is also a very important parameter of RF amplifier. The other parameters such as gain, noise figure are meaningful when the amplifier is stable. By assuming the input impedance at the input port of the amplifier  $Z_i = R_i + jX_i$ , then the  $\Gamma_{in}$  is expressed in Equation (2.19).

$$\Gamma_{in} = \left| \frac{Z_i - Z_0}{Z_i + Z_0} \right| = \sqrt{\frac{(R_i - Z_0)^2 + X_i^2}{(R_i + Z_0)^2 + X_i^2}}$$

(2.19)

If the real part of the input resistance  $R_i$  is negative, i.e.  $R_i < 0$ , then  $|\Gamma_{in}| > 1$ . Oscillation can occur if the loss comes from the input termination

network compensated by negative resistance. The amplifier is potentially unstable. We have same scenario for the stability issue of output port. Therefore, the amplifier is unconditionally stable if for all the passive terminations at the input and output ports, Equations (2.20a) and (2.20b) would be satisfied. Otherwise, it is potentially unstable or conditionally stable.

$$|\Gamma_{in}| < 1 \tag{2.20a}$$

$$|\Gamma_{out}| < 1 \tag{2.20b}$$

In term of S-parameter, it can be expressed that the amplifier are unconditionally stable if it has the following conditions.

$$|S_{11}| < 1 \tag{2.21a}$$

$$|S_{22}| < 1 \tag{2.21b}$$

$$K > 1 \tag{2.22}$$

where K is the stability factor given by Equation (2.23).

$$K = \frac{1 - |S11|^2 + |S22|^2 + |S11 * S22 - S12 * S21|^2}{2|S12 * S21|} > 1$$

(2.23)

Adding a shunt conductance or a series resistance to the unstable port is the simple method to stabilize an active device. Practically, since the input and output ports of the amplifier are coupled to the other, it is usually enough to stabilize one of the ports. One should not add a series resistance or a shunt conductance to the input port of the amplifier, since it will cause additional noise to be amplified. Therefore, the best way is to stabilize the output port.

#### **2.5.** Noise

This is a factor that makes it possible to assess the quality of a device according to the noise. In fact, it allows to quantify the noise level in a signal, and this factor becomes more and more important when dealing with low input powers. There are various noise sources with varying noise generation. Within the integrated circuits shot noise, flicker noise, and thermal noise are the primary sources of noise. The noise from the shot is generated primarily, and it is unique to nonlinear devices such as field - effect transistors through jumping electrical charges over a semiconductor. In MOS systems, the dc gate leakage current is the only source of shot noise, and is therefore not considered a major problem [16]. The shot noise in base and collector is the key sources in the bipolar junction transistor (BJT), and they can dramatically reduce the improved receiver performance.

There is flicker noise known as pink noise, and it comes up because

charges are caught in channel area defects and impurities in MOS devices [17], [18]. As can be seen from the Equation (2.24), flicker noise is directly proportional to the wavelength of operations (f). In the other words, larger MOS devices with large W lead to less flicker noise. Equation (2.24) determines the spectral density of this noise.

$$\overline{\iota_{fn}^2} = \frac{\kappa g_m^2}{fWLC_{ox}^2} \tag{2.24}$$

where K is a device geometric constant, the width and length of the MOS device is W and L, respectively.  $C_{ox}$  is the gate-oxide capacitance per unit area, and  $g_m$  is the trans-conductance of the MOS device [19].

Therefore, at very low frequencies the dominant noise source is flicker noise. Flicker noise plays significant role in LNAs because the frequency range of the received signal is several gigahertzes, and hence it can be ignored [20]. It is noteworthy that in mixers or voltage-controlled oscillators (*VCOs*) flicker should be considered and can be a serious issue.

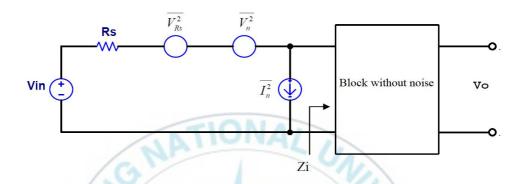

#### 2.5.1. Noise Sources

Figure 2.2 illustrates the standard small signal model of a cascode configuration with noise sources. Four sources of noise have been measured: the thermal source resistance noise  $(i_{n,Rs})$ , thermal channel—current noise  $(i_{n,d})$ , the current noise caused by the gate  $(i_{n,g})$ , and the thermal noise of the

output resistance  $(i_{n,out})$ . The spectral density of power (SDPs) of  $i_{n,Rs}^2$  and  $i_{n,Rout}^2$  are as follows:

$$i_{n,Rs}^{-} = 4KT \frac{1}{R_s} \Delta f$$

(2.25)

$$i_{n,Rout}^{-} = 4KT \frac{1}{R_{out}} \Delta f \tag{2.26}$$

where T is absolute Kelvin temperature, the noise frequency in Hz is  $\Delta f$  and the Boltzmann constant is K.

The SDPs for channel-current thermal and gate-induced noises given by Equations (2.27) and (2.28) [21].

$$i_{n,d}^{-} = 4KT\gamma g_{d0}\Delta f \tag{2.27}$$

$$i_{n,g}^{-} = 4KT\delta g_g \Delta f \tag{2.28}$$

where  $g_g$  is the equivalent conductivity of shunt gate given by [22].

$$g_{g} = \frac{(\omega C_{gs})^{2}}{5g_{d0}}$$

(2.29)

where  $g_{d0}$  is drain conductance of zero drain source voltage, and  $\gamma$  is a parameter y-dependent on technology with a ratio of approximately 2/3 for long-channel devices in the saturation region (in short-channel devices  $\gamma$  is

greater *with* between 2 and 3) [23].  $\delta$  is the noise coefficient of the gate, and is also a parameter depending on technology. The importance is 4/3 for long channel devices, and is decreased in short channel devices by a factor of 2.

#### 2.5.2. Noise Figure

We define the noise figure of a device as being the ratio of the noise power available at the output of the device compared to the part of this power due to the internal impedance of the source placed at the input and assumed to be carried at a temperature of  $290^{\circ}$  K. In other words, the noise figure is the degradation due to the component of the signal-to-noise ratio (SNR) of the source, assumed to be raised to  $290^{\circ}$  K. This is therefore the ratio between the SNR at the input of the device and the SNR at the output of the device.

the device.

$$NF = \frac{\frac{S_{in}}{N_{in}}}{\frac{S_{out}}{N_{out}}} = \frac{SNR_{in}}{SNR_{out}}$$

(2.30)

$= \frac{total \ output \ noise \ power}{output \ noise \ power \ due \ to \ source}$

where  $SNR_{in}$  and  $SNR_{out}$  are respectively the signal-to-noise ratio measured at the input and the output of the device.  $S_{in}$  and  $N_{in}$  are the input noise and signal powers while  $S_{out}$  and  $N_{out}$  represent the output noise and signal

powers, respectively.

The NF can be defined in two ways for each block separately or the entire receiver. LNA noise which is known as  $NF_{LNA}$  determines inherent noise, and it is added to the desired or wanted signal during the process of amplification.

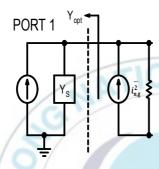

According to the classical two-port network, NF of a noisy two-port network can be written as Equation (2.31).

$$NF = NF_{min} + \frac{R_n}{G_s} [(G_s - G_{opt})^2 + (B_s - b_{opt})^2]$$

(2.31)

where  $NF_{min}$  is the attainable minimum NF,  $B_{opt}$  and  $G_{opt}$  are  $NF_{min}$ 's, ideal source susceptibility and conductance, respectively.  $R_n$  is equal to noise resistance that quantifies NF's ability to deviate from ideal parameters.

The NF is a source admittance function seen from the input terminal of two-port network. An optimum entry, namely  $Y_{opt}$ , should be inserted into the network to attain the NF<sub>min</sub>. The NF<sub>min</sub> and  $Y_{opt}$  expressions for a MOS device can be derived by considering a two-port network configuration for the MOS system. In this model the input port is the gate-source terminal, and the output port is the drain-source terminal.

A small signal model of a MOS device which consists of all noise sources connected to the noise source  $i_s^{-2}$  and the source admittance

$Y_s = G_S + jB_s$  is shown in Figure 2.2.

We assume that in MOS devices  $i_{n,g}^{2}$  and  $i_{n,d}^{2}$  are dominant noise sources and the following expressions for the noise parameters and  $NF_{min}$  can be obtained [24].

Figure 2.2. Two-port MOS network configuration for measuring the

noise.

$$R_n = \frac{\gamma g_{d0}}{g_m^2} \tag{2.32}$$

$$G_{opt} = \alpha \omega C_{gs} \sqrt{\frac{\delta}{5\gamma} (1 - |c|^2)}$$

(2.33)

$$G_{opt} = -\omega C_{gs} (1 - \alpha |c| \sqrt{\frac{\delta}{5\gamma}})$$

(2.34)

$$NF_{min} \approx 1 + \frac{2}{\sqrt{5}} \frac{\omega}{\omega_t} \sqrt{\frac{\delta}{5\gamma} (1 - |c|^2)}$$

(2.35)

where  $\alpha = g_m/g_{d0}$  and for long channel devices it is equal to one, and

decreases as devices shrink to smaller dimensions.

It is obvious from Equation (2.35) that with the increasing transition frequency ( $f_i$ ) the minimum noise figure decreases. It should be noted that as CMOS is scaling down, the transient frequency increases. Therefore, employing CMOS technology will be an advantage to provide low noise figure [25].

# 2.5.3. First-stage Output Noise

Section 2.7 will describe the input impedance of the inductive source degeneration technique in the cascode. Figure 2.3 shows small signal model of a cascade topology with inductively degenerated noise source.

The input impedance should be equal to the impedance of the source, *Rs*, and could be expressed as Equation (2.36).

$$Z_{in} = g_m \frac{L_s}{C_t} = R_s = 50\Omega \tag{2.36}$$

where  $L_s$  is the source inductor, and  $C_t$  is the total capacitance in source.

The quality factor of input circuit is expressed by Equation (2.37).

$$Q = \frac{1}{(R_s + g_m \frac{L_s}{C_t})\omega_0 C_t} = \frac{1}{2R_s \omega_0 C_t}$$

(2.37)

where  $\omega_0$  represents the resonance frequency of input matching network.

From Figure 2.3, output noises of noise sources at  $\omega_0$  are obtained as Equations (2.38)~(2.41).

$$i_{n,out,Rs} = \frac{g_m}{j2\omega_0 C_t} i_{n,Rs} \tag{2.38}$$

$$i_{n,out,Rout} = i_{n,Rout} (2.39)$$

$$i_{n,out,d} = \frac{1}{2}i_{n,d} \tag{2.40}$$

$$i_{n,out,g} = \frac{g_m}{j\omega_0 C_t} \frac{jR_s\omega_0 C_t - 1}{j2R_s\omega_0 C_t} i_{n,g}$$

(2.41)

The correlation Equation (2.42) between  $i_{n,g}$  and  $i_{n,d}$  is suggested by [13]. c=-0.395j and its magnitude decreases for a long channel interface as the channel length falls down [26].

$$c = \frac{\overline{l_{n,g} \cdot l_{n,d}^*}}{\sqrt{\overline{l_{n,g}^2} \cdot \overline{l_{n,d}^2}}}$$

(2.42)

We can measure the PSD of output current due  $toi_{n,g}$  and  $i_{n,d}$  as calculated by Equations (2.43) and (2.44).

$$i_{n,out,g+d}^{-} = \overline{(A\iota_{n,g} + B\iota_{n,d})(A\iota_{n,g} + B\iota_{n,d})^*}$$

(2.43)

$$= \left| A \right|^2 i_{n,g}^{-} + \left| B \right|^2 i_{n,d}^{-} + AB^* \overline{\iota_{n,g} \cdot \iota_{n,d}^*} + A^* B \overline{\iota_{n,g}^* \cdot \iota_{n,d}}$$

$$\vec{i_{n,out,c}^{2}} = (jcAB^* - jcA^*B)\sqrt{\vec{i_{n,g}^{2}} \cdot \vec{i_{n,d}^{2}}} = \frac{g_{m\cdot c}}{2\omega_0 c_t}\sqrt{\vec{i_{n,g}^{2}} \cdot \vec{i_{n,d}^{2}}}$$

(2.44)

where, A and B are transfer functions for Equations (2.40) and (2.41), respectively.

By using Equation (2.37), total noise factor for cascode topology at  $\omega_{\theta}$  is described as Equation (2.45).

$$F_{firs\ tstage} = \frac{i_{n,out,Rs}^{2} + i_{n,out,d}^{2} + i_{n,out,g}^{2} + i_{n,out,Rout}^{2} + i_{n,out,Rout}^{2}}{i_{n,out,Rs}^{2}}$$

(2.45)

It can be also rephrased as Equations (2.46)~(2.48).

$$F_{first\ stage} = 1 + \frac{g_{g1}(Q^2 + \frac{1}{4})P^2 \quad \frac{g_m^2}{g_{dn}} + \gamma_1 \frac{g_{dn}}{4} + \sqrt{\frac{\gamma_1 g_{g1}}{4}} \ cPg_m + \frac{1}{R_{out}}}{R_s Q^2 g_m^2}$$

(2.46)

$$P = \frac{C_{\rm gs}}{C_t} \tag{2.47}$$

$$g_{dn} = \gamma g_{d0} \tag{2.48}$$

The long-channel weights are 8/45 and 1 for  $g_{gl}$  and  $\gamma_l$ , respectively. Parameter P is always less than unity, since due to an extra capacitance  $(C_{ex})$ ,  $C_t$  is always greater than  $C_{gs}$ .

The total noise factor of a LNA is defined as Equation (2.49) according to Friis equation.

$$F_{total} = F_{first-stage} + \frac{F_{subsequent}-1}{G_F}$$

(2.49)

where,  $F_{first-stage}$  is cascode topology noise factor,  $F_{subsequent}$  is the noise factor of LNA, and  $G_F$  is the LNA gain of the first stage [27].

The dominant noise source of the LNA is the first stage noise due to high  $G_F$ . Therefore, the use of source inductive degeneration and the addition of  $L_x$  at the first stage reduce NF.

Figure 2.3. Small signal model of a cascode configuration including inductively degenerated noise sources.

## 2.5.4. Sensitivity

The sensitivity of the overall receiver is determined by the front-end noise figure. This relationship is provided analytically by Equation (2.50).

Sensitivity(dBm) =

$$-174 \frac{\text{dBm}}{H_Z} + 10 \log(\text{BW}) + NF_{tot} + 10 \log(SNR_{out})$$

(2.50)

where -174dBm/Hz characterizes the thermal noise at a temperature of 27°C, NF is the noise figure in dB of the cascaded stages of the whole system, BW is the noise bandwidth of the antenna, and the  $SNR_{out}$  is the minimum signal-to-noise ratio required by the detector to ensure an allowable level of the BER. The receiver noise floor  $N_{out}$  is equal to the sum of the first three terms of the equation below.

$$N_{out} = -174 \, \mathrm{dBm}/_{Hz} + 10 \log(\mathrm{BW}) + NF_{tot}$$

Low *NF* of the LNA as evident from Equation (2.50), greatly decreases the sensitivity of the whole receiver.

### 2.6. Linearity

Dynamic range (DR) is commonly defined as the ratio of the highest possible input voltage without any noticeable distortion that can be tolerated by the circuit to the lowest input voltage that provides sufficient signal quality. Assuming that the LNA input signal is within the range of nanovolt (nV) or microvolt ( $\mu$ V), the LNA will have a large DR to ensure that it remains linear in the presence of large distortions. The amplifiers in the receiver chain must be able to minimize or cancel the adverse effects of large numbers of in-band interferences and inter-modulation/cross-

modulation induced by transmitter leakage or blockers at a high frequency. Nonlinear distortions including intermodulation, cross-modulation and signal distortion can be significant in high frequency amplifiers and restrict the upper DR band. Furthermore, in low frequency, the upper DR limit is usually defined as the input power that the circuit can manage without reaching the saturation region.

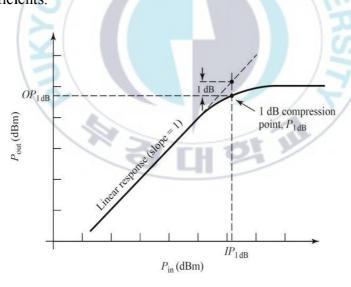

A wide in-band blocker is more likely to desensitize the circuit. It is measured by the 1-dB compression point ( $P_{1dB}$ ). DR measures the efficiency of the signal constrained by the third-order input intercept point (IIP3). There are also plenty of linearity measurement methods for high frequency circuits, but perhaps the most obvious responses are the  $P_{1dB}$  and IIP3.

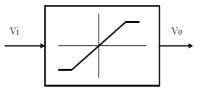

# 2.6.1. Compression Point 1-dB

The  $P_{IdB}$  is commonly defined as the input and output signal amplitude which causes essential gain to reduce by IdB from the ideal or normal small signal gain at the particular frequency as shown in Figure 2.4. Compression point on the LNA dynamic spectrum is known to be an upper limit. Thus input signals at the amplification point of out-of-band are typically compressed or saturated at the output.

It is possible to approximate a nonlinear system by using the Taylor

series defined in Equation (2.51).

$$y(t) = \alpha_1 x(t) + \alpha_2 x^2(t) + \alpha_3 x^3(t) + \cdots$$

(2.51)

The compression point referred to input 1-dB in [28] can be determined as the Equation (2.52).

$$P_{1dB} = \sqrt{0.145 \left| \frac{\alpha_1}{\alpha_3} \right|} \tag{2.52}$$

where  $\alpha_1$  and  $\alpha_3$  are the first and third-order Taylor series expansion coefficients.

Figure 2.4. Definition of 1-dB compression point

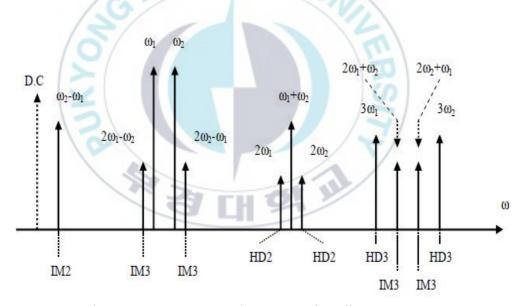

# 2.6.2. Third-order Input Intercept Point (IIP3)

The multiplication of the input signal including its harmonics can cause

distortion with the nonlinear of the reasonable systems. The multiplication leads to the creation of terms of output called by intermodulation products (IMP). For instance, if two adjacent sinusoidal signals (also known as "two-tones") are fed to an LNA's nonlinear system input, due to the nonlinearity of the circuit, the mixing of the harmonics of these signals will produce the intermodulation products of the  $2^{nd}$  and  $3^{rd}$  order at the output but might hide the truth within the frequency response, thus reducing the desired output signal.

Consider a practical system with the input-output relation provided in Equation (2.51) to further investigate the effect of intermodulation. Let's consider that the input signal has almost the same amplitude as Equation (2.53) but has two nearby sinusoidal components.

$$x(t) = A(\cos(\omega_1 t) + \cos(\omega_2 t))$$

(2.53)

Then the following sentence defined in Equation (2.53) should appear at the output of the device. Equations (2.53) and (2.54) are found in the vicinity of both  $\omega_1$  and  $\omega_2$ .

First

- order terms:

$$\begin{cases} at \ \omega_1 : y_{\omega_1} = \left(\alpha_1 A + \frac{9}{4}\alpha_3 A^3\right) \cos(\omega_1 t) \\ at \ \omega_2 : y_{\omega_2} = \left(\alpha_1 A + \frac{9}{4}\alpha_3 A^3\right) \cos(\omega_2 t) \end{cases}$$

(2.54)

Third – order IMP terms:

$$\begin{cases} at \ 2\omega_1 - \omega_2 \colon y_{2\omega_1 - \omega_2} = \left(\frac{3}{4}\alpha_3 A^3\right) \cos(2\omega_1 - \omega_2)t \\ at \ 2\omega_2 - \omega_1 \colon y_{2\omega_2 - \omega_1} = \left(\frac{3}{4}\alpha_3 A^3\right) \cos(2\omega_1 - \omega_2)t \end{cases} \tag{2.55}$$

The input point which has the same output power as the fundamental signal and IMP is labeled in the third-order input intercept point as shown in Figure 2.5. It can be determined experimentally in Equation (2.56).

Figure 2.5. (a) Nonlinear system signal spectrum, and (b) conceptual description of *IIP3*

$$IIP3 = \sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|} \tag{2.56}$$

These equations are valid if we presume that the  $y_{\omega l}$  and  $y_{\omega 2}$  of Equation (2.55) are correct. Expressions  $(\frac{9}{4}\alpha_3A^3)$  are negligible. However, this principle no longer holds where the amplitude of signals is very high at the point of intercept. However, the measured IIP3 value in the Equation (2.56) is essentially an analysis of the weak input signal.

### 2.6.3. Consideration of System Level Linearity

A receiver chain typically consists of several cascaded blocks such as LNA, Mixer, VCO, etc. The overall linearity of a receiver chain therefore depends on the linearity and gain from each point. A receiver chain with different gain and *IIP3* of each individual block is given by the worst-case *IIP3* as the Equation (2.57) [29].

$$\frac{1}{A_{IIP3,tot}^2} = \frac{1}{A_{IIP3,1}^2} + \frac{\alpha_1^2}{A_{IIP3,2}^2} + \frac{\alpha_1^2 \alpha_2^2}{A_{IIP3,3}^2}$$

(2.57)

where  $A_{IIP3,i}$  and  $\alpha_i$  are IIP3 and gain of the *i*-th stage reward, respectively.

A thorough analysis of Equation (2.57) shows that if any stage of a cascade has a gain greater than unity, therefore the nonlinearity of the next stage becomes more critical [30]. This means that the nonlinearity of stages after LNA, e.g. mixer(s), has a major effect on the nonlinearity of LNA rather than the nonlinearity. As we know the LNA production increases, the *NF* decreases. Therefore the trait of linearity is in contrast with the *NF* situation, and there is a trade-off between linearity and *NF*. Usually designers are trying to optimize the LNA gain to obtain the best *NF*.

## 2.7. Input Impedance Matching Network

To transmit the antenna's maximum power to the LNA, the LNA's input port must be calibrated to the antenna's impedance, e.g.,  $50\Omega$ . For narrowband applications, the input impedance of LNA must be matched to antenna impedance in a single frequency with very narrow bandwidth. Even so, for wideband circuits, impedance matching at the LNA input port can be accomplished over a broad range of frequencies and is typically a major challenge given by the requirements for noise and power consumption.

The voltage standing wave ratio (VSWR) specified in Equation (2.58) is usually used to determine the coefficient of impedance matching [31].

$$VSWR = \frac{1+|\Gamma|}{1-|\Gamma|} \tag{2.58}$$

where  $\Gamma$  is the reflection coefficient as explained in Equation (2.59).

$$\Gamma = \left| \frac{Z - Z_0}{Z + Z_0} \right| \tag{2.59}$$

$Z_o$  is the source characteristic impedance for this calculation that becomes usually equal to  $50\Omega$ , and Z is the real impedance of input. Perfect impedance matching with  $Z=Z_o$  results in  $\Gamma=0$  and VSWR=1. However,  $\Gamma$  must be less than -10dB and the matching requirement are normally acceptable.

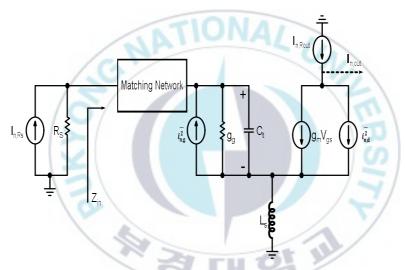

# 2.8. Circuit Design and Analysis

The rapid growth of wireless communications has pursued on low power, low cost, and high performance receivers [32]. In most cases, the millimeter wave circuits were considered by utilizing CMOS technology [33]. The main wireless receiver task is to detect the desired modulated signals [34]. Wireless receivers have to perform several functions such as tuning to the wanted signal carriers, filtering out the undesired signals, and amplifying the desired signal to compensate for power losses occurring during transmission, [35].

Thanks to growing speed of radar-based collision avoidance systems, vehicles can see the other objects including pedestrian and other vehicles, anticipate accidents and collision, control the braking system and steering wheel to save the people life, and reduce the severity of collisions. Radar transceivers are installed on the vehicles which operate in the all types of weather or sometimes both laser and camera are utilized to anticipate the imminent collision on the street or highways [36]. At first, collision avoidance systems search the surrounded area of the vehicles to detect the imminent crash. When the detection process is done, the system warns to the drivers by light, vibration in steering wheel or seat belt, and then the system based on the predefined distance fastens the seat belt and brakes, and finally controls the steering wheel to save the driver. The main frequency bands of radar applications are 24GHz and 77GHz. For the sake of detection of other near vehicles in the medium-short range and wide beam, 24GHz is mainstream [37]. The receiver for the automotive radar system operates in the band of 24 GHz frequency which is composed of LNA (low noise amplifier), down-conversion mixer, and VCO (voltage-controlled oscillator). The LNA is a crucial component for radio receivers [38], and it must meet several requirements such as good input matching, adequate gain and reasonably low noise figure to elevate received signal-to-noise ratio as well

as energy-efficiency for battery-powered portable devices [39].

This part presents low-power low-noise 24-GHz CMOS LNA for automotive collision avoidance radar. The proposed circuit is fabricated using 65nm RF CMOS technology and it is powered by 1.5V supply. To increase voltage gain, this circuit has cascode scheme, and it is optimized to decrease noise figure. Cascode inductive source degeneration technique is also utilized to match the circuit to source impedance.

#### 2.8.1. Overview of 24GHz Radar

The automotive radar is the most promising and robust solution to vehicle sensing requirements in terms of environmental conditions, measurement capabilities, and ease of installation. The best frequency for this radar depends on the targeted application. In fact, this choice of frequency involves trade-off between several factors such as transmitted and received powers. The systems consist of three types such as short range radar (SRR), medium-short range (MRR) and long range radar (LRR). The CMOS-based 24-GHz SRR sensors with distance up to approximately 30 meters are under development for a variety of further applications [40]. The SRR may cover many applications such as parking aid, ACC with stop and go, pre-crash or collision warning, back-up function, etc. Since it has also

better performance in azimuth angle and in range measurements, it is suitable for automotive applications providing parking aid, pre-crash detection, side object detection and blind spot detection [41].

## 2.8.2. Design of the Proposed 24GHz CMOS LNA

Figure. 2.6 shows the proposed low-power low noise-noise 24-GHz CMOS LNA. This LNA is implemented using the 65nm RF CMOS process. This process has been retained because of its good low noise performance, the unity current gain cut-off frequency ( $f_T$ ) of 120GHz and the maximum oscillation frequency ( $f_{max}$ ) of 140GHz.

Figure 2.6. 24GHz CMOS LNA

Successful integration of the LNA at 24GHz depends on minimizing parasitic capacitances and losses to maintain adequate gain, designing with low voltage swing for low breakdown devices, and achieving sufficient linearity required for low spectrally efficient and variable envelope modulation scheme.

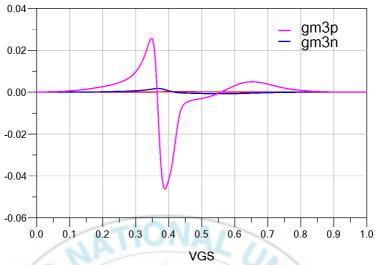

Providing a resistive input impedance of  $50\Omega$  is a critical requirement of an LNA. The  $50\Omega$  termination is required mainly by the previously band select filter  $L_3$  with parasitic capacitance and transistor  $M_1$  is biased by adding parasitic capacitance to the input impedance matching. The third-order non-linear transconductance coefficient  $g_{m3}$  is performed by gate-drain and gate-source capacitances of basic components, and it reduces linearity performance. To improve noise figure and linearity, we propose a CG (common gate) NMOS-PMOS inverter scheme for the cascode LNA as a linearizer. The proposed linearization method accepts NMOS and PMOS transistors into common gate configuration with the second-order and third-order nonlinearity to improve the linearity performance [42], [43].

To reach very low third-order distortion and low power, it is very important to reduce the second-order and third-order nonlinearities. It is very important to minimize or cancel  $g_{m2}$  and  $g_{m3}$  to decrease the third-order intermodulation distortion and to improve *IIP3* (third-order input intercept

point). The inductor  $L_2$ , and the parasitic capacitances at the drain of  $M_2$  and  $M_4$  form provide broadband network.

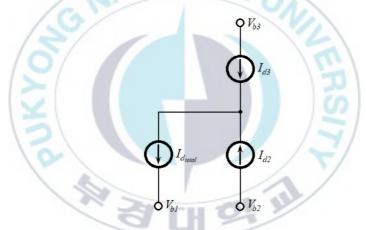

Let's consider drain current  $I_{dtotal}$  of  $M_1$  through the  $M_2$  and  $M_3$  transistors as shown in Fig. 2.7. For  $M_4$ ,  $V_{g4} = V_{dd}$ ,  $V_{s4} = V_{d3}$ ,  $I_{d4} = (V_{dd}-V_{d4})/R_{out}$ ,  $I_{d4} = I_{d3}$  and  $I_{d4} = 0$ , since  $M_1$  is connected to the ground through capacitor  $C_1$  for  $I_{d1} = 0$ . From KCL,  $I_{s3} = I_{d1} + I_{s2}$ ,  $I_{s2} = I_{s3}$ ,  $V_{dd}-I_{d4}R_{out}-V_{ds4}-V_{ds3} = V_{ds2}$ , and  $V_{dd} = I_{d4}R_{out} + V_{d4}$ , and we obtain Equations (2.60)~(2.62).

Figure 2.7. Ideal view of the inverter stage

$$I_{d2} = g_{m1_2} V_{gs_2} + g_{m2_2} V_{gs_2}^2 + g_{m3_2} V_{gs_2}^3$$

(2.60)

$$I_{d3} = g_{m1_3}(-V_{gs_3}) + g_{m2_3}(-V_{gs_3})^2 + g_{m2_3}(-V_{gs_3})^3$$

(2.61)

$$I_{d_{total}}(V_1) = I_{d2} + I_{d3}$$

$$= (g_{m1_2}V_{gs_2} + g_{m2_2}V_{gs_2}^2 + g_{m3_2}V_{gs_2}^3) - (g_{m1_3}(-V_{gs_3}) + g_{m2_3}(-V_{gs_3})^2 + g_{m2_3}(-V_{gs_3})^3$$

(2.62)

Since  $V_{gs_3}$  is a function of  $V_{gs_2}$ , it is expressed to power series of  $V_{gs_2}$  as follows:

$$V_{gs3} = c_1 V_{gs_2} + c_2 V_{gs_2}^2 + c_1 V_{gs_2}^3$$

(2.63)

where  $c_i s$  are in general frequency dependent. In practice, the  $\pi$ -network cancels the effects of  $c_2$  and  $c_3$  at the frequency of interest. To find the coefficient  $c_i s$ , we should solve the equation after expanding  $I_{dtotal}$  as a power series of  $V_{gs2}$  and replacing it with Equation (2.63) we obtain Equation (2.64) [45].

$$= I_{d2} + I_{d3}$$

$$\cong (g_{m1_3} + c_1 g_{m2_2}) V_{b3} + (g_{m2_3} + c_1^2 g_{m2_2}) V_{b3}^2 + (g_{m3_3} + c_1^3 g_{m3_2}) V_{b3}^3 \dots$$

(2.64)

where  $g_{m1}$ ,  $g_{m2}$  and  $g_{m3}$  are the main transconductance, second-order and third-order nonlinearity coefficients respectively [20]. The second order nonlinearity is canceled in output due out off phase signal by NMOS and PMOS. The optimum biasing is used to obtain a high *IIP3* by reducing the total  $g_3$ , the *IIP3* can be calculated as follows: [46].

$$A_{\rm IIP3} = \sqrt{\frac{3}{4} \left| \frac{g_{m1}}{g_{m3}} \right|} \tag{2.65}$$

The  $g_{m3,d3}$  changes from positive to negative when the transistor moves from weak to strong inversion region. In other words, by changing gate bias voltage of PMOS transistor, the parameter  $C_I$  can be varied. It can be deduced from Equation (2.65).

#### 2.8.3. Small Signal Analysis

In LNA solutions it is significant that the input impedance is matched with the antenna impedance to carry out effective power transfer. LNA is proposed like a high frequency application and must be terminated by inherent  $50\Omega$  impedance. If there is any essential turning of load impedance from  $50\Omega$  seen by the filter, then there can be a loss and wave at pass band and stop band characteristics of the filter. Figure 2.8 shows simplified high-frequency small signal model of cascade topology with inductively degenerated for the LNA.  $\mu_p$  and  $\mu_n$  are mobility of charge carriers of PMOS and NMOS transistors respectively. W, L, and  $C_{ox}$  represent the transistor's width, length, and gate capacitance per unit area.

By applying the KCL at source node we get

$$C_{gs} = C_{gd} = \frac{C_{ox}WL}{2} = C_{gc} \ (V_s = V_d).$$

(2.66)

where W and L represent the transistor's width and length, respectively, and  $C_{ox}$  is gate capacitance per unit area.

Figure 2.8 High-frequency small signal models for the LNA.

By applying the KCL at drain node  $d_1$  of  $M_1$ , we get Equations (2.67)~(2.72).

$$(V_{d1} - V_{g1}) \text{jw} C_{gd1} + g_{m1} V_{gs1} + \frac{(V_{d1} - V_{s1})}{r_0} + \frac{(V_{d1} - V_{s2})}{jw L_3} = 0$$

(2.67)

$$(V_{d1} - V_{g1}) jw C_{gd1} + g_{m1} V_{gs1} + \frac{V_{ds1}}{r_0} + \frac{(V_{d1} - V_{s2})}{jw L_3} = 0$$

(2.68)

$$(V_{d1} - V_{g1})(-w^2L_3C_{gd1})r_0 + jwL_3r_0g_{m1}V_{gs1} + jwL_3V_{ds1} + r_0(V_{d1} - V_{s2})$$

$$= 0$$

(2.69)

$$V_{d1}\left[-w^{2}L_{3}r_{0}C_{gd1}+r_{0}\right]+V_{g1}w^{2}L_{3}r_{0}C_{gd1}-r_{0}V_{s2}+jwL_{3}V_{ds1}+jwL_{3}r_{0}g_{m1}V_{gs1}=0$$

(2.70)

$$V_{d1}\left[-w^{2}L_{3}r_{0}C_{gd1} + r_{0}\right] + V_{g1}w^{2}L_{3}r_{0}C_{gd1} - r_{0}V_{s2} + jwL_{3}V_{d1}$$

$$-jwL_{3}V_{s1} + jwL_{3}r_{0}g_{m1}V_{g1} - jwL_{3}r_{0}g_{m1}V_{s1} = 0$$

(2.71)

$$V_{d1}[-w^{2}L_{3}r_{0}C_{gd1} + r_{0} + jwL_{3}] + V_{g1}[w^{2}L_{3}r_{0}C_{gd1} + jwL_{3}r_{0}g_{m1}] +$$

$$V_{s1}[-jwL_{3} - jwL_{3}r_{0}g_{m1}] - r_{0}V_{s2} = 0$$

(2.72)

Now let's analyze the input impedance of the cascade topology using inductive source degeneration technique will explain with the circuit shown in Figure 2.8. The transistor  $M_1$  is replaced with a high-frequency small-signal model consisting of gate-source capacitor  $C_{gs1}$ , gate-drain capacitor  $C_{gd1}$ , transconductance  $g_{m1}$ , and source degeneration inductor  $L_1$ . The input impedance matching is a core technology in RF circuit design. As seen in the Figure 2.6 the input impedance of transistor  $M_1$  is a series an LC circuit given by equation (2.81).

The noise performance of the design sample is good after impedance matching is done.

By applying the KCL at source node  $s_1$  we also obtain Equations (2.73)~(2.75).

$$I_{in} = V_{s1}(\frac{1}{R_{in}} + \frac{1}{jwL_1}) - g_{m1}V_{gs1} - V_{ds1}(\frac{1}{r_0} + jw(\frac{C_{gd1}C_{gs1}}{C_{gd1} + C_{gs1}})$$

(2.73)

$$I_{in} = \frac{V_{s1}}{R_{in}} + \frac{V_{s1}}{jwL_1} - g_{m1}V_{gs1} - \frac{V_{ds1}}{r_0} - V_{ds1}jw(\frac{C_{gd1}C_{gs1}}{C_{gd1} + C_{gs1}})$$

(2.74)

$$I_{in} = V_{s1} \left( \frac{1}{R_{in}} + \frac{1}{jwL_1} + g_{m1} + \frac{1}{r_0} + jw \left( \frac{C_{gd1}C_{gs1}}{C_{gd1} + C_{gs1}} \right) \right)$$

$$-g_{m1}V_{g1} - V_{d1}\left(\frac{1}{r_0} + jw\left(\frac{C_{gd1}C_{gs1}}{C_{gd1} + C_{gs1}}\right)\right)$$

(2.75)

For AC analysis,  $C_{in}$  can be shorted, and by neglecting the term  $V_{dl}$  and  $V_{gl}$ , and using Equations (2.73)~(2.75), we obtain Equations (2.76) and (2.77).  $V_{in} = V_{sl}$  by inserting this value and rearranging, so the input impedance  $Z_{in}$  is expressed by Equations (2.78) and (2.79).

$$I_{in} = V_{in} \left( \frac{1}{R_{in}} + \frac{1}{jwL_1} + g_{m1} + \frac{1}{r_0} + jw \left( \frac{C_{gd1}C_{gs1}}{C_{gd1} + C_{gs1}} \right) \right)$$

(2.76)

$$\frac{V_{in}}{I_{in}} = Z_{in} \quad (\Omega) \tag{2.77}$$

$$Z_{in} = \frac{1}{\left(\frac{1}{R_{in}} + \frac{1}{jwL_1} + g_{m1} + \frac{1}{r_0} + jw\left(\frac{C_{gd1}C_{gs1}}{C_{gd1} + C_{gs1}}\right)\right)}$$

(2.78)

where  $Z_{in}$  and output impedance  $Z_{out}$  of each stage are optimized at 24GHz.

$$Z_{in} = R_{in} / X_{L1} / \frac{1}{g_{m1}} / r_0 / X_C$$

(2.79)

where

$$X_{L1} = jwL_1$$

and  $X_C = \frac{1}{jw(\frac{c_{gd1}c_{gs1}}{c_{gd1}+c_{gs1}})}$ .

By assuming  $r_0=\infty$ , we get the simplified form of  $Z_{in}$  as shown below:

$$Z_{in} = R_{in} / / X_{L1} / / \frac{1}{g_{m1}} / / X_{C}$$

(2.80)

On deactivating the input source  $V_{in}$  and applying KCL at the output node, we can get output impedance  $Z_{out}$ . At the input node  $s_1$ , we also obtain Equations (2.81) and (2.82).

$$I_{s1} = g_{m1}V_{gs1} + \frac{V_{ds1}}{r_0} + V_{ds1}jw(\frac{C_{gd1}C_{gs1}}{C_{gd1} + C_{gs1}})$$

(2.81)

$$V_{s1} = I_{s1} \left[ \frac{R_{in} j w L_1}{R_{in} + j w L_1} \right]$$

(2.82)

By applying KCL at the output node  $d_4$ , inserting  $V_{d4} = V_{out}$ , and rearranging, we get Equations (2.83)~(2.87).

$$\frac{V_{out} - V_{s4}}{r_0} + g_{m4}V_{gs4} + \left[ \left( \frac{R_{out} + jwL_{out} \frac{1}{jwC_{gd4}}}{R_{out} + jwL_{out} + \frac{1}{jwC_{gd4}}} \right) + \frac{1}{jwC_{gs4}} \right] (V_{out} - V_{s4})$$

(2.83)

$$\frac{V_{out}}{r_0} + V_{out} \left[ \left( \frac{R_{out} + jwL_{out} \frac{1}{jwC_{gd4}}}{R_{out} + jwL_{out} + \frac{1}{jwC_{gd4}}} \right) + \frac{1}{jwC_{gs4}} \right] = I_{out}$$

(2.84)

$$Z_{out} = \left[\frac{1}{r_0} + \frac{R_{out} + jwL_{out}}{jwC_{gd4}(R_{out} + jwL_{out}) + 1} + \frac{1}{jwC_{gs4}}\right]^{-1} (\Omega)$$

(2.85)

$$Z_{out} = \left[\frac{1}{r_0} + \frac{1}{jwC_{gd4} + G_{out}} + \frac{1}{jwC_{gs4}}\right]^{-1}$$

(2.86)

where  $G_{out} = \frac{1}{R_{out} + jwL_{out}}$ , by assuming  $r_0 = \infty$ , we obtained the simplified

form of  $Z_{out}$  as shown below:

$$Z_{out} = \frac{jwC_{gs4}(jwC_{gd4} + G_{out})}{jw(C_{gd4} + C_{gs4}) + G_{out}}$$

(2.87)

Now let's get voltage gain. From the voltage and current of transistors  $M_1$ ,  $M_2$ ,  $M_3$  and  $M_4$ , we also obtain Equations (2.88)~(2.96).

$$V_{s2} = V_{d1} - I_{d1,d2} jw L_3 (2.88)$$

$$V_{d1} = I_{ds1}r_{01} + V_{s1}; (2.89)$$

$$V_{d4} = I_{ds4}r_{04} + V_{s4} = V_{out} (2.90)$$

As  $V_{s1} = V_{in}$  for transistor M<sub>1</sub> we get Equation (2.91).

$$V_{d1} = I_{ds1}r_{01} + V_{in} (2.91)$$

By rearranging Equations (2.88) and (2.90), we get Equation (2.92).

$$V_{s2} = I_{ds1}r_{01} + V_{in} - I_{d1.d2}jwL_3 (2.92)$$

As  $V_{s2} = V_{s3}$  for transistor M<sub>2</sub> and M<sub>3</sub>, we get Equation (2.93).

$$V_{s3} = I_{ds1}r_{01} + V_{in} - I_{d1,d2}jwL_3 (2.93)$$

As shown in Figure 2.8 we will get Equation (2.94).

$$V_{d3} = I_{ds3}r_{03} + V_{s3} (2.94)$$

By rearranging Equations (2.93) and (2.94), we get Equation (2.95).

$$V_{d3} = I_{ds3}r_{03} + I_{ds1}r_{01} + V_{in} - I_{d1,d2}jwL_3$$

(2.95)

As  $V_{d3} = V_{s4}$  for transistor M<sub>3</sub> and M<sub>4</sub>, we get Equation (2.96).

$$V_{s4} = I_{ds3}r_{03} + I_{ds1}r_{01} + V_{in} - I_{d1,d2}jwL_3$$

(2.96)

By rearranging Equations (2.90) and (2.96), we get Equation (2.97).

$$V_{out} = I_{ds1}r_{01} + V_{in} - I_{d1,d2}jwL_3 + I_{ds3}r_{03} + I_{ds4}r_{04}$$

(2.97)

The gain of the proposed LNA should be as large as possible to reduce the noise figure. And the voltage gain of proposed LNA is shown in Equation (2.104).

As shown in Figure 2.8 we can calculate  $A_{\nu}$  voltage gain.

$$A_{v1} = g_{m1}(R_{D1}//r_{01}) (2.98)$$

Where  $R_{D1} = (jwL_3//r_{02})$  represent the series resistance of  $L_3$

$$A_{v1} = g_{m1}(jwL_3//r_{02}//r_{01}) (2.99)$$

$$A_{v3} = g_{m3}(r_{03} / \frac{1}{g_{m4}} / / r_{04})$$

(2.100)

$$A_{v4} = g_{m4}(r_{04}//R_{out} + jwL_{out})$$

(2.101)

$$A_v = g_{m1}(jwL_3//r_{02}//r_{01}) \ g_{m3}(r_{03}//\frac{1}{g_{m4}}//r_{04})g_{m4}(r_{04}//R_{out} + jwL_{out})$$

(2.102)

$$A_v = g_{m1}g_{m3}g_{m4}((jwL_3//r_{02}//r_{01}) (r_{03}//\frac{1}{g_{m4}}//r_{04})(r_{04}//R_{out} + jwL_{out}))$$

(2.103)

If we assumed that  $r_{01} = r_{02} = r_{03} = r_{04} = r_0$  are same

$A_v$

$$=g_{m1}g_{m3}g_{m4}(\frac{jwL_3r_0}{2jwL_3+r_0})(\frac{r_0}{2+r_0g_{m4}})(r_0//R_{out}+jwL_{out})$$

(2.104)

By assuming  $r_0 = \infty$ , therefore we get Eq. (2.105).

$$A_{v} = g_{m1}g_{m3}g_{m4}(R_{out} + jwL_{out})\lim_{r_{0\to\infty}} \left(\frac{jwL_{3}r_{0}}{2jwL_{3} + r_{0}}\right)\lim_{r_{0\to\infty}} \left(\frac{r_{0}}{2 + r_{0}g_{m4}}\right)$$

(2.105)

After solving the above Eq. (2.105), can be further simplified as follows

$$A_{v} = g_{m1}g_{m3}g_{m4}(R_{out} + jwL_{out})\frac{jwL_{3}}{g_{m4}}$$

(2.106)

$$A_{v} = G_{T}(R_{out} + X_{Lout})(X_{L3})$$

(2.107)

where

$$X_{Lout} = jwL_{out}$$

,  $X_{L3} = jwL_3$  and  $G_T = g_{m1}g_{m3}$

Throughout the amplification phase the noise figure *(NF)* in LNA specifies the intrinsic LNA noise applied to the desired or desirable signal.

NF is a method of source admittance that looks through the two-port network input terminal. To achieve the  $NF_{min}$ , an optimum admittance, namely  $Y_{opt}$ , should be introduced to the network. The expressions for  $NF_{min}$  and  $Y_{opt}$  can be derived for a MOS device by considering a two-port network

model for the MOS device. The gate-source terminal in this configuration is the port of input, and the terminal drain-source is the port of output.

### 2.8.4. Implementation

The design plays a very major part in deciding the output of the chip produced in an RF circuit. The main factors to be considered in the RF layout are system matching and symmetry, parasites, current density in interconnections, thermal variations and substrate effects [47]. For some significant factors for RF layout, a thicker nanowire layer should be used to realize chip capacitors, and on-chip supply decoupling should be used to reduce high frequency noise of the power supply. In sensitive circuit areas physical structural element can also be used to avoid parasites.

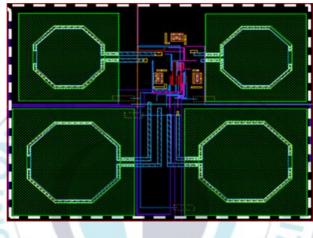

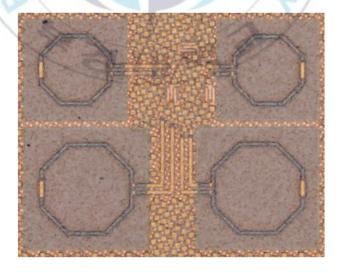

The Cadence software program is used to provide layout and post-processing of LNA. The circuits are designed and fabricated using 65nm RF CMOS technology. This technology offers six metal layers with two top layers of 0.6 $\mu$ m thick copper. Shield pads for inductors are employed at each port. Figure 2.9 and Figure 2.10 show layout and die photograph of the proposed LNA. Grounded metal underneath the pads prevents loss of the signal power and noise generation associated with the substrate resistance. Ground rings are placed around each transistor at minimum distance to

reduce the substrate loss. To minimize parasitic capacitance all transistors are designed by folded structure [48]. Signal lines are wide enough to meet electro-migration requirements. Ground lines were made wide to provide low impedance paths.

Figure 2.9. Layout of the 24 GHz LNA

Figure 2.10. Die photograph of the proposed LNA

The decoupling capacitor is added to bypass high frequency noise from the bias voltage. Grounded guard ring with substrate connection surrounds the inductor to minimize substrate noise. The MIM capacitors are used for high quality factors and the resistors of tantalum-nitride thin film are used. Large on-chip bypass capacitors are placed between each  $V_{DD}$  and ground. The die occupies  $0.60 \times 0.60 \text{mm}^2$  including pads and  $0.31 \times 0.35 \text{mm}^2$  without pads.

### 2.9. Measurement Results and Discussions

### 2.9.1. Measurement of S-Parameter and Noise Figure

The input and output pads are laid out in GSG configuration with a pitch of  $50\mu$ m to perform wafer level testing for LNA using a probe station with network analyzer. We performed 2-port measurements. The measurements are based on a separate LNA test chip. The power of  $-20 \, \mathrm{dBm}$  is applied from the synthesized sources at both port 1 and port 2. We applied the attenuators of  $0 \, \mathrm{dB}$  at both port 1 and port 2.

Obviously, downscaling of CMOS technologies has significant impact on the design of analog and radio frequency circuits. Particularly, in low supply voltage circuits, as the technology downscales, the available voltage headroom decreases, and so it makes the design procedure difficult. Additionally, since the voltage headroom is smaller, the low power consumption in wireless and electronic portable devices and applications is becoming more important. In analog and RF blocks, high output power with high efficiency is desirable, but with the above-mentioned limitations on the recent technologies, achieving these goals requires special attention on the designing circuits with new techniques and topologies. From Figure 2.6 and Figure 2.7, the proposed LNA showed total dc current of 3.825mA at 1.5V supply, so we obtained the lowest power consumption of 4.59mW as compared to conventional results [49], [50].

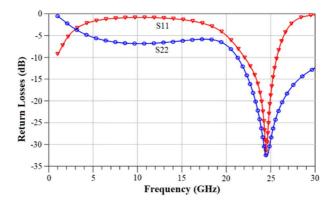

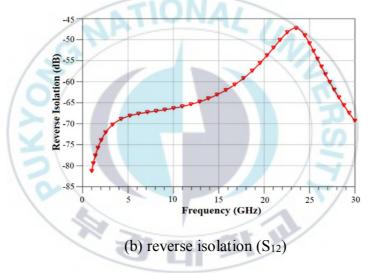

Figure 2.11(a) and (b) show input and output return losses ( $S_{11}$ ,  $S_{22}$ ) and reverse isolation ( $S_{12}$ ), respectively. Input and output impedance matching is so important to obtain low input and output return losses. Ideal input and output impedances of the amplifier must have  $45{\sim}50\Omega$  at the operation frequency. As shown in Figure 2.11, the LNA showed very low input return loss of -32.8dB, very low output return loss of -32.7dB, and very low reverse isolation of -47dB as compared to conventional results [52].

(a) Input and output return losses,  $S_{11}$  and  $S_{22}$ .

Figure 2.11. S-parameter for the proposed LNA.

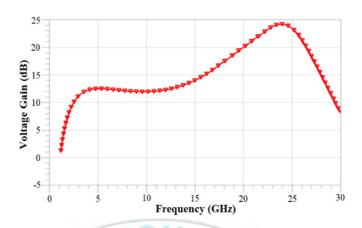

Voltage gain is very important parameter in GHz-band LNA. Figure 2.12 shows voltage gain (S<sub>21</sub>). As shown in Figure 2.12, the proposed LNA showed very high voltage gain of 24.3dB at the operation frequency of 24GHz as compared to conventional results [53], [54].

Figure 2.12. Voltage gain (S<sub>21)</sub>.

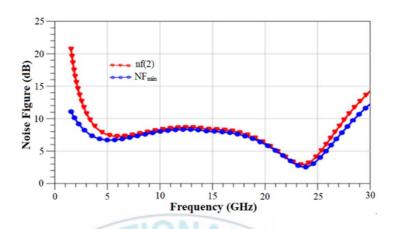

Figure 2.13 shows noise figure. Noise figure is measurement factor of degradation of signal-to-noise ratio (SNR) as the incoming signal from antenna traverses the receiver front-end. Mathematically, noise figure is defined as the ratio of the input SNR to the output SNR of the system. As shown in Figure 2.13, the proposed LNA showed very low noise figure of 2.98dB as compared to conventional results [55], [56].

Figure 2.13 Noise Figure

## 2.9.2. IIP3 and Stability Factor

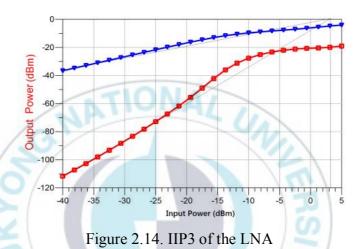

Figure 2.6 in previous session showed that the proposed common gate NMOS/PMOS technique inverted in between the input and output port of LNA & due to the inclusion of  $C_{in}$  &  $C_{1}$  the linearity increase.

From the figure 2.14 it can be observe that, to achieve high linearity or to achieve the low IIP3 distortion  $g_{m2}$  and  $g_{m3}$  should be reduced or minimized. The inclusion of inductor with proper size cancels the parasitic capacitive effects which results in an effective short circuit over a complete bandwidth. Under this condition, non-linearity of  $M_2$  can be neglected. The non-linearity drain current of  $M_1$  moves toward the  $M_2$  and  $M_3$  transistors which are utilized as CG configuration, and as a current buffer. The main responsibility of stage ( $M_2$  and  $M_3$ ) is to absorb non-linearity of  $M_1$  drain