#### 저작자표시 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

- 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

- 이차적 저작물을 작성할 수 있습니다.

- 이 저작물을 영리 목적으로 이용할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건

을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 <u>이용허락규약(Legal Code)</u>을 이해하기 쉽게 요약한 것입니다.

Disclaimer -

### 공학석사 학위논문

# VCO 주기마다 전하가 전달되는 구조의

루프필터를 가진 위상고정루프

전 자 공 학 과

김 민 욱

### 공학석사 학위논문

# VCO 주기마다 전하가 전달되는 구조의 루프필터를 가진 위상고정루프

2013년 2월 부경대학교 대학원 전자공학과

김 민 욱

# 김민욱의 공학석사 학위논문을 인준함

주 심 공학박사 최 혁 환 (인)

위 원 공학박사 문 광석 (인)

위 원 공학박사 최 영 식 (인)

## 목 차

### Abstract

| I . 서론 ··································                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Ⅱ. 위상고정루프의 기본 이론 3</li> <li>2.1 위상고정루프의 구조 및 이론 3</li> <li>2.2 기본 블록들의 동작특성 5</li> <li>2.2.1 위상 주파수 검출기 5</li> <li>2.2.2 전하펌프와 루프필터 8</li> </ul> |

| 2.2.3 전압 제어 발진기 ···································                                                                                                       |

| 2.3 전하펌프 PLL의 선형적 분석 ···································                                                                                                  |

| 3.1 PLL with Fvco-sampled 1st-order LF 구조 ·············15                                                                                                 |

| 3.2 PLL with Fvco-sampled 2nd-order LF 구조 ·······23                                                                                                       |

| 3.3 위상 주파수 검출기(Phase Frequency Detector) ·············· 27                                                                                                |

| 3.4 전하펌프(Charge Pump)29                                                                                                                                   |

| 3.5 전압 제어 발진기(Voltage Controlled Oscillator)30                                                                                                            |

| 3.6 주파수 전압 변환기(Frequency Voltage Converter) ······· 32 |

|--------------------------------------------------------|

| 3.7 주파수 분주기(Divider)34                                 |

|                                                        |

| Ⅳ. 시뮬레이션 결과35                                          |

| 4.1 시뮬레이션 결과35                                         |

| 4.1.1 PLL with Fvco-sampled 1st-order LF35             |

| 4.1.1 PLL with Fvco-sampled 2nd-order LF37             |

| 4.2 레이아웃                                               |

| 4.2.1 PFD                                              |

| 4.2.2 Charge Pump ———————————————————————————————————— |

| 4.2.3 Voltage Controlled Oscillator                    |

| 4.2.4 Frequency to Voltage Converter43                 |

| 4.2.5 LF Control(OR, NOR, NMOS)43                      |

| 4.2.6 Divider                                          |

| 4.2.7 Total PLL45                                      |

| 4.2.7.1 PLL with Fvco-sampled 1st-order LF 45          |

| 4.2.7.1 PLL with Fvco-sampled 2nd-order LF ······ 46   |

|                                                        |

| V. 결론 ···································              |

|                                                        |

| 참고문헌48                                                 |

#### A Phase-Locked Loop with Fvco-sampled Loop-Filter

#### Min-wook Kim

Department of Electronic Engineering, Graduate School,

Pukyong National University

#### Abstract

A phase-locked loop (PLL) with Fvco-sampled loop-filter has been proposed. Conventional PLL has loop-filter made of a resistor and capacitors. One of the proposed PLL structure, A PLL with Fvco-sampled 1st-order loop-filter, is working stably with the loop-filter consisted of capacotors and a switch. The proposed PLL is to reduce the fractional spur. Another structure, A PLL with Fvco-sampled 2nd-order loop-filter, is consisted of 2nd-order loop and a switch. The proposed PLL is to remove the fractional spur. It has been designed with a 1.8V 0.18 m CMOS process and proved by simulation with HSPICE. Layout of the proposed phase-locked loop has done by Cadence Virtuoso and Mentor Calibre Tool.

### I. 서 론

정보통신 기술이 급속도로 발전함에 따라 최근 개발되고 있는 고속 데이터통신 시스템이나 이동통신 단말기 등을 비롯하여 대부분의 디지털 제품에는 주파수합성기를 필요로 한다. 주파수 합성기란 낮은 위상 잡음을 가지는 원하는 주파수의 신호를 만들어 내는 회로이다. 주파수 합성기에는 수정발진 방식, 믹서 방식, 위상고정루프 방식 등이 있는데, 위상고정루프 방식이 가격이 저렴하고 집적화가 쉽기 때문에 일반적으로 사용되고 있다.

위상고정루프 (PLL)는 일반적으로 위상 주파수검출기(PFD), 전하펌프 (CP), 루프필터 (Loop Filter), 전압제어발진기 (VCO)와 주파수분주기 (Divider)로 구성되어 있다[1]. 위상고정루프에서 루프필터는 회로의 대역 폭과 위상고정 시간을 조절할 수 있다. 일반적으로 저항(R)과 커패시터(C)를 사용하여 LF(Loop Filter) 구조를 가지고 있는데, 출력 신호의 잡음을 더 많이 제거하기 위해 2차 루프필터 구조를 사용한다.

기존의 2차 RC 루프필터 구조에서 공정 변화에 민감한 저항을 없애고 커패시터로 만들어진 루프 필터를 가진 위상고정루프가 만들어 졌다. PFD에서 나오는 신호를 두 개의 CP와 다양한 스위치 구조를 사용하여 저항없이 커패시터만으로 안정적으로 동작하는 구조도 발표되었다[2-4]. 이 구조들은 두 개의 CP를 사용하고 각각의 커패시터를 동작시키도록 한다. 두커패시터에 전하가 공급되는 시간을 다르게, 즉 지연시킴으로써 저항과 같은 역할을 하게 하였다[2]. 또 다른 구조들은 두 개의 CP가 하나는 루프필터의 저항과 같이 동작하고 다른 하나는 커패시터로 동작하도록 각각의 경로가 스위치를 통해 합쳐지도록 하여 일반적인 2차 루프필터처럼 안정적으로 동작하도록 하였다[3-4].

저항 없이 커패시터만으로 동작하는 구조는 기존의 2차 루프필터에서 저항의 자리에 스위치를 사용하여 기준주파수 신호가 이를 제어하도록 되어있다. 이로 인해 저항이 하던 역할을 이 스위치가 대체하여 동작하도록 하였다. 그러나 이는 크기가 큰 기준주파수 스퍼를 발생시킨다는 단점이 있다. 논문 [2-4]에 발표된 구조에 비해 간단하게 커패시터와 하나의 스위치만 사용하여 위상고정루프 칩 크기를 줄일 수 있는 구조도 발표 되었다[5]. 논문 [5]에서 제안된 루프 필터의 구조는 간단하여 칩의 크기를 줄일 수 있었지만, 스퍼의 크기가 줄일 수 없었다. 루프 필터 출력 전압이 반주기가지난 다음 감소되므로, 즉 VCO 위상 변화를 일으키는 루프 필터의 출력전압이 반주기 동안 유지되어 스퍼의 크기가 커지게 된다.

본 논문에서는 높은 출력주파수를 가진 전압제어발진기(VCO) 출력 신호가 루프필터의 입력 신호로 사용되는 구조를 제안하였다. 제안된 구조는 더 안정적으로 동작하며 기준 주파수 스퍼를 크기를 억제 할 수 있다.

제안한 위상고정루프는 0.18µm CMOS 공정을 사용하여 HSPICE 시뮬레이션을 통해 결과를 검증하였다.

### Ⅱ. 위상고정루프의 기본 이론

### 2.1 위상고정루프의 구조 및 이론

위상고정루프(Phase-Locked Loop)를 구현하는 방법에는 여러 가지 방법들이 제안되어 왔다. 그중에 가장 보편적으로 사용하는 방법이 위상고정루프를 이용 하는 것인데, 그 이유는 위상고정루프는 낮은 위상잡음, 낮은 spurious tone 등 여러 가지 장점을 가지고 있기 때문이다.

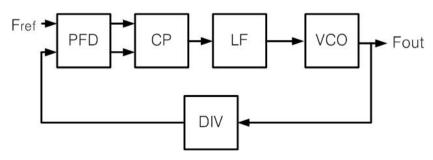

위상고정루프는 입력되는 주파수와 비교해 위상과 주파수가 같은 신호출력을 안정적으로 만들어 내는 회로이다. 위상고정루프의 특성 중 동작특성을 나타내는 지표는 위상잡음(phase noise), 위상고정시간(locking time), spurious tone 등이 있다. 이 지표들은 모두 위상고정루프의 대역폭에 의해영향을 받는다. 대역폭이 넓어지면, 위상고정 시간은 짧아지나 잡음특성이나빠지고, 대역폭이 줄어들면 반대의 효과가 나타나는 trade-off 관계이다. 대역폭은 위상고정루프에 인카되는 기준 주파수에 의존한다. 본 논문에서다루고 있는 위상고정루프는 전하 펌프 위상고정루프로 기본적인 블록 다이어그램은 그림2.1과 같다.

그림 2.1 기본 PLL 블록 다이어그램

일반적으로 위상고정루프는 위상주파수 검출기(Phase Frequency Detector), 전하펌프(Charge Pump), 루프 필터(Loop Filter), 전압제어발진기(Voltage Controlled Oscillator), 주파수 분주기(Divider)으로 구성되어 있다. 위상고정루프의 동작을 살펴보면, 위상 주파수 검출기는 외부로부터 입력되는 기준주파수 신호와 전압 제어 발진기에서 생성되는 신호의 위상과주파수를 비교하여 위상 및 주파수의 차이에 해당하는 신호를 출력하여 전하펌프를 구동한다. 전하펌프는 입력신호의 펄스폭에 비례하는 전류를 구동하여 루프 필터의 커패시터를 충전 또는 방전시킴으로써 전압 제어 발진기의 출력신호와 위상을 기준주파수의 위상과 주파수에 동일하게 만드는전압 제어 발진기의 제어전압을 발생시킨다.

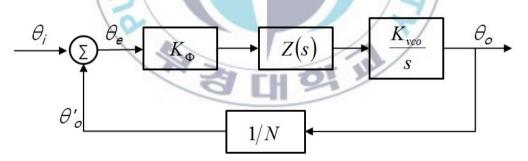

위상고정루프가 위상 고정되는 과정은 비선형적 과정이지만 위상 고정된 후에는 위상고정루프를 선형 모델링 할 수 있다. 그림2.2는 위상 고정 상태에서 위상고정루프의 선형모델을 나타낸다.

그림 2.2 위상 고정 상태에서의 위상고정루프 선형 모델

#### 2.2 기본 블록들의 동작특성

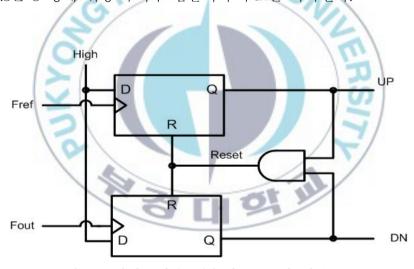

#### 2.2.1 위상 주파수 검출기 (phase frequency detector)

위상 주파수 검출기는 두 개의 주파수의 위상을 비교하여 위상차이가 발생하는 차이만큼의 신호(UP/DN)를 발생하는 회로이다. 일반적으로 위상주파수 검출기는 위상과 주파수 차이를 동시에 검출하는 순차회로인 3-상태 (3-state)위상 주파수 검출기 구조가 가장 보편적으로 사용되고 있다. 그림 2.3는 3-상태 위상 주파수 검출기의 구조를 나타낸다.

그림 2.3 위상주파수 검출기(PFD)의 기본 구조

3-상태 위상주파수 검출기는 2개의 D Flip-Flop과 1개의 AND 게이트로 구성되어 있다. 이 구조는 2개의 D Flip-Flop의 입력으로 기준 주파수 신호(Fref)와 전압제어 발진기(VCO)의 출력 주파수 신호(Fout)에 따라 동작하기 때문에 두 입력 신호의 듀티비에 대해 무관한 특성을 나타낸다.

그림 2.4는 3-상태 위상주파수 검출기의 상태도를 나타낸다. 위상주파수

검출기는 기준 신호와 전압 제어 발진기의 출력신호의 위상차이에 비례하는 폭을 가진 출력 펄스를 생성하고, 두 입력 중 빠른 위상을 가진 입력이어떤 것인가에 따라 UP, DN 펄스를 출력 신호로 내보낸다.

예를 들어, 기준 신호가 전압 제어 발진기의 출력 신호보다 위상이 빠르다고 하면, 그 위상차에 해당하는 펄스폭을 가지는 UP 신호를 출력한다. 반대로 기준 신호가 전압 제어 발진기의 출력 신호보다 위상이 느리다고하면, 마찬가지로 그 위상차에 해당하는 DN 신호를 출력한다.

위상주파수 검출기의 출력 UP 신호는 전하펌프를 구동시켜 루프필터의 커패시터를 충전하여 전압을 상승시킨다. 마찬가지로 DN 신호는 루프필터 의 충전된 전하를 방전하여 전압을 하강시킨다.

기준신호와 전압 제어 지연단의 출력 신호가 같아지면 이상적인 경우 위상주파수 검출기의 출력인 UP, DN 신호가 없고, 이에 따라 전하펌프의 구동이 없게 된다. 그리고 전하펌프의 전류 구동이 없기 때문에 루프필터의커패시터에 충전, 방전이 없게 되므로, 전압 제어 발진기의 입력제어전압은항상 일정한 값을 유지하게 된다. 그러나 실제의 경우, 위상주파수 검출기의 D Flip-Flop의 리셋 시간에 의해 리셋 펄스가 생성된다.

위상 주파수 검출기에 입력되는 두 입력 위상간의 위상차를  $\Delta \Theta$ 라디안이라 하면, 위상 주파수 검출기는 주기가  $1/f_{PFD}$  이고 펄스의 크기가 (duration)  $|\Delta \theta|/\omega_{PFD}(=2\pi f_{PFD})$  인 펄스를 발생시킨다. 전하펌프의 전류가  $I_p$ 라 할 때, 이는 전하펌프에 인가되어 한 주기 당  $I_p\Delta \theta/2\pi$ 의 전류를 루프필터에 전달해 준다. 이를 루프필터는 전압으로 바꾸어 주는 역할을 한다. 이를 수식으로 표현하면 식2-1과 같다.

$$V_{cont}(s) = \frac{1}{2\pi} \cdot I_p \cdot G_{LF}(s) \cdot \Delta\theta(s)$$

(2-1)

위의 수식에서  $V_{cont}$  는 루프필터의 출력 전압이며,  $G_{LF}$  는 루프필터의 전달함수이다.

#### 2.1.2 전하펌프와 루프필터

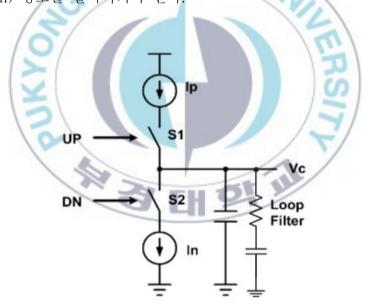

전하펌프는 위상 주파수 검출기의 출력신호인 UP, DN 신호에 의해 동작한다. 기준주파수와 피드백 주파수의 위상차이에 따라 UP이나 DN 신호의 크기가 정해지고 이 크기에 따라 전하펌프의 전류량이 조절된다. 위상고정루프에서 사용되는 전하펌프와 루프필터의 구성을 그림 2.5에 나타낸다. 전하펌프는 정전류 Source, Sink 그리고 UP, DN 신호에 의해 전류원을 ON/OFF 시키는 스위치로 구성된다. 전하펌프의 출력전압이 변동되지않도록 하는 것이 상당히 중요하므로 회로의 풀업(Pull-up)과 풀다운 (Pull-down) 경로를 일치사켜야 한다.

그림 2.5 전하펌프와 루프필터

전하펌프의 동작을 살펴보게 되면 UP신호가 'high'일 경우 전하펌프의 S1 스위치가 'turn on'이 되어 루프필터에 전류  $I_p$ 가 흐르게 되고, 이 루프 필터의 커패시터에 전하가 충전되어, 전압 제어 발진기의 입력제어전압인

Vc 전압이 서서히 상승하게 된다. 반대로, DN 신호가 'high'일 경우 전하 펌프의 S2 스위치가 'turn on'되어 루프필터에 전류  $I_n$ 이 흐르게 되고, 루프 필터의 커패시터에 충전되어 있던 전하가 방전되어 전압 제어 발진기의 입력제어전압인  $V_c$ 가 서서히 하강하게 되는 메커니즘을 갖는다.

또한 위상고정 상태에서 reset time에 스위치 SW1, SW2가 동시에 'turn on'되어 접지로 전류 경로가 형성되므로, 루프필터의 커패시터의 충전, 방전이 없게 된다. 따라서 전압 제어 발진기의 입력제어전압의 변동 없이 일정한 값을 갖게 된다.

전하펌프에 사용되는 스위치 소자는 MOSFET으로 스위치 S1의 경우는 P형 MOSFET, 스위치 S2의 경우는 N형 MOSFET을 사용하게 된다. 지연고정루프가 지연고정이 된 경우, 전하펌프에 흐르는 전류량 Ip, In의 크기는 같아야 한다. 그러나 스위치로 사용되는 P형 MOSFET, N형 MOSFET 소자의 이동도 차이, 위상주파수 검출기의 출력인 UP, DN신호에 의한 스위치 'turn on' 시간차이, MOSFET 스위치의 클록 피드스루(Clock Feedthrough), 전하공유(Charge Sharing)에 따른 전류 미스매치(mismatch)가 발생한다.

이러한 요소들에 의해 발생하는 전류 미스매치는 전압 제어 발진기의 입력제어전압이 출렁거리는 원인이 되고, 궁극적으로 지터를 발생하게 하는 주요 원인이 된다.

#### 2.2.2 전압 제어 발진기 (voltage controlled oscillator)

전압 제어 발진기는 입력전압에 비례하는 주파수를 발생하는 블록으로, 그 수식은 식2-2와 같다.

$$\omega_{out} = \omega_{free} + K_{vco} \cdot V_{cont} \tag{2-2}$$

위의 수식에서  $\omega_{free}$  는  $V_{cont}$  전압이 인가되지 않았을 경우의 전압 제어 발진기 free running frequency,  $K_{VCO}$  는 전압 제어 발진기의 이득을 의미한다. 위의 수식에서 전압 제어 발진기의 전달함수를 구하면 다음과 같다.

$$\Phi_{out}(s) = \frac{1}{s} \cdot K_{vco} \cdot V_{cont}$$

(2-3)

#### 2.2.3 주파수 분주기

출력 주파수를 입력 기준 주파수에 비해 높은 주파수를 가지게 하기 위해서는 전압 제어 발진기의 주파수를 그대로 사용하지 못하고, 주파수 분주기를 이용해서 주파수를 분주하게 된다. 이때 사용되는 주파수 분주기의특성에 따라 Integer-N, Fractional-N 방식으로 나누어진다.

### 2.3 전하펌프 PLL의 선형적 분석

루프의 동작특성을 s-domain에서 분석하면 개루프 전달함수와, 폐루프 전달함수는 식2-4 와 식2-5 같이 나타낼 수 있다.

$$H_{open} = K_{PFD} \cdot \frac{K_{VCO}}{s} \cdot G_{LF}(s)$$

(2-4)

$$H_{closed}(s) = \frac{K_{PFD} \cdot K_{VCO} \cdot G_{LF}(s)}{s + K_{PFD} \cdot K_{VCO} \cdot G_{LF}(s)}$$

(2-5)

위의 수식을 바탕으로 PLL의 개루프 전달함수는 식2-6과 같고, 폐루프의 전달함수는 식2-7로 나타낸다.

$$\frac{\theta_o(s)}{\Delta\theta(s)} = \frac{1}{2\pi} \cdot I_p \cdot G_{LF}(s) \cdot \frac{K_{VCO}}{s}$$

(2-6)

$$\frac{\theta_o(s)}{\theta_i(s)} = \frac{\frac{K_{VCO}}{s} \cdot \frac{I_p}{2\pi} \cdot G_{LF}(s)}{1 + \frac{K_{VCO}}{s} \cdot \frac{I_p}{2\pi} \cdot G_{LF}(s)}$$

(2-7)

$G_{LF}(s)$  는 루프 필터의 전달함수를 나타내고, 저역 통과 필터가 사용된다.

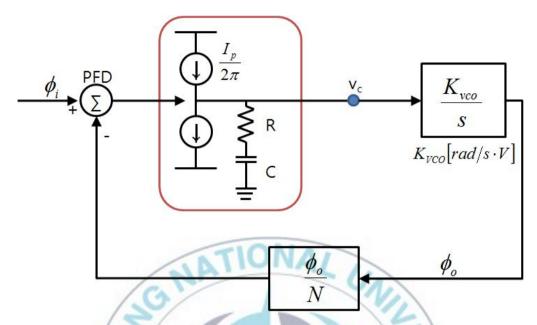

그림 2.6 2차 구조의 전하펌프 위상고정루프

그림 2.6은 루프필터에서 1차의 전달함수를 가지고 전압제어발진기에서 1차의 전달함수를 지니는 가장 기본적인 위상고정루프를 보인 것이다. 이구조는 Eq. 2.7를 이용하여 전개하면 식2-8과 같이 나타난다.

$$\frac{\phi_o}{\phi_i} = \frac{N\left(\frac{1}{N} \cdot \frac{I_p}{2\pi} \cdot R \cdot K_{VCO} \cdot s + \frac{1}{N} \cdot \frac{I_p}{2\pi} \cdot K_{VCO} \cdot \frac{1}{C}\right)}{s^2 + s \cdot \frac{1}{N} \cdot \frac{I_p}{2\pi} \cdot R \cdot K_{VCO} + \frac{1}{N} \cdot \frac{I_p}{2\pi} \cdot K_{VCO} \cdot \frac{1}{C}}$$

$$= \frac{2\zeta \omega_n \cdot s + \omega_n^2}{s^2 + 2\zeta \omega_n \cdot s + \omega_n^2}$$

(2-8)

그림 2.6과 같은 구조는 저항의 성분이 Ip에 의해 빠른 Vc 전압의 변화를 보이므로 전체 PLL의 출력에 원치 않는 신호(spur)가 크게 나타나는 등의 문제가 많이 발생하므로 거의 사용하지 않는 구조이다.

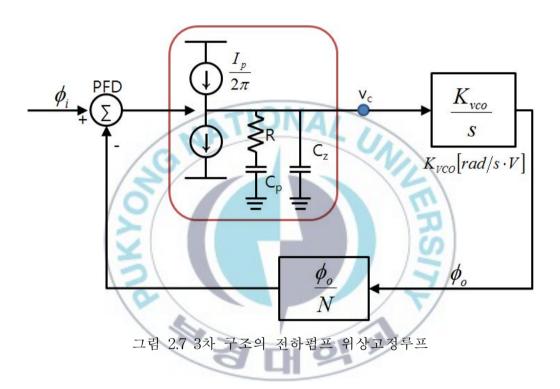

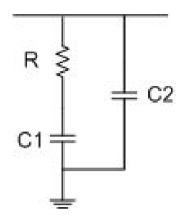

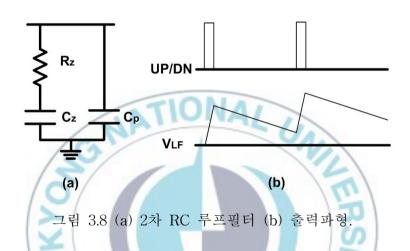

이에 비해 그림 2.7과 같이 2차 필터를 사용하여 3차의 루프를 구성하는 경우는 스퍼의 감소와 안정성을 기대 할 수 있다. 전달 함수에 있어서 2차 필터를 사용하면 두 개의 극점은 원점에 존재하고 나머지 하나의 극점과한 개의 영점을 이용하여 위상 마진을 고려하여 루프의 안정성을 보장하게하고, 대역폭을 조절하게 된다. 2차 필터는 그림 2.8과 같다.

그림 2.8 2차 루프 필터

2차 필터를 이용한 전체 PLL의 개루프와 폐루프의 전달함수를 구하면 다음과 같다.

$$H_{open}(s) = \frac{1}{2\pi} \cdot I_p \cdot \frac{1 + s \cdot R \cdot C_1}{s(C_1 + C_2) + s^2 \cdot R \cdot C_1 \cdot C_2} \cdot \frac{K_{VCO}}{s}$$

(2-9)

$$H_{closed}(s) = \frac{K_{VCO} \cdot I_p \cdot (1 + s \cdot R \cdot C_1)}{K_{VCO} \cdot I_p + K_{VCO} \cdot I_p \cdot R \cdot C_1 \cdot s + 2\pi (C_1 + C_2) s^2 + 2\pi \cdot R \cdot C_1 \cdot C_2 \cdot s^3} \quad (2-10)$$

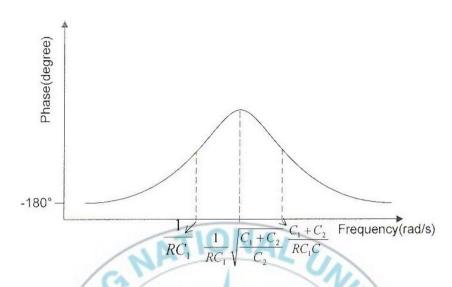

위의 식2-9에서 원점에 2개의 pole이 존재하고,  $\frac{C_1+C_2}{R\cdot C_1\cdot C_2}$  에 극점이 하나 존재하고,  $\frac{1}{R\cdot C_1}$ 에 하나의 원점이 존재한다. 위의 개루프 전달함수에 대한 위상에 대한 보드선도를 그리면 그림 2.9와 같다.

그림 2.9 3차 PLL의 위상특성

루프 필터의 차수에 따라, 그리고 R과  $C_1$ ,  $C_2$ 의 값에 따라 위의 식의 특성이 달라지므로 원하는 대역폭과 안정성을 고려하여 필터를 설계해야 한다.

### Ⅲ. 제안한 위상고정루프 설계

### 3.1 PLL with Fvco-sampled 1st-order LF 구조

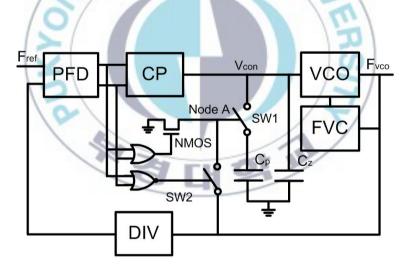

본 논문에서 제안한 1차 루프필터를 가진 위상고정루프의 형태는 그림 3.1과 같이 위상·주파수 검출기(PFD: Phase Frequency Detecter), 전하펌 프(CP: Charge Pump), 전압제어 발진기(VCO: Voltage Controlled Oscillator), 분주기(divider) 그리고 두 개의 커패시터와 스위치로 구성된 루프필터(LF: Loop Filter)로 구성하였다.

그림 3.1 제안된 위상고정루프

위상고정루프는 일반적으로 저항(R)과 커패시터(C)를 사용하여 2차 LF(Loop Filter) 구조를 사용한다. 제안한 구조는 루프필터의 저항을 없애고 VCO의 출력 신호에 의해 스위치(SW1)가 on/off 되는 구조이다. 기준

주파수 $(F_{ref})$ 와 분주기(DIV)의 출력 신호 $(F_{div})$ 의 위상 차이에 의해 발생된 UP/DN 신호를 OR, NOR 게이트를 사용하여 스위치(SW2)를 제어한다.

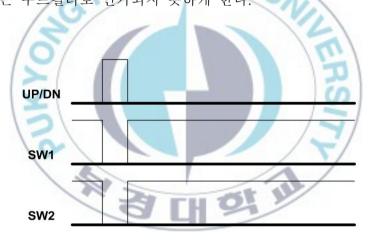

VCO의 출력주파수(F<sub>vco</sub>)는 OR와 NOR 게이트 출력 신호에 따라 루프필터로 입력된다. SW1은 OR 게이트에 의해 제어되는데, UP/DN 신호가 발생하면 OR 게이트의 출력이 "high"가 되어 NMOS를 "on" 시키고 노드 A를 접지시켜 SW1을 "off" 시킨다. SW2는 NOR 게이트에 의해 제어되는데, UP/DN 신호가 발생하면 NOR 게이트의 출력이 "off" 되어 SW2를 "off" 시킨다. 그림 3.2 와 같이 스위치는 UP/DN 신호가 발생하는 순간에만 "off" 되고 나머지 시간에는 "on" 되어 VCO 출력이 UP/DN 신호가 발생할 때에는 루프필터로 인가되지 못하게 한다.

그림 3.2 UP/DN 신호에 의한 스위치 동작

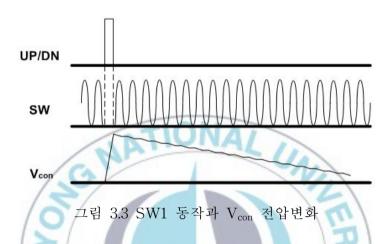

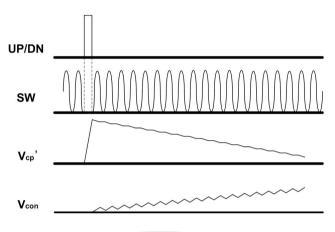

그림 3.3 은 회로에서 스위치들의 동작과  $V_{con}$  전압변화를 보여준다. SW1, SW2 는 UP/DN 신호가 발생하는 순간 외의 시간 동안은 항상 "on" 되어 있다. VCO의 높은 출력 주파수로 인해 SW1, SW2가 "on" 되어 있는 동안에는 스위치가 "on" "off"를 반복하게 되어 그림 3.3 과 같은 모양을 나타낸다. UP/DN 신호가 발생하는 순간에는 SW는 "off" 되고 Cz에만 전

하가 충전되었다가, UP/DN 신호가 꺼지고 SW1이 "on" 되면서 Cz에 충전되어 있는 전하를 Cp와 공유하게 된다. 이때  $F_{vco}$ 의 비교적 높은 주파수로 인해 "on" "off"가 반복되어  $V_{con}$ 은 그림 3.3 과 같은 모양을 나타낸다.

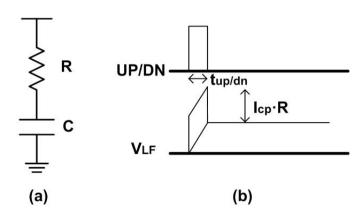

저항과 커패시턴스로 구성된 루프 필터의 구조는 그림 3.4 의 (a)와 같다. UP/DN 신호가 발생하면, 두 신호에 따라 전하펌프에서 전류가 루프 필터로 흘러 루프 필터 출력 전압이  $(V_{LF})$  그림 3.4 의 (b)와 같이 변한다. 이때 UP/DN 신호가 발생하는 시간을  $\triangle t$  라고 한다면,  $\triangle t$  시간동안 발생하는 위상 변화를 아래와 같이 수식으로 나타낼 수 있다.

$$\Delta \Phi = K_{vo} \int_{0}^{\Delta t} I_{cp} \cdot R dt = K_{vo} I_{cp} R \Delta t$$

(3-1)

그림 3.4 (a) RC 루프필터 (b) 출력파형

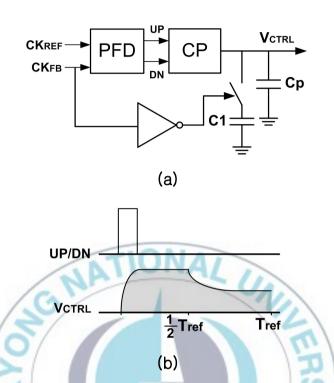

그림 3.5 는 기존에 2차 RC 루프필터에서 저항을 없애고 기준신호를 루프필터의 입력 신호로 사용되는 구조이다[5]. 이 구조는 기존의 2차 RC 루프필터의 저항과 커패시터 대신에 두 개의 커패시터, 하나의 스위치로 구성되어 있다. UP 신호에 의해 Cp 커패시터를 충전시켜 루프 필터 출력 전압이 변하며, 기준신호의 반주기 동안 그 값을 유지한다. 반주기 뒤에 스위치를 "on" 시키면서 Cp의 일부 전하가 C1으로 이동하여 그림 3.5 (b)처럼 출력 전압이 감소한다. 그림 3.5 (b) 출력 전압은 그림 3.4 (b) 와 같은 파형을 가지게 되어 스위치가 저항의 역할을 하는 것처럼 동작한다. 그러나 이 구조의 루프 필터에서는 출력 전압이 반주기 후에 감소 하므로 그림 3.5 (b) 에 나타난 바와 같이 반주기 동안 VCO 출력 신호에 많은 위상 변화가 일으켜 스퍼의 크기가 커지게 된다.

그림 3.5 (a) Half-duty sampled-feedforward 루프필터 (b) 출력파형

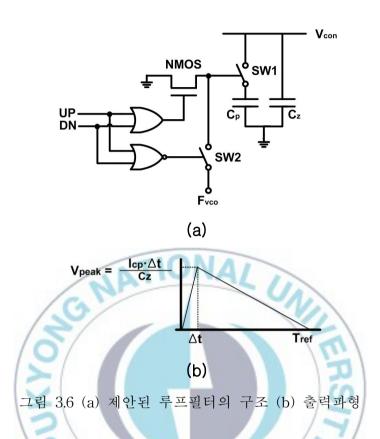

본 논문에서 제안하는 루프 필터는 VCO 출력 신호루프 필터의 입력 신호로 사용하여 논문 [5]에서 발생하는 스퍼의 크키를 억제하는 구조이다. 제안한 루프필터(LF)의 구조는 그림 3.6 의 (a)와 같이 VCO 출력 신호 F<sub>vco</sub>가 스위치를 통해 루프필터로 인가되는 구조이다. 그림 3.6 (b)의 루프 필터의 전압은 UP/DN 신호가 종료 되자마자 감소하기 시작하므로 음영으로 표시된 부분의 면적이 그림 3.5 (b)와 비교해 작아진다. 그러므로 VCO의 위상 변화가 작아져 스퍼의 크기가 줄어든다.

이 구조에서  $V_{con}$ 의 전압변화를 그림 3.6 (b)와 같이 UP/DN 신호가 발생한  $\triangle t$  시간동안 증가(감소) 했다가 나머지 시간( $T_{ref}$ - $\triangle t$ ) 동안 감소(증가) 한다고 가정하면 아래와 같이 수식으로 나타낼 수 있다. 이 구조에서  $V_{con}$  전압변화에 의해 발생하는 최대 크기의 위상 변화를 구하기 위해 그림 3.6 (b)의 음영으로 표시된 부분을 삼각형으로 추정하였다.

$$\Delta \Phi = K_{vco} \int_{0}^{T_{ref}} \frac{I_{cp} \Delta t}{C_{p}} dt = K_{vco} \frac{I_{cp} \Delta t}{C_{p}} \frac{T_{ref}}{2}$$

(3-2)

수식 (3-1)과 (3-2)를 같다고 본다면, 제안된 루프필터의 실효 저항 값을

다음과 같이 구 할 수 있다.

$$R_{eff.\text{max}} = \frac{1}{C_p} \frac{T_{ref}}{2} \tag{3-3}$$

따라서 제안된 루프 필터 구조에서는  $F_{vco}$ 의 주기와 커패시터의 크기에 저항 값이 결정된다고 볼 수 있다.  $C_p$ 가 작아지면 실효 저항 값이 증가하여 안정도는 증가하나  $V_{peak}$ 가 증가하여 기준 주파수 스퍼가 증가하므로 설계할 때 세심한 고려가 필요하다.

#### 3.2 PLL with Fvco-sampled 2nd-order LF 구조

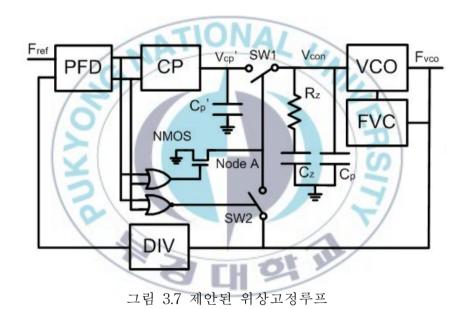

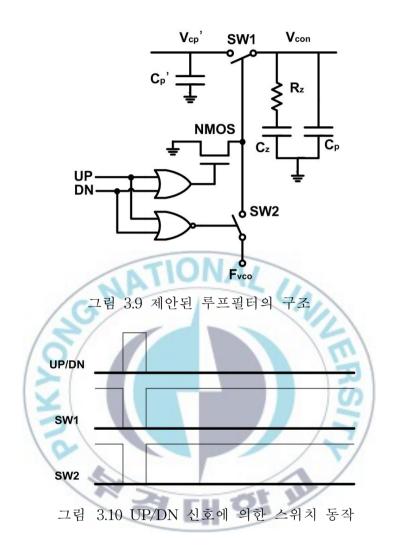

본 논문에서 제안한 2차 루프필터를 가진 위상고정루프의 형태는 그림 3.7과 같이 위상·주파수 검출기(PFD: Phase Frequency Detecter), 전하펌 프(CP: Charge Pump), 전압제어 발진기(VCO: Voltage Controlled Oscillator), 분주기(divider) 그리고 커패시터와 스위치, 2차 RC 루프필터 (LF: Loop Filter)로 구성하였다.

일반적으로 위상고정루프에서 사용하는 2차 루프필터는 그림 3.8의 (a)와 같이 저항과 두 개의 커패시턴스로 구성되어 있다. 위상주파수검출기 (PFD)에서 UP/DN 신호가 발생하면 전하펌프(CP)에서 전류가 루프 필터로 흘러 RC 딜레이에 따라  $C_p$ 를 먼저 충전 시켜  $V_{LF}$  전압을 상승(하강) 시킨다. UP/DN 신호가 종료되면  $C_p$ 에 충전되어 있던 전하가  $R_z$ ,  $C_z$  쪽으

로 흘러가면서 다시  $V_{LF}$ 가 하강(상승) 하는 동작을 하게된다. 이 2차 RC 루프필터의 동작은 기준주파수 $(F_{ref})$ 의 주기에 따라 동작을 반복하게 되어 기준주파수 스퍼가 발생하게 된다.

그림 3.9 는 제안한 루프필터의 구조이다. 일반적인 2차 루프필터 앞 단에 커패시터를 추가 하여 스위치(SWI)로 연결해놓은 구조이다. 이 스위치(SWI)는 전압제어발진기(VCO)의 출력(F<sub>vco</sub>)을 UP/DN에 의해 제어된 신호로 동작한다. VCO의 출력주파수(F<sub>vco</sub>)는 OR와 NOR 게이트 출력 신호에 따라 루프필터로 입력된다. SW1은 OR 게이트에 의해 제어되는데, UP/DN 신호가 발생하면 OR 게이트 출력이 "high"가 되어 NMOS를 "on"시키고 노드 A를 접지시켜 SW1을 "off"시킨다. SW2는 NOR 게이트에 의해 제어되는데, UP/DN 신호가 발생하면 NOR 게이트의 출력이 "off" 되어 SW2를 "off"시킨다. 그림 3.10 과 같이 스위치는 UP/DN 신호가 발생하는 순간에만 "off" 되고 나머지 시간에는 "on" 되어 VCO 출력이 UP/DN 신호가 발생할 때에는 루프필터로 인가되지 못하게 설계하였다.

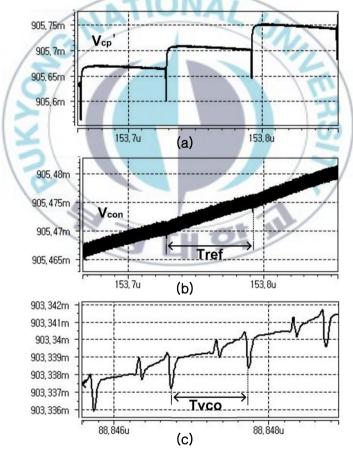

스위치(SW1) 동작에 따른  $V_{cp'}$  과  $V_{con}$  전압의 변화를 그림 3.11 에 나타내었다. SW1은 UP/DN 신호가 있을때만 off 가 되고, 나머지 구간에서는 항상 "on" 이 되는 동작을 한다. UP/DN 신호가 발생하면 그림 3.9의  $C_{p'}$ 을 충전(방전)하게 되어 전압이 상승(하강)하고, SW1이 on/off를 반복하면서 2차 루프필터에  $F_{vco}$  주기로 전하를 전달하게 되어  $V_{cp'}$ 과  $V_{con}$  전압은 그림 3.11 과 같은 파형을 나타낸다.

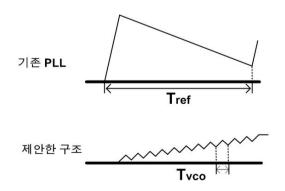

그림 3.11 SW1 동작과 Vcon 전압변화.

기준주파수( $F_{ref}$ )는 15.625MHz 이고 분주비는 64분주로 출력주파수( $F_{vco}$ )를 1GHz로 하였다. SW1이  $F_{vco}$ 에 따라 동작을 하게 되므로  $C_p$ '에 충전되어 있는 전하가  $F_{vco}$  주기로 2차 RC 루프필터에 전하를 전달하는 동작을 하게된다. 그림 3.12 는 기존의 2차 RC 루프필터와 제안한 구조의 동작을 비교한 그림이다. 기존의 기존의 2차 RC 루프필터를 사용했을 경우 기준주파수( $F_{ref}$ ) 주기로 동작을 하여 기준 주파수 스퍼를 유발하였지만, 제안한 구조의 루프필터는 기준주파수가 아닌  $F_{vco}$ 의 높은 주파수로 동작하기 때문에 기준주파수를 제거할 수 있다.

그림 3.12 2차 루프필터의 동작과 제안한 구조의 동작 비교

### 3.3 위상 주파수 검출기 (Phase Frequency Detector)

시스템이 고속화, 집적화됨에 따라 위상 주파수 검출기의 속도 향상을 위해서 본 논문에서는 간략화된 TSPC(True Single Pluse Clcok) CMOS 로직회로를 이용한 위상 주파수 검출기를 사용한다. 간략화된 TSPC CMOS 로직회로를 이용하면 위상주파수 검출기에서 사용되는 전체 MOSFET의 개수를 감소시킬 수 있어서, 전체 칩 면적과 파워 소모를 줄일 수 있다는 장점을 가진다.

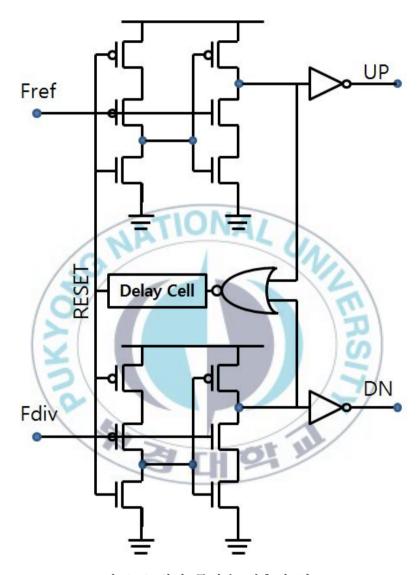

제안된 위상 주파수 검출기는 그림 3.13과 같이 TSPC(True Single Phase Clock)회로로 구성되어있다. TSPC 회로는 간단한 구조, 적은 전력소비와 빠른 스위칭 동작에 우수한 성능을 나타내기 때문에 널리 사용되어지고 있다. D-F/F은 6개의 MOS-Tr로 구성되고, 리셋은 NOR 회로를 사용하였다. 기준신호와 전압 제어 발진기 출력 신호의 위상차가 매우 작은경우에 위상 차이가 있음에도 불구하고 위상 차이를 검출하지 못하는 데드존(dead zone)문제와 in-lock 상태에서 위상주파수 검출기의 출력인 UP, DN 신호가 임펄스 형태의 파형을 갖기 때문에, 이 UP, DN 신호에 따른전하펌프의 충분한 스위칭 시간을 확보하기 위해 NOR 게이트 출력에 인버터 형태의 지연셀을 달아 준다.

그림 3.13 위상 주파수 검출기 회로

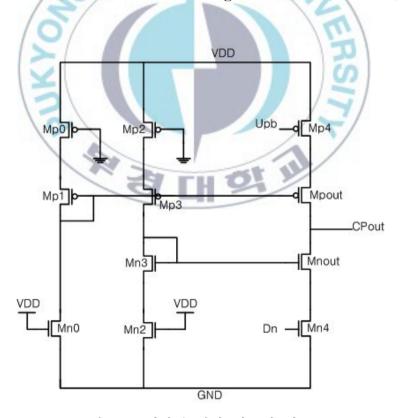

### 3.4 전하펌프(Charge Pump)

전하펌프는 PFD에서 출력된 up, down 신호를 입력받아 LF에 전류를 흘려줌으로써 VCO를 제어하는데 필요한 전압을 만들어 준다. 그림 3.14 는 제안된 전하펌프회로를 나타낸다. 제안된 전하펌프는 캐스코드 구조를 사용하여 전류 비대칭과 클록 피드스루(Feedthrough) 등을 최소화 하여 스퍼(spur)의 크기를 줄이고 잡음 특성을 개선하였다. 전류 미스매치가 발생하면 PLL의 성능을 저하시키므로 전류 미스매치현상을 최소화 하도록 Mp4와 Mn4의 사이즈를 선택하였다. Mpout, Mnout 은 갑작스러운 전류 스위 칭에 의한 클록 피드스루(clock feedthroutgh)를 줄이는 역할을 한다.

그림 3.14 제안된 전하 펌프의 회로

## 3.5 전압 제어 발진기 (Voltage Controlled Oscillator)

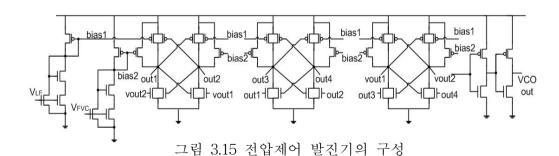

그림 3.15 은 전압 제어 저항(Voltage Controlled Resistor)과 3단 ring 구조를 사용한 전압 제어 발진기를 보여주고 있다. 전압 제어 저항을 사용할 경우 간단한 구조와 넓은 튜닝범위를 쉽게 변화시킬 수 있다는 것이 장점이다.

전압제어저항(VCR)은 그림 3.15 에 나타낸 VCO의 지연시간을 제어하는데 사용된다. 루프필터와 주파수-전압 변환기의 출력 전압인 VLF과 VFVC는 전압제어저항을 통해 VCO의 지연시간을 제어하는 전류로 변환된다. 전압제어저항은 입력전압의 변화를 큰 전류의 변화로 변환시켜줌으로써 VCO가 넓은 출력주파수 범위를 가지도록 해준다. VCO는 최대출력 전압진동폭과 낮은 위상잡음의 출력을 갖는 차동구조 지연단 세 개를 이용해구성하였다. PMOS와 NMOS 한 쌍의 트랜지스터가 CMOS 래치구조로 구성되어 지연단에 추가되었다. 이 래치 구조는 VCO가 낮은 출력위상잡음을 가지도록 하기 위해 지연단이 빠르게 켜지는 시간(on-time)을 갖도록 해준다. VCO는 루프필터와 주파수-전압 변환기로부터 입력되는 두 개의 전압제어저항을 가진다.

- 30 -

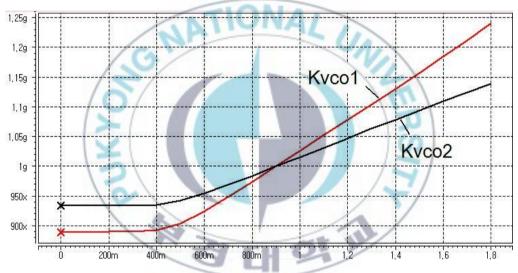

그림 3.16은 VLF(Kvco1)의 Gain값과 VFVC(Kvco2)의 Gain값을 동시에 나타내는 시뮬레이션 결과이다. 각각의 Gain은 기울기를 통해서 알 수 있다. 1차 루프필터를 가진 위상고정루프에서 Kvco1은 150Mhz/V, Kvco2는 50Mhz/V 의 값을 가지고, 2차 루프필터를 가진 위상고정루프에서 Kvco1은 330Mhz/V, Kvco2는 220Mhz/V 의 값을 가진다. 시뮬레이션에서 보듯이 두 입력전압이 0.9v 일 때, 두 Gain 그래프가 교차하게 되고, 이 때의 출력이 목표한 VCO출력인 1GHz이다.

그림 3.16 전압 제어 발진기의 전압-주파수 특성

### 3.6 주파수-전압 변환기(Frequency-Voltage Converter)

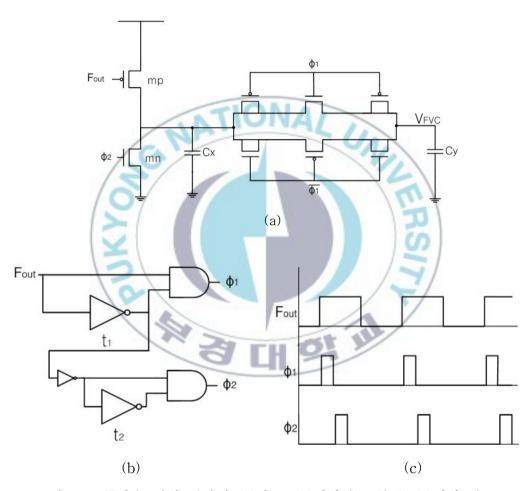

그림 3.17 는 제안한 위상고정루프에 사용된 주파수-전압 변환기의 회로를 나타낸다. 이 주파수-전압 변환기는 [5]에 사용된 구조를 간단한 구조로 변형한 주파수-전압 변환기이다. 사용된 변수 K는 식3-5와 같다.

$$K = I_{FVC} \frac{T_{out}}{2} \frac{1}{K' + 1} \tag{3-5}$$

여기서,  $I_{FVC}$ 는  $C_x$ 로 공급되는 전류량,  $T_{out}$ 은 PMOS로 입력되는 신호 (Fout)의 주기, K'는 Cy/Cx의 비율이다.

주파수-전압 변환기의 출력전압은 VCO 출력인  $F_{out}$ 의 주파수에 의해 결정된다.  $F_{out}$ 의 주파수가 높으면  $V_{FVC}$ 가 낮아지고,  $F_{out}$ 의 주파수가 낮으면  $V_{FVC}$ 는 높아진다. VCO의 출력 주파수가 변할 때마다 주파수-전압 변환기는 보상기로 역할을 하고, 이것은 VCO 잡음을 줄이게 된다.

주파수-전압 변환기는 두 개의 NMOS와 PMOS 트랜지스터, 두 개의 커패시터와 하나의 트랜스미션 게이트로 구성된 샘플링 스위치로 이루어지며, 이를 그림 3.17 (a)에 나타내었다. 출력신호에 샘플링 스위치의 클록 피드스루현상으로 인하여 레퍼런스 스퍼가 발생한다. 샘플링 스위치는 추가의 보상 트랜지스터를 양쪽으로 덧붙여 변형시킨 CMOS 트랜스미션 게이트이다. 이 트랜지스터들은 클록 피드스루현상을 줄여주는 효과를 낼 수있다.  $F_{out}$ 이 "low"일 때 PMOS가 동작되고, 커패시터  $C_x$ 에 전하가 충전된다.  $F_{out}$ 이 "high"일 때 PMOS는 동작을 멈추고,  $\Phi$ 1 신호에 의해 커패시터  $\Phi$ 2 신호에 충전된 전하가  $\Phi$ 3 전하가  $\Phi$ 5 전하가  $\Phi$ 7 전하가  $\Phi$ 8 전한  $\Phi$ 9 전하가  $\Phi$ 9 전하기  $\Phi$ 9 전

방전된다. 그림 3.17 (b)와 3.17 (c)는 제어 신호를 생성하는 회로와 파형을 나타내었다. 제어 신호 블록은 서로 중첩되는 부분이 없도록 하여 Φ1 과 Φ2 신호를 생성한다. 간단한 2분주기를 이용하여 VCO 출력의 "high/low" 비율이 일정하게 되도록 만들어 주었다.

그림 3.17 주파수-전압 변환기 (a)회로, (b)제어신호 블록, (c)제어 신호 타이밍

### 3.7 주파수 분주기 (Divider)

본 논문에서 제안된 위상고정루프의 분주기는 4분주 프리스케일러와 16 분주 메인 디바이더로 구성되어 있다. 그림 3.18은 출력신호의 지연을 최대한 줄인 구조의 E-TSPC(Expanded True Single Phase Clock) 회로이며, 제안한 주파수 분주기의 프리스케일러에 사용된 회로이다. 하나의 E-TSPC는 2분주이며, 4분주비를 내기 위해서 2개의 E-TSPC를 연결하여 분주기회로를 설계하였다.

그림 3.18 다이나믹 E-TSPC (Expanded True Single Phase Clock)

16분주 메인 디바이더는 Placement & Routing을 하여 분주비를 조절할 수 있도록 설계하였다. [p0:p4] 핀을 사용하여 1~31분주가 가능하도록 설계하였으며, 표 3.1은 [p0:p4]의 컨트롤전압에 따라 분주비를 나타낸 것이다.

| p4 | р3 | p2 | p1 | p0 | 분주비 |

|----|----|----|----|----|-----|

| 0  | 0  | 0  | 0  | 1  | 1   |

| 0  | 1  | 0  | 0  | 0  | 8   |

| 1  | 0  | 0  | 0  | 0  | 16  |

| 1  | 1  | 0  | 0  | 0  | 24  |

| 1  | 1  | 1  | 1  | 1  | 31  |

## Ⅳ. 시뮬레이션 결과

#### 4.1 시뮬레이션 결과

#### 4.1.1 PLL with Fvco-sampled 1st-order LF

본 논문에서 제안한 1차 루프필터를 가진 위상고정루프는 15.625 MHz의 입력 주파수를 가지고 출력 주파수는 1 GHz 이며, 분주비는 64 이다. 위상고정루프의 파라미터인  $I_{cp}$ =10uA,  $C_p$ =640pF,  $C_z$ =40pF,  $K_{vcol}$ =150 MHz/V,  $K_{vcol}$ =50 MHz/V, N=64 의 변수 값을 가진다.

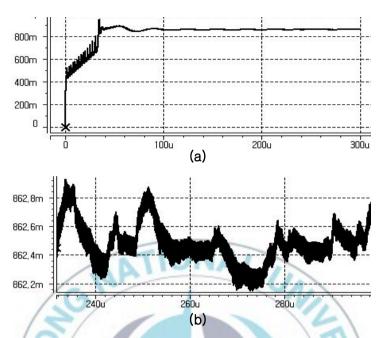

제안된 위상고정루프는 1.8V  $0.18 \mu m$  CMOS 공정 변수를 이용하여 HSPICE로 시뮬레이션을 수행하고 회로의 동작을 검증하였다. 그림 4.1 은 전압제어발진기(VCO)의 입력단  $V_{con}$ 이  $210 \mu s$ 에서 위상 고정이 되는 것을 확인 하였다. 위상이 고정된 후 루프필터 전압변화를 확인하기 위해 그림 4.2 에 나타내었다.

표 4.1은 전하펌프 전류와 두 개의 루프 필터 커패시터 크기를 변화 하여 시뮬레이션 한 결과이다. 위상고정 시간과 루프 필터 출력 전압 변동폭이 전하펌프 전류와 두 개의 루프 필터 커패시터 크기에 따라 변화하는 것을 보여 주고 있다. 표 4.1이 보여주듯이  $C_z$ 가  $C_p$ 에 비해 커질수록 루프 필터 출력 전압의 흔들림도 (한주기 동안 변화량 =  $\Delta V_{con}$ ) 작아지고 위상고정 시간도 줄어지는 것을 알 수 있다.

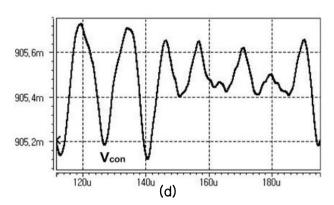

그림 4.1 시뮬레이션 결과 (a) 루프필터 (b) 위상고정된 후 전압변화.

그림 4.2 시뮬레이션 결과 (a) 스위치 제어신호 (b) 루프필터 전압변화

표 4.1. 시뮬레이션 결과

| I <sub>cp</sub> (μA) | C <sub>z</sub> (pF) | C <sub>p</sub> (pF) | t <sub>lock</sub> (µs) | △V <sub>con</sub> (mV) |

|----------------------|---------------------|---------------------|------------------------|------------------------|

| 50                   | 50                  | 200                 | 50                     | 3.2                    |

|                      | 50                  | 400                 | 40                     | 1.9                    |

|                      | 100                 | 400                 | 60                     | 2.4                    |

|                      |                     | 800                 | 40                     | 1.4                    |

|                      | 10                  | 40                  | 180                    | 5.8                    |

| 10                   | 10                  | 80                  | 140                    | 5.3                    |

| 10                   | 40                  | 160                 | 200                    | 2.2                    |

|                      |                     | 640                 | 160                    | 0.75                   |

# 4.1.2 PLL with Fvco-sampled 2nd-order LF

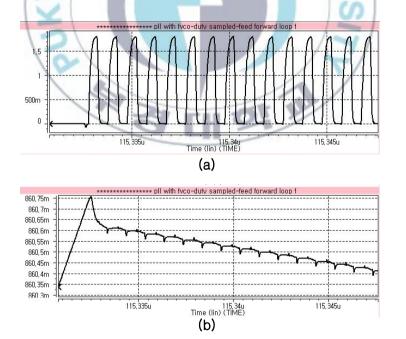

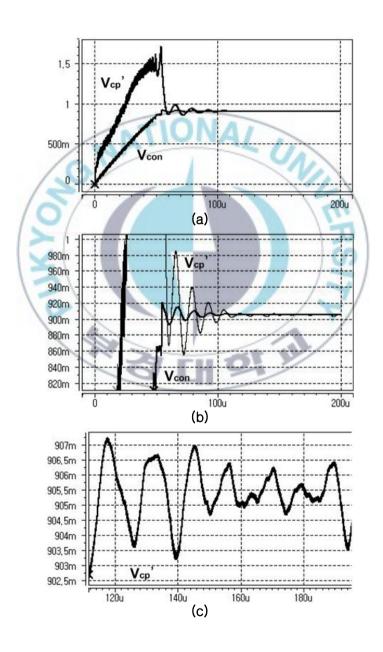

본 논문에서 제안한 2차 루프필터를 가진 위상고정루프는 15.625 MHz의 입력 주파수를 가지고 출력 주파수는 1 GHz 이며, 분주비는 64 이다. 위상고정루프의 파라미터인  $I_{ep}=20 uA$ ,  $R_z=0.5 k\Omega$ , Cz=5 nF, Cp=400 pF,  $C_p'=400 pF$ ,  $K_{vco1}=330 MHz/V$ ,  $K_{vco2}=220 MHz/V$ , N=64 의 변수 값을 가진다.

제안된 위상고정루프는 1.8V  $0.18 \mu m$  CMOS 공정 변수를 이용하여 HSPICE로 시뮬레이션을 수행하고 회로의 동작을 검증하였다. 그림 4.3의 시뮬레이션 결과 전압제어발진기(VCO)의 입력단  $V_{con}$ 이  $110 \mu s$ 에서 위상고정이 되는 것을 확인하였다. 위상이 고정된 후 루프필터 전압변화를 확인하기 위해 확대한 것을 그림 4.4에 나타내었다. 그림 4.4의 (a)는  $V_{cp}$  가  $V_{con}$ 의 전압변화를 비교한 것인데  $V_{cp}$  전압이 기준주파수 주기에 맞춰 동작하는 반면  $V_{con}$  전압은 더 높은 주파수에 맞춰 동작하는 것을 알 수 있

다. 이때  $V_{cp}'$  전압변화에서 주기마다 전압이 하강하는 것은 전하펌프의 미스매치에 의해 발생한 것이지만 VCO의 입력전압에 미치는 영향은 거의 없다. 그림 4.4의 (b)는 VCO 입력전압  $V_{con}$ 의 전압변화가  $F_{vco}$ 의 주기에 따라 변화하는 것을 확인하였다.

그림 4.3 시뮬레이션 결과 (a) 루프필터 전압변화 (b) 위상고정과정 (c) 위상고정된 후  $V_{cp}{}'$  전압변화 (d) 위상고정된 후  $V_{con}$  전압변화.

그림4.4 시뮬레이션 결과 (a)  $V_{cp}'$  전압변화 (b)  $V_{con}$  전압변화 (c) 확대한 루프필터 전압변화

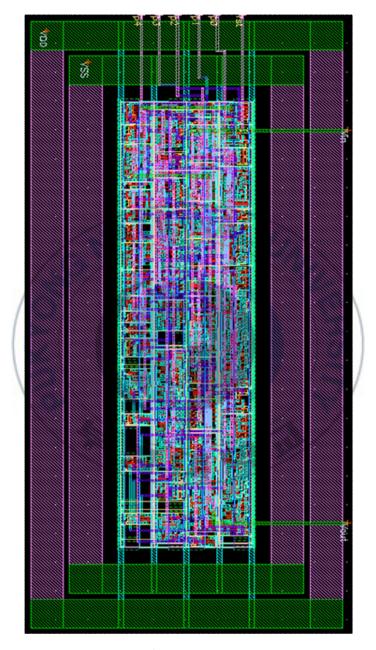

# 4.2 레이아웃(Layout)

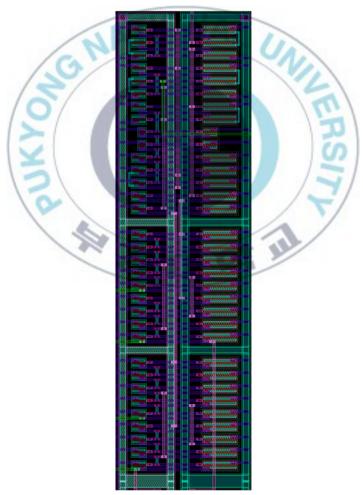

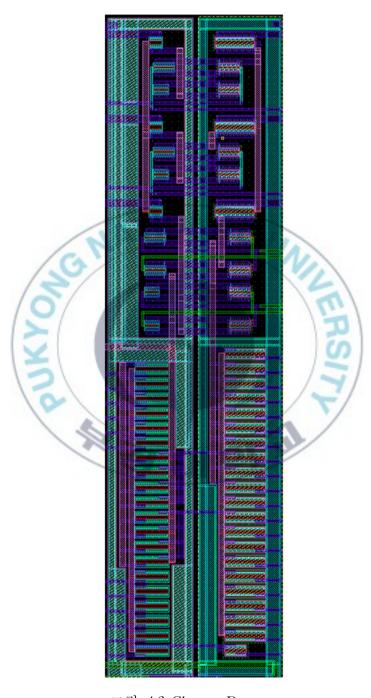

레이아웃은 Magna/Hynix 0.18μm 공정을 이용하여 Cadence사의 Virtuoso Tool로 구현하였고 Mentor사의 Calibre Tool로 검증하였다. 1차 루프필터를 가진 PLL의 크기는 230μm × 290μm 이고, 2차 루프필터를 가진 PLL의 크기는 240μm × 290μm 이다.

#### 4.2.1 PFD

그림 4.5 Phase Frequency Detector

# 4.2.2 Charge Pump

그림 4.6 Charge Pump

# 4.2.3 Voltage Controlled Oscillator

그림 4.7 Voltage Controlled Oscillator

# 4.2.4 Frequency to Voltage Converter

그림 4.8 Frequency to Voltage Converter

# 4.2.5 LF Control(OR, NOR, NMOS)

그림 4.9 LF Control(OR, NOR, NMOS)

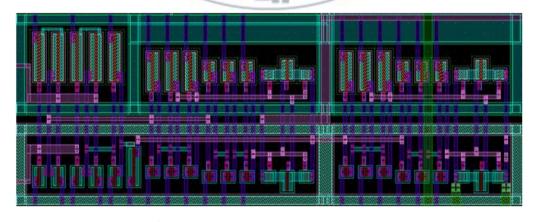

# 4.2.6 Divider

그림 4.10 Divider

## 4.2.7 Total PLL

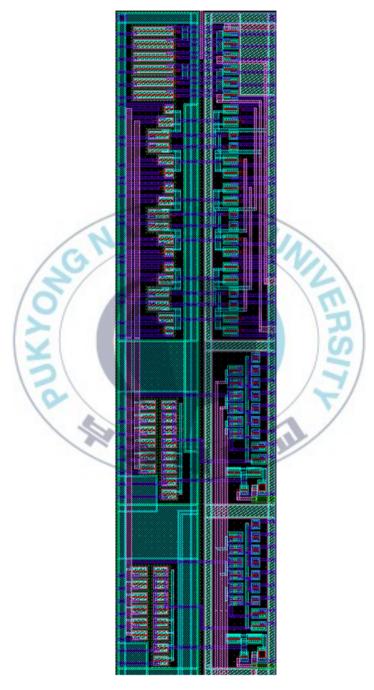

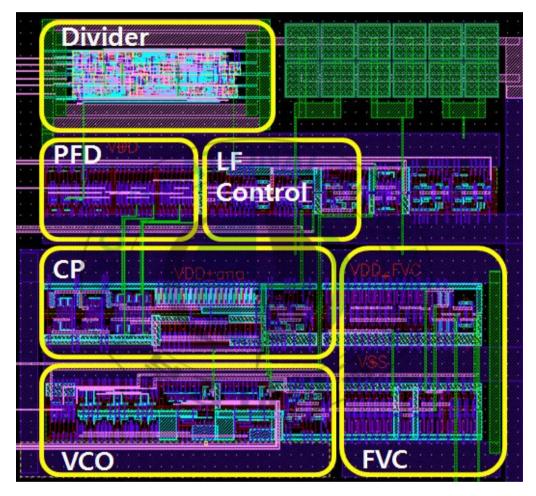

#### 4.2.7.1 PLL with Fvco-sampled 1st-order LF

그림 4.11 PLL with Fvco-sampled 1st-order LF

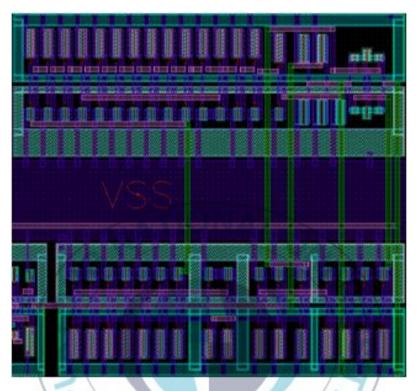

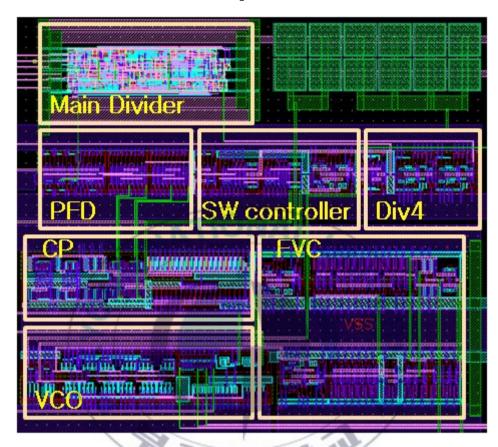

## 4.2.7.2 PLL with Fvco-sampled 2nd-order LF

그림 4.12 PLL with Fvco-sampled 2nd-order LF

## V. 결론

본 논문에서는 전압제어발진기(VCO)의 출력주파수를 샘플링하여 1차, 2차 루프필터에 입력되는 구조를 제안하였으며 시뮬레이션을 통하여 동작을 확인하였다. 1차 루프필터 구조에서는 두 개의 커패시터와 하나의 스위치로 루프필터를 구현하였다. 전압제어발진기의 출력주파수가 루프필터의 스위치를 제어하여 두 개의 커패시터가 충방전을 하게 하여 저항 역할을 하도록 하였다. 루프 필터 동작 신호를 기존 구조[5]와 달리 기준주파수를 사용하지 않고 전압제어발진기 출력 신호를 사용하여 기준 신호 스퍼의 크기를 감소시킬 수 있는 구조를 제시하였다.

2차 루프필터 구조에서는 기존의 2차 RC 루프필터 구조의 앞단에 커패시터를 추가하고 전압제어발진기(VCO)의 높은 출력주파수로 동작하는 스위치를 연결해 놓은 구조를 제안하였으며, 시뮬레이션을 통하여 동작을 확인하였다. 전압제어발진기의 출력주파수가 루프필터와 커패시터 사이의 스위치를 제어하기 때문에 2차 RC 루프필터의 전압변화가 기준주파수가 아닌 높은 출력주파수 주기로 동작하기 때문에 기준주파수 스퍼를 제거할 수있는 구조를 제시하였다.

제안된 위상고정루프는 Hynix/Magna 0.18µm CMOS공정을 기반으로 설계 제작되었으며 Synopsys의 HSPICE를 사용하여 시뮬레이션 하여 동 작을 검증하였다. 레이아웃 툴은 Cadence Virtuoso을 이용하여 회로를 구현하고, Mentor의 Calibre를 이용하여 DRC와 LVS를 통해 검증하였다.

## 참 고 문 헌

- [1] Floyd M. Gardner, "Charge-Pump Phase-Lock Loop", IEEE J. Tran, on Communications, vol. COM-28, no.11, pp. 1849-1858, Nov., 1980.

- [2] T. C. Lee and B. Razavi, "A stabilization technique for phase-locked frequency synthesizers," IEEE J. Solid-State Circuits, vol. 38, no. 6, pp.888-894, Jun. 2003.

- [3] A Maxim et al., "A low-jitter 125-1250-MHz process-independent and ripple-poleless 0.18-um CMOS PLL based on a sample-reset loop filter," IEEE J. Solid-State Circuit, vol. 36, no. 11, pp. 1673-1683, Nov. 2001.

- [4] J. G Maneatis et al., "Self-biased, High-bandwidth, low-jitter 1-to-4096 multiplier clock-generator PLL," IEEE J. Solid-State Circuits, vol. 38, no. 11, pp. 1795-1803, Nov. 2003.

- [5] A. Djemouai, M. A. Sawan, and M. Slamani, "New Frequency-Locked Loop based on CMOS Frequency-to-Voltage Converter: Design and Implementation", IEEE Tran. Circuit and Systems-II, vol. 48, no.5, pp. 441-449, May 2001.

- [6] R. Tao, and M. Berroth, "Low power 10GHz ring VCO using source capacitively coupled current amplifier in 0.12um CMOS technology", Electron. Lett., vol. 40, no.23, pp. 1484–1486, Dec. 2004.

- [7] Jaeha Kim, Jeong-Kyoum Kim, Bong-Joon Lee, Namhoon Kim, Deog-Kyoon Jeong and Wonchan Kim, "A20-GHz Phase-Locked Loop for 40-Gb/s Serializing Transmitterin 0.13-um CMOS", IEEE Journal of Solid-State Circuits, vol.41, no.4, April 2006.

- [8] 송윤귀, 최영식, "다중 전하펌프를 이용한 고속 위상고정루프", 대한 전자공학회논문지-SD 제46권 제2호, pp. 71-77, 2009.

- [9] 오정대, "자기잡음제거 전압제어발진기를 이용한 위상고정루프", 부경 대학교 대학원 2011.