#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

Disclaimer 🖃

## 공 학 석 사 학 위 논 문

용액공정을 통한 강유전체 기반 저전압 구동 전계효과 트랜지스터에 관한 연구

부 경 대 학 교 대 학 원

스마트그린기술융합공학과

박 병 찬

## 공 학 석 사 학 위 논 문

용액공정을 통한 강유전체 기반 저전압 구동 전계효과 트랜지스터에 관한 연구

이 논문을 공학석사 학위논문으로 제출함.

2023년 2월

부 경 대 학 교 대 학 원

스마트그린기술융합공학과

박 병 찬

박병찬의 공학석사 학위논문을 인준함.

2023년 2월 17일

위 원 장 공학박사 이 지 열

위 원 공학박사 백 강 준

위 원 공학박사 서민호

## 목 차

| 목 차                                      | i   |

|------------------------------------------|-----|

| List of Figures                          | iii |

| List of Tables                           | iv  |

| Abstract                                 | vi  |

| I. 서 론                                   | 1   |

| II. 이 론                                  | 3   |

| 1. 강유전체 (Ferroelectricity)               | 3   |

| 2. 산화물 반도체 (Oxode Semiconductor)         | 6   |

| 3. 전계 효과 트랜지스터 (Field-Effect Transistor) | 8   |

| 가. 전계 효과 트랜지스터의 구조                       | 8   |

| 나. 전계 효과 트랜지스터의 전기적 특성                   | 10  |

| III. 실험 및 분석                             | 11  |

| 1. 실험 재료                                 | 11  |

| 가. Indium Oxide / Gallium Oxide          | 11  |

| 나. Hafnium Oxide / Zirconium Oxide       | 11  |

| 2. 실험 방법                                 | 14  |

| 가. 기판 세척                                 | 14  |

| 나. 산화물 반도체와 강유전성 절연체의 박막 형성              | 14  |

| 다. 전극 증착                                 | 21  |

| 3. 측정 방법 및 측정 장비                         | 23  |

| 가. 전기적 특성 분석 장비                          | 23  |

| 나. X-Ray Diffractometer(XRD)             | 24  |

| 다. Atomic Force Microscope (AFM)         | 26  |

| IV. | 결과 및 고찰                        | .27  |

|-----|--------------------------------|------|

|     | 1. 습도에 따른 반도체 박막의 전기적 특성 평가    | 27   |

|     | 2. 게이트 절연충 코팅 온도에 따른 X선 특성 평가  | .32  |

|     | 3. 절연충 혼합 비율에 따른 박막의 모폴로지 변화   | .35  |

|     | 4. 절연층 혼합 비율에 따른 소자의 전기적 특성 비교 | .37  |

| v.  | 요 약                            | . 43 |

| 차   | 고 무 혀                          | 15   |

## List of Figures

| Figure 1. Polarization Hysteresis Loop                                  |

|-------------------------------------------------------------------------|

| Figure 2. Field Effect Transistor device structure8                     |

| Figure 3. Changes in the crystal structure of ferroelectric materials12 |

| Figure 4. Dielectric constants of hafnium oxide and zirconium oxide     |

| materials                                                               |

| Figure 5. Spin coating process schematic diagram                        |

| Figure 6. Oxide-only glove box in our LAB                               |

| Figure 7. Spin coater in our LAB                                        |

| Figure 8. Hot Plate in our LAB20                                        |

| Figure 9. Box Furnace for annealing                                     |

| Figure 10. Thermal Evaporation in our LAB                               |

| Figure 11. Vacuum probe station in our LAB23                            |

| Figure 12. Measurement Principles of XRD25                              |

| Figure 13. X-Ray Diffractometer measuring equipment25                   |

| Figure 14. Atomic Force Microscope & Principles of operation of         |

| a commercial AFM employing a bottom-side PZT scanner26                  |

| Figure 15. A schematic diagram of the hydrogen doping effect29          |

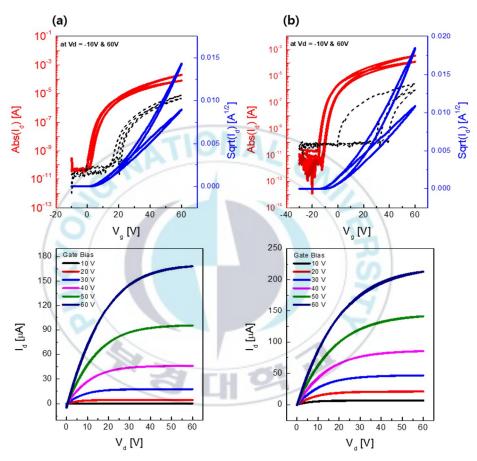

| Figure 16. Transfer curve and Output curve according to humidity        |

| (a) 20%, (b) 30%30                                                      |

| Figure 17. Transfer curve and Output curve according to humidity        |

| (c) 40%, (d) 50%31                                                      |

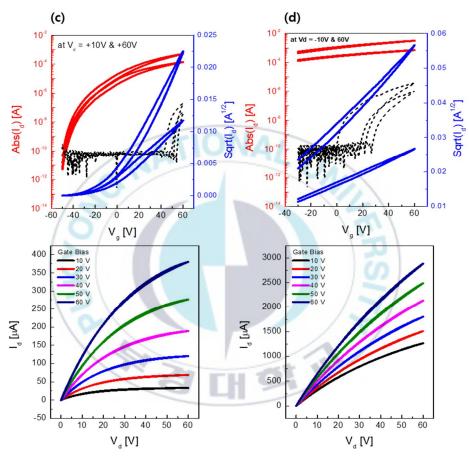

| Figure 18. The Graph of X-ray characteristics according to              |

| annealing temperature34                                                 |

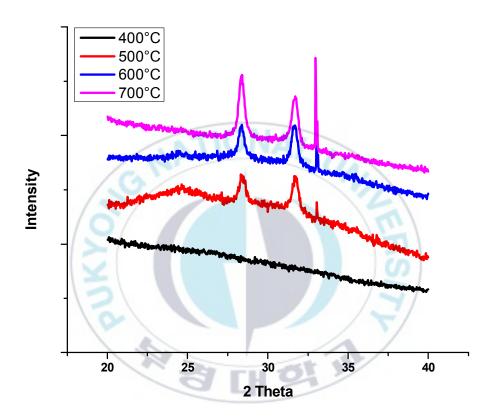

| Figure 19. AFM image according to Hafnium Zirconium Oxide ratio         |

| (a) 100:0, (b) 80:20, (c) 50:50, (d) 20:80, (e) 0:10036                 |

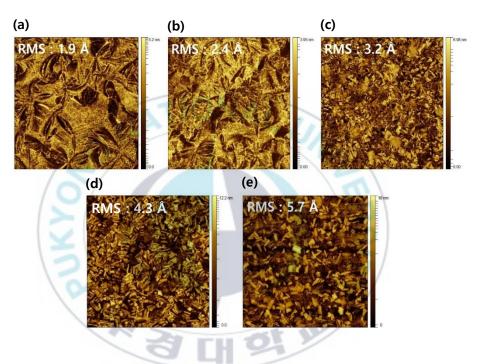

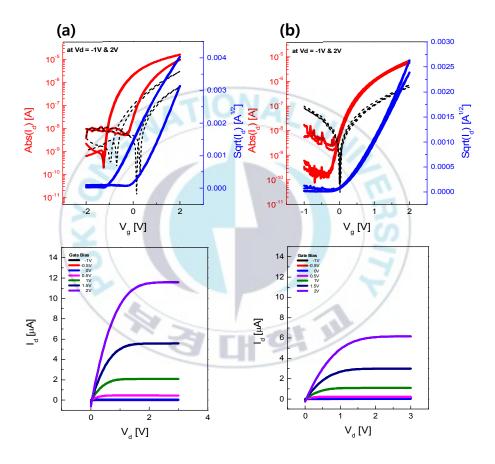

| Figure 20. Characteristic graph according to HZO ratio |    |

|--------------------------------------------------------|----|

| (a) 100:0, (b) 80:20                                   | 39 |

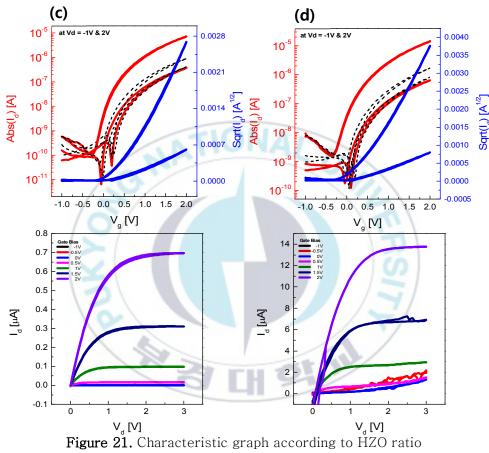

| Figure 21. Characteristic graph according to HZO ratio |    |

| (c) 50:50, (d) 20:80                                   | 40 |

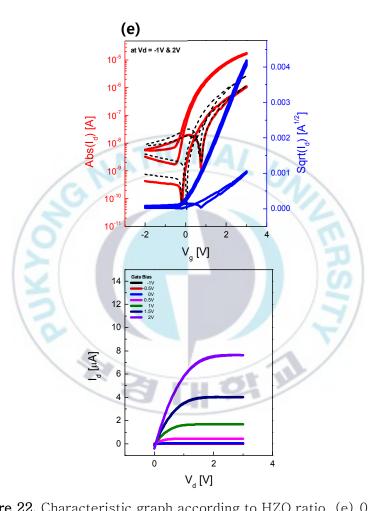

| Figure 22. Characteristic graph according to HZO ratio |    |

| (e) 0:100                                              | 41 |

## List of Tables

| Table 1. Summary of semiconductor layer's electrical properties accor   | ding to |

|-------------------------------------------------------------------------|---------|

| humidity                                                                | 42      |

| Table 2. Summary of gate dielectric layer's electrical properties accor | ding to |

| ratio                                                                   | 42      |

#### A Study on Ferroelectric-Based Low Voltage Driving Field Effect Transistor with Solution Process

#### Byeong Chan Park

# Department of Smart Green Technology Engineering Pukyong National University

#### Abstract

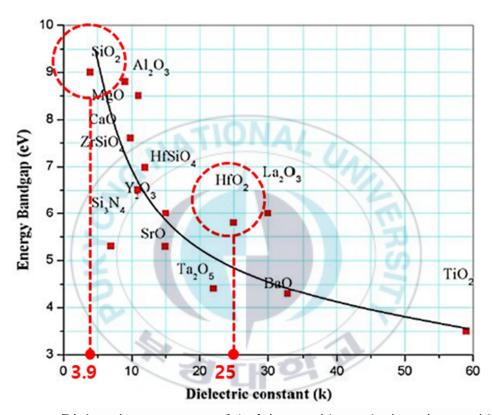

The rapid development of metal oxide semiconductor integrated circuits and the high integration of transistors have greatly promoted the development of the nano-scale electronic industry. However, in order to realize high-performance electronic devices in line with the developing industry, not only high electron mobility but also a thin thickness of several nanometers suitable for miniaturized transistors and precision electrical characteristics are required. It is essential to develop a semiconductor material technology that can be adjusted to. In the case of conventional SiO<sub>2</sub>, when the Dielectric Layer is reduced to a certain thickness or more, a tunneling effect occurs, resulting in a sharp increase in leakage current and an inability to function properly as a gate Dielectric layer. Therefore, in accordance with the industrial issue of high integration of devices, low-voltage ferroelectric field effect transistors (FE-FETs) or Ferroelectric Random Access memory

applications (FERAM) using high-k materials with high permittivity are being developed. A ferroelectric-based transistor device, which can be realized by replacing a gate insulating layer with a ferroelectric dielectric layer in a commonly used FET structure, has received a lot of attention and continuous research and development from the early stage of development of next-generation non-volatile memory technology. Currently, perovskite structure-based ferroelectric materials such as Pb(Zr,Ti)O3 (PZT) and SrBi2Ta2O9 (SBT) are most commonly used, and ferroelectric materials with this structure are compatible with silicon. The surface layer formed at the interface is irregular, which reduces the overall polarization and can reduce ferroelectricity. In addition, it is pointed out that it is difficult to realize transistor characteristics that are excellent in physical properties unique to the material, such as high leakage current due to low bandgap energy. In contrast, binary metal oxides, which have recently emerged as new ferroelectric materials, have a relatively high bandgap energy (5.7 eV) compared to conventional materials, and are only a few nanometers thick. Therefore, the leakage current can be reduced, and excellent electrical characteristics of the transistor can be achieved. In this research, we proposed a method to fabricate FE-FETs that can be driven at low power using Hafnium oxide and Zirconium oxide, which are ferroelectric materials with non-volatile memory properties, as gate insulators. A metal oxide semiconductor of indium oxide and gallium oxide was used as the active layer, and a ferroelectric material prepared by mixing hafnium oxide and zirconium oxide in various ratios was replaced with the gate insulating layer. After fabricating a ferroelectric-based field effect transistor, the effect of the ferroelectric gate insulating film on the electrical characteristics of the transistor was compared.

## I. 서론

금속 산화물 반도체 집적회로가 급속도로 발전하게 되고 트랜지스터의 고 집적화가 진행됨에 따라 나노 스케일의 전자 산업 발전이 크게 촉진되었다. 그러나 발전하는 산업에 맞춰 고성능의 전자소자를 구현하기 위해서는 높은 전자 이동도뿐만 아니라 소형화되는 트랜지스터에 적합한 수nm의 얇은 두깨, 그에 따른 전기적 특성을 정밀하게 조절할 수 있는 반도체 소재 기술의 개발이 필수적이다. 기존 SiO2의 경우 절연층 박막이 특정 두께 이상으로 줄어들 경우 Tunneling 현상이 발생하게 되고 이로 인해 의해 누설전류가 급격히 증가하여 게이트 절연층의 역할을 제대로 하지 못하게 된다. 따라서 소자의 고집적화라는 산업적 이슈에 따라 높은 유전율을 가진 High-k 물질을 사용한 저전압 강유전성 전계 효과 트랜지스터(FE-FET)또는 비휘발성 메모리 어플리케이션(FERAM)의 개발이 이루어지고 있으며, 일반적으로 사용되는 FET 구조에서 케이트 절연막을 강유전성 절연층 박막으로 대체함으로써 실현할 수 있는 강유전체 기반 트랜지스터 소자는 차세대 비휘발성 메모리 기술의 개발 초기 단계부터 많은 관심과 지속적인연구 개발이 진행되었다.

현재 Pb(Zr,Ti)O<sub>3</sub> (PZT), SrBi<sub>2</sub> Ta<sub>2</sub> O<sub>9</sub> (SBT)등의 페로브스카이트 (Perovskite) 구조 바탕의 강유전체 물질이 가장 많이 사용되고 있으나 이 구조의 강유전성 물질들은 실리콘과의 계면에 형성되는 표면층이 불규

칙적이고 이로 인해 전체 분극이 줄어들어 강유전성을 감소시킬 수 있다. 또한 낮은 밴드갭 에너지에 의해 높은 누설전류가 발생하게 되는 등 소재고유의 물성이 우수한 트랜지스터 특성을 구현해 내기에는 어렵다는 문제점이 지적되고 있다. 그에 비해 최근 새로운 강유전체 물질로 떠오르고 있는 이원계 금속 산화물은 기존의 물질에 비해 상대적으로 높은 밴드갭 에너지(5.7eV)를 가지고 있어 수nm의 얇은 두께에서도 누설전류를 줄일 수 있고 트랜지스터의 우수한 전기적 특성 구현이 가능해진다.

본 연구에서는 비휘발성 메모리 특성을 갖는 강유전성 물질인 Hafnium oxide와 Zirconium oxide를 게이트 절연막으로 사용하여 저전력에서 구동이 가능한 FE-FET를 제작하는 방법을 제안하였다. Indium Oxide와 Gallium Oxide의 금속 산화물 반도체를 활성층으로 사용하고 Hafnium Oxide와 Zirconium Oxide를 다양한 비율로 혼합하여 제조한 강유전체 물질을 게이트 절연층으로 대체하여 강유전체 기반 전계 효과 트랜지스터를 제작함으로써 강유전성 게이트 절연막이 트랜지스터의 전기적 특성에 어떠한 영향을 미치는지 비교하였다.

## II. 이론

### 1. 강유전체 (Ferroelectricity)

강유전체란 절연층(Dielectric Layer) 역할을 할 수 있는 유전체의 일종으로 일반적으로 유전율이 높은 High-k 물질을 의미한다. 강유전체는 외부의 전기장이 제거되었을 때에도 자발적 분극(Spontaneous Polarization)을 형성할 수 있는 특징을 가지고 있으며 외부 전기장에 의해 분극이 Switching되는 현상을 보인다. 또한 강유전체는 특정 온도 이상에서 특정온도에서 상전이 현상을 보이며, 이 온도를 큐리 온도(Curie Temperature)라고 부른다. 큐리 온도 이하에서는 전기 쌍극자 사이의 상호작용으로 인해 자발 분극이 무작위의 방향으로 배열되고 있어 강유전상을 보이게 되며, 큐리 온도 이상에서는 자발 분극이 소실되고 특정한 한방향으로 배열되는 상유전상으로 바뀌게 된다.

기존의 강유전체 물질은 페로브스카이트(Perovskite) 구조를 가진 물질을 많이 사용하였다, 하지만 페로브스카이트 구조의 강유전체 물질들은 Si 기판과의 호환성이 떨어지거나 큰 금속 원자의 크기 때문에 얇은 박막 성장에 불리하다는 한계가 있다. 따라서 이러한 문제점을 보완할 수 있는 강유전체 물질을 필요로 하게 되었고, HfO2나 ZrO2와 같은 얇은 두께의 박막에서도 강유전성이 나타나는 플루오라이트(Fluorite) 구조의 강유전체 물

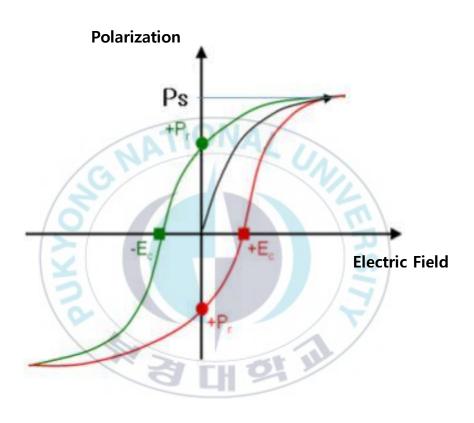

질이 발견되면서 이를 적극적으로 활용할 수 있는 연구가 활발히 이루어지고 있다. Ferroelectric 특성은 이력곡선(hysteresis loop)을 통해 나타낼수 있으며, 이력곡선이란 외부 전기장(E)에 따른 분극(P)의 변화를 나타내는 강유전체의 가장 대표적인 특성이다. 강유전체의 자발분극이 외부 전기장에 따라 역전되는 현상에 의해 나타내는 것으로 전기장의 방향과 세기에 따른 분극 상태의 변화를 보여준다. 강유전체의 분극은 잔류 분극 (Remanent Polarization, Pr)와 항전계 (Coercive Field, Ec)로 나눌 수 있으며, 잔류 분극은 외부에서 전압이 인가되면 전계를 형성하여 분극이 증가하게 되며, 이때 일정 일정한 전기장 이상에서는 분극이 증가하지 않고 포화상태로 외부 전기장에 따른 선형적인 증가만 보이게 된다. 잔류 분 극은 외부의 전기장이 제거된 후에도 분극은 0으로 돌아가지 않고 일정한 분극값을 가지게 되는 것을 의미한다. 또한 항전계는 전기장이 제거된 이후에도 남아있는 분극을 다시 0으로 되돌리기 위해 가해주는 반대 방향의 전기장을 의미한다.

강유전체는 다양한 분야에 적용되고 있으며, 비휘발성 메모리인 Ferroelectric Random Access Memory(FRAM) 가장 대표적이다. FRAM은 강유전체의 특징으로 인해 다른 메모리와는 다르게 전원이 차단되어도 그대로 남아 있는 비휘발성이라는 특징이 있으며 저전압에서 디바이스의 구동이 가능하고 빠른 스위칭 속도로 인해 플래시 메모리보다 10배 이상의 빠른 속도로 읽기/쓰기가 가능하다는 장점이 있다.

Figure 1. Polarization Hysteresis Loop

#### 2. 산화물 반도체 (Oxide Semiconductor)

산화물 반도체는 기존의 실리콘만을 사용하여 만든 반도체가 아니라 실리콘 위에 산화물 막을 올려 트랜지스터 구동에 필요한 전자의 흐름을 더욱 원활하게 만든 반도체이다. 비정질 실리콘은 sp3 오비탈로 구성되어 있어 전도대에서 전자의 이동이 부자연스럽지만 산화물 반도체의 경우 s오비탈로 구성되어 있어 전자의 이동이 상대적으로 자연스럽게 이루어 지므로 nm단위로 얇아지고 있는 소자에서도 전도성을 유지할 수 있다는 장점이 있다. 또한 산화물 기반 반도체 소자는 넓은 밴드 갭으로 인해 누설 전류가 극히 낮기 때문에 기존의 Si 반도체를 대체 가능할 것이라고 예상된다.

산화물 반도체는 기본적으로 화합물 반도체의 범주에 들어가기 때문에 물질을 이루는 성분 원소의 결핍이나 수소 원자의 존재 등이 결함으로 작용하게 된다. 산화물 반도체는 대부분 N-Type 물질이므로 산소의 결핍과도핑된 수소가 전자 이동의 주된 캐리어 역할을 하고 있어 산화물 반도체의 전기적 특성에 주요한 영향을 끼치는 것으로 알려져 있다. 따라서 산소공공과 수소 도핑에 의해 트랜지스터의 전기적 특성이 영향을 받음으로써반도체 박막 형성 공정을 위한 산화물 반도체의 물성 조절이 중요하다.

산화물 TFT의 특성은 전자 이동도, 문턱 전압, on/off ratio, subthreshold swing(S.S)등으로 규정 지어지고, 이들의 특성은 Gate 전극, 게이트 절연막, 반도체 박막, Source/Drain등에 의해 총체적으로 결정된다. 산화물

TFT의 우수한 특성 확보를 위해서는 산화물 반도체 박막에 존재하는 결함의 조절, 우수한 품질의 Gate 절연막, 트랜지스터의 구조와 각 전극의적절한 선택이 중요한 영향을 미치게 된다.

#### 3. 전계효과 트랜지스터 (Field-Effect Transistor)

전계 효과 트랜지스터(FET)는 게이트(Gate), 소스(Source), 드레인 (Drain)의 3가지 전극을 이용하여 전류의 흐름을 조절하는 트랜지스터이다. 활성층으로 사용되는 물질의 Type에 따라 양(+) 또는 음(-)의 전압을 게이트 전극에 가했을 때, 절연층에 발생하는 전계를 이용하여 반도체층에 형성되는 채널(Channel)을 통해 이동하는 전자나 정공의 양을 제어하는 원리이다.

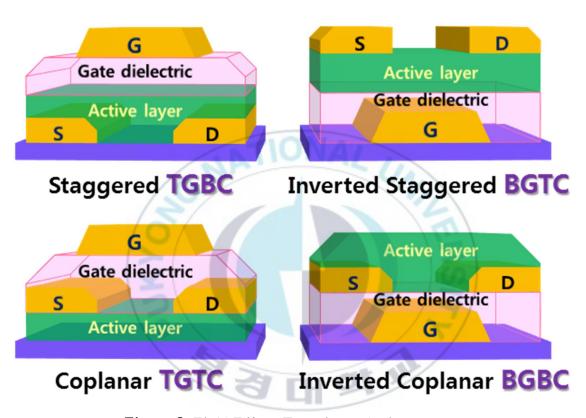

#### 가. 전계 효과 트랜지스터의 구조

전계 효과 트랜지스터의 경우 크게 Top-Gate / Bottom-Contact, Top-Gate / Top-Contact, Bottom-Gate / Top-Contact, Bottom-Gate / Bottom-Contact의 총 4가지의 구조로 구분이 가능하며 각각의 구조에 따라 장단점이 존재하므로 제작하고자 하는 트랜지스터와 물질에 따라 적절한 구조를 선택하여 사용하는 것이 중요하다. 본 논문에서는 Bottom-Gate / Top-Contact의 구조로 소자를 제작하여 실험을 진행하였다. BGTC 구조의 경우 반도체 표면에 형성된 굴곡을 따라 전극의 형성이 가능하기 때문에 활성층과 전극 사이에 존재하는 계면이 넓어져 컨택 저항 (Contact resistance)을 낮출 수 있다는 장점이 있다.

Figure 2. Field Effect Transistor device structure

#### 나. 전계 효과 트랜지스터의 전기적 특성

전계 효과 트랜지스터의 경우 일반적으로 전달 곡선(Transfer Curve)과 출력 곡선(Output Curve) 2가지 그래프를 통해 전기적 특성을 파악할 수 있다. 전달 곡선은  $V_D$ 를 고정시키고  $V_G$ 에 따른  $I_D$ 의 변화를 측정할 수 있으며 게이트 전압에 따른 채널의 전하 형성 정도를 확인할 수 있다. 출력 곡선의 경우 전류가 선형적으로 증가하는 선형 영역(Linear region)과 포화되어 일정한 전류를 유지하는 포화 영역(Saturation region)으로 나눌수 있다. 각 영역에서의 소스 전극과 드레인 전극 간에 흐르는 전류  $I_D$ 는 게이트 전압  $V_G$ 와 소스/드레인 전압  $V_D$ 를 사용하여 다음과 같은 식으로 나타낼 수 있으며, 전하의 이동도(Mobility), 문턱 전압(Threshold Voltage), 문턱 기울기(Subthreshold Voltage), 점멸비(On/Off Ratio)와 같은 전계 효과 트랜지스터의 전기적 특성을 파악할 수 있는 여러 파라미터를 구할 수 있다.

$$I_{D,lin} = \frac{W\mu_{lin}C_i}{L}\Big(V_G - V_T - \frac{V_D}{2}\Big)V_D$$

(linear region)

$$I_{D,sat} = \frac{W\mu_{sat}C_i}{2L}(V_G - V_T)^2$$

(saturation region)

(W= 채널의 폭, L= 채널의 길이,  $\mu=$  전하 이동도,  $V_T=$  문턱 전압,  $C_i=$  게이트의 정전용량)

## III. 실험 및 분석

### 1. 실험 재료

#### 가. Indium Oxide / Gallium Oxide

전하가 이동하기 위한 반도체 박막을 형성시키기 위한 물질로 산화물인 Indium Oxide 와 Gallium Oxide를 혼합하여 사용하였다. Indium Gallium Oxide(IGO)는 3가지 물질이 혼합된 삼성분계 N-Type 산화물 반도체로 전기전도성이 좋고 광 투과도가 우수해 박막 트랜지스터의 재료로 유용하게 사용될 수 있다. Indium의 경우 앞서 언급된 것처럼 s오비탈의 궤도 겹침을 이용하여 전자 이동도를 증가시키는 효과가 있다. 또한 이렇게 증가된 전자 이동도를 과잉 캐리어의 생성을 억제시키는 Gallium의 특성을 이용하여 전원을 Off시키고 누설전류를 방지할 수 있다. 또한 산소 원자에의해 형성되는 공공을 통해 전기 전도를 위한 전자 캐리어를 형성시킬 수있다.

#### 나. Hafnium Oxide / Zirconium Oxide

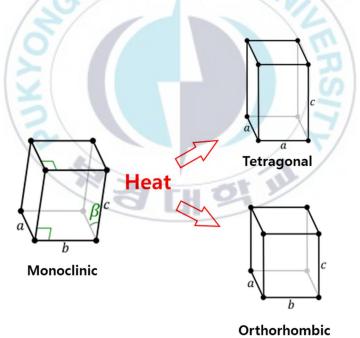

절연층 박막을 형성을 위한 강유전체 물질로는 Hafnium Oxide와 Zirconium Oxide를 각각의 비율로 혼합하여 사용하였다. Hafnium은 상온에서 단사 구조(monoclinic phase)를 선호하고 대칭성을 가지며 상유전성을 띈다. 반면 Zirconium은 정방 구조(tetragonal phase)를 가지며 대칭

성이 좋고, 반강유전성을 띄게 된다. Zirconium은 Hafnium과 물성이 비슷한 4가 원자로, 큰 밴드 갭 에너지(5.8eV)를 가지고 있어 Hafnium의 가장 이상적인 Dopant로 알려져 있으며, Zirconium을 도핑할 경우  $400\sim500$   $^{\circ}$ 의 낮은 결정화 온도에 의해 혼합물은 저온에서 열처리를 통해 사방구조(Orthorhombic) 상으로의 결정 구조 변화가 생기면서 Ferroelectric 특성을 얻을 수 있다. Hafnium과 Zirconium을 혼합한 HZO의 화학적 조성비는  $Hf_{1-x}$   $Zr_xO_2$ 로 나타낼 수 있으며, 50:50의 조성비에서 가장 큰 Ferroelectric 특성을 가지는 것으로 알려져 있다.

Figure 3. Changes in the crystal structure of ferroelectric materials

Figure 4. Dielectric constants of hafnium oxide and zirconium oxide materials

#### 2. 실험 방법

#### 가. 기판 제작

본 실험에서는 Bottom-Gate Top Contact(BGTC) 구조를 선택하여 기판을 제작하였다. 약 525um 두께의 N-Type Polished Silicon Wafer를 사용하였으며 실리콘 기판은 산화물 반도체를 코팅하기 전 탈이온수 (Di Wafer), 아세톤 (Acetone), 이소프로필알콜 (Isopropylalchol, IPA)을 이용하여 각각 10분씩 Sonic Bath에서 초음파 세척을 진행하였다. 이후 RIE 장비를 이용하여 10초간 O<sub>2</sub> 플라즈마 처리를 통해 기판을 세척하였다.

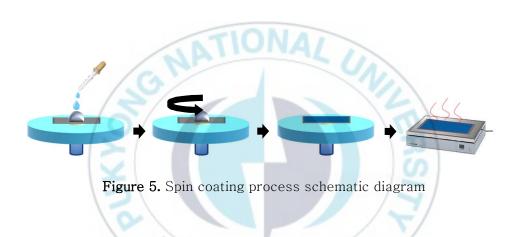

#### 나. 산화물 반도체와 강유전성 절연체의 박막형성

본 실험에서는 스핀 코팅(Spin Coating) 방법을 이용하여 활성층과 절연 층 박막을 형성시켰다. 스핀 코팅 방식은 기판 위에 용액을 도포 후 회전시켜 원심력을 이용하여 박막을 형성시키는 방법으로 고속으로 회전하면서용액의 Solvent가 대부분 증발되고, 산화물만 남아 막을 형성시키게 된다. 스핀 코팅 방식은 장비의 회전수(RPM)를 통해 박막의 두께를 조절할 수 있으며, 상대적으로 고가의 장비를 필요로 하지 않고 균일한 두께의 박막을 형성시킬 수 있다는 장점이 있다.

#### (1) 강유전성 절연층 박막 형성

저전압 구동 트랜지스터를 제작하기 위해 강유전체 물질인 Hafnium(IV) Chloride와 Zirconium(IV) Chloride를 0.2mol의 농도로 용액을 제조하여 절연층으로 사용하였다. 이 두 물질을 혼합한 Hafnium Zirconium Oxide(HZO)를 열처리를 통해 결정화가 되면 강유전성이 나타나는 사방 구조(Orthorhombic)를 가지게 된다. Solvent로는 Ethyl Alcohol와 Nitric Acid를 사용하였으며, 각 물질은 0.2mol의 용액 농도로 용액을 제조하여 실험을 진행하였다. Si 기판 위에 각 비율로 혼합한 HZO 용액을 도포 후 5000rpm, 30s의 조건으로 절연층의 코팅을 진행하였으며, 이후 형성된 박막의 열처리를 위해 Box Furnace를 사용하여 어닐링(Annealing)을 진행하였다.

#### (2) N-Type 산화물 반도체 박막 형성

활성층의 역할을 하기 위해 Indium(III) nitrate hydrate(In(NO<sub>3</sub>)<sub>3</sub>·xH<sub>2</sub>O)와 Gallium(III) nitrate hydrate(In(NO<sub>3</sub>)<sub>3</sub>·xH<sub>2</sub>O)를 80 : 20의 비율로 혼합하여 게이트 절연층 박막 위에 코팅하였다. 2-Methoxy Ethanol을 Solvent로 사용하여 각각 0.05mol의 농도로 용액을 제조하였으며, 절연층 코팅과 마찬가지로 스핀 코팅 장비를 사용하여 5000rpm, 30s의 조건으로 반도체층 코팅을 진행하였다. 형성된 박막의 열처리를 위해 핫 플레이트 (Hot Plate)를 사용하여 275℃의 온도에서 박막의 어닐링(Annealing)을

진행하였다. 산화물 반도체 박막 형성의 공정은 습도에 영향을 받는 산화물 반도체의 특성상 제습 기능이 있는 글러브 박스 내부에서 코팅을 진행하였다.

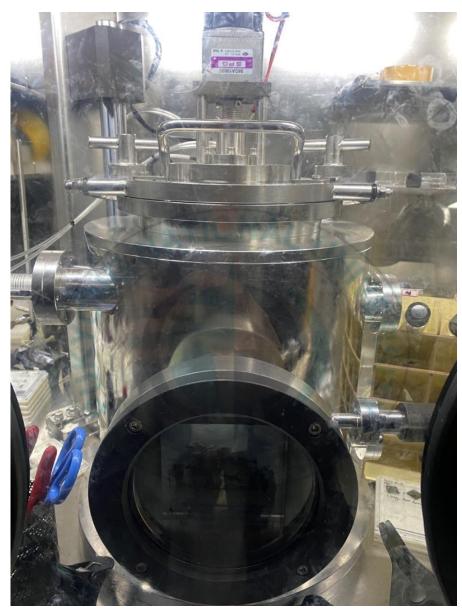

Figure 6. Oxide—only glove box in our LAB

Figure 7. Spin coater in our LAB

Figure 8. Hot Plate in our LAB

Figure 9. Box Furnace for annealing

#### 다. 전극 증착

절연층과 반도체층을 코팅한 이후 전류가 흐르는 Source와 Drain 전극을 중착하기 위해 물리적 기상 중착법(Physical Vapor Deposition, PVD)을 사용하였다. PVD 방식은 진공 상태의 챔버 내부에서 금속을 기화시켜 원하는 웨이퍼 표면에 중착시키는 방법이다. 실험실 내에 위치한 Solar—Thermal Evaporator를 사용하였으며, 이 장비의 경우 다양한 PVD 방법중 상대적으로 단순한 방법인 열 중착법을 이용한 전극 중착 방법이다. 중착 공정 진행 시 장비의 챔버 내부를 진공 상태로 유지시키므로 디바이스의 오염을 방지할 수 있다는 장점이 있다. 진공 상태에서 고온의 열을 가해 중착을 위한 Source를 녹이고, Mask를 씌운 소자에 Gate나 Contact을 중착시키는 방법을 사용한다. 본 실험에서는 소자에 Contact Mask를 씌운 진공도  $10^{-6}$ Torr 이상의 고진공에서 전극의 중착을 진행하였으며, Aluminium Source를 사용하여 Thickness Monitor를 확인해가며 50nm의 Contact 전극을 중착하였다.

Figure 10. Thermal Evaporation in our LAB

## 3. 측정 방법 및 측정 장비

### 가. 반도체 전기적 특성 분석 장비

제작한 Fe-FET는 Keithley 4200A-SCS(Semiconductor Characterization System) 반도체 분석 장비를 사용하여 전기적 특성을 분석하였다. 반도체 박막과 절연층 특성상 N-Type 특성이 강하게 나타나므로 양전압(+) 위주의 저전압을 가해가며 소자의 전기적 특성을 측정하였다.

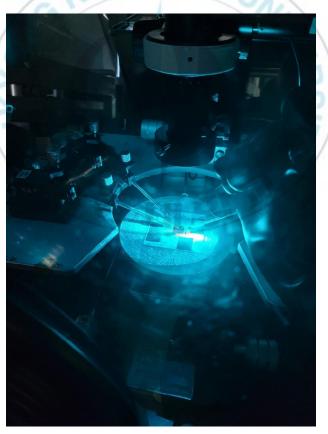

Figure 11. Vacuum probe station in our LAB

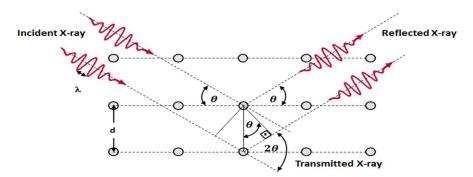

#### 나. X-Ray Diffractometer (XRD)

절연층 박막의 온도에 따른 결정화도를 파악하기 위해 X-Ray Diffractometer를 사용하였다. XRD 장비는 X-Ray를 원하는 시편에 회절시켜 시편의 내부 정보를 그래프로 나타내는 분석 장비로 여러상들의 고유한 각도에서 Peak 값이 나타나 결정이 시편속에 어떠한 상으로 존재하고있는지 분석 가능한 방법이다. 시편으로 입사되는 X선의 각도를 연속적으로 변화시키면서 회절되어 나오는 X선의 강도를 기록하면 강도가 다른 복수의 회절 peak가 나타나고, 이로부터 각도와 강도에 대한 그래프를 얻을수 있다. 결정구조는 각 물질에 따라 차이가 있으므로 회절 패턴 또한 물질의 고유한 값을 가지게 된다. XRD 분석법은 Bragg's Law라고 불리는회절식으로 나타날 수 있고 아래의 식으로 표현이 된다.

Bragg's Law:  $n\lambda = 2dsin\theta$

회절현상이 발생하는 경우 입사 X선의 파장λ 및 입사각 θ와 격자면 간격 d 사이에 Bragg's Law가 성립하게 된다. 파장 λ와 X선의 입사각 θ가 결정되면 회절 패턴을 통해 결정격자의 면간거리 d를 계산할 수 있게 된다.

Figure 12. Measurement Principles of XRD

Figure 13. X-Ray Diffractometer measuring equipment

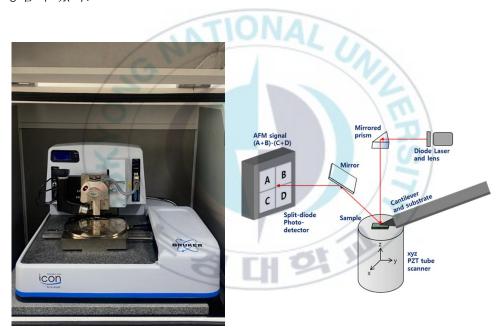

#### 다. Atomic Force Microscope (AFM)

AFM 은 캔틸레버(Cantilever)라고 불리는 탐침이 시료의 표면에 가까워지고, 이때 시료 표면과 탐침 사이에 작용하는 인력이나 척력을 감지기(Detector)에서 감지하여 시료 표면의 형상을 이미지화 할 수 있는 측정 장비이다. AFM 은 나노 단위의 아주 미세한 분석이 가능하다는 장점이 있다.

**Figure 14.** Atomic Force Microscope & Principles of operation of a commercial AFM employing a bottom-side PZT scanner

## III. 결과 및 고찰

### 1. 습도에 따른 반도체 박막의 전기적 특성 평가

강유전체 게이트 절연층의 특성을 파악하기 앞서 전자가 이동하기 위한 채 널이 형성될 수 있는 산화물 활성층을 코팅하기 위해 Si/SiO2 기판위에 Indium Gallium Oxide(IGO)를 코팅하여 트랜지스터로서의 전기적 특성을 파악하였다. 소스 전극을 접지시키고 드레인 전극과 게이트 전극에 전압을 가해주어 Source와 Drain 사이에 흐르는 전류의 양을 측정하였다.

Figure 12, Figure 13은 공정 진행 시 습도에 따른 전달곡선과 출력곡선과 Indium Gallium Oxide(IGO)의 혼합 비율에 따른 전기적 특성을 나타낸 그래프이다. 습도에 많은 영향을 받는 산화물 반도체이기에 각각 다른 습도에서 코팅된 박막의 전기적 성질이 어떻게 변하는지 확인해보았다. 박막의 코팅시 습도는 20%로 고정시켰으며 이후 열처리 과정에서 각각 30%와 40%, 50%로 설정 후 실험을 진행하였다. 전기적 특성 측정 결과 열처리 과정에서의 습도가 증가갈수록 이동도가 소폭 증가하였으나 Gate 전압에 의한 Drain 전류가 제어되지 않고 반도체적 특성이 아닌 도체의 성질을 띠고 있는 것을 확인할 수 있었다. 이는 습도가 증가함에 따라 Indium Gallium Oxide 박막에 수소 원자가 도핑되어 일어나는 현상으로 생각된다. 작고 가벼운 수소 원자의 특성상 Indium과 Gallium의 격자 내부로 침입이

쉬울 뿐 아니라 산화물 박막의 산소 공공 위치로 수소 원자가 침투하게 되고, 이후 전하를 제공하는 도펀트로서의 역할을 수행할 수 있게 된다. 따라서 대기중 습도의 중가로 인해 전자의 이동이 과도하게 증가하는 현상을 보이게 된다.

반도체 활성층 혼합 비율의 경우 Indium의 양이 증가할수록 Mobility나 On Off Ratio 등의 전체적인 전기적 특성이 증가하였다. 하지만 Indium의 양이 90% 이상이 될수록 표준 편차가 커지는 것으로 보아 전자의 이동이 과도하게 증가하는 것으로 판단된다. 따라서 이후의 실험에서는 Indium Gallium Oxide의 양을 80 : 20로 고정시켰으며 습도는 20%의 조건에서 실험을 진행하였다.

반도체층의 전기적 특성 측정 결과 20%에서 50%까지 10% 단위로 습도가 증가할수록 전자 이동도가 감소하는 것을 확인하였다. 산화물 반도체의 특성상 수소 원자의 도핑이 증가할수록 Conductive한 도체의 특성이 보이게 되지만 시간이 지날수록 수소 원자가 증발하여 공공이 형성되게 되고 결함으로 작용하게 된다. 이로 인해 습도가 증가할수록 이동도가 감소하는 추세를 보이게 되었다.

Figure 15. A schematic diagram of the hydrogen doping effect

**Figure 16.** Transfer curve and Output curve according to humidity.

(a) 20%, (b) 30%

Figure 17. Transfer curve and Output curve according to humidity. (c) 40%, (d) 50%

#### 2. 게이트 절연층 코팅 온도에 따른 X선 특성 평가

온도에 따른 물질의 상 변화를 파악하기 위해 교내 공동실습관에 있는 X-Ray Diffractometer를 사용하여 Hafnium Zirconium Oxide의 결정 구 조를 측정해 보았다. Hafnium Oxide와 Zirconium Oxide의 경우 열역학적 안정상인 Monoclinic Phase, 고온 안정상인 Tetragonal Phase, 강유전성 결정상인 Orthorhombic Phase가 존재한다. Tetragonal phase와 Monoclinic Phase는 Non-Centrosymetric하여 물질이 강유전성 특성을 띄는 것에 기여하지 않으며, Orthorhombic Phase만이 강유전체의 특성을 띄게 된다. 기본적으로 Hafnium Zirconium Oxide는 400° C에서 500° C 의 사이의 온도에서 전극과 박막 사이에 걸린 응력(stress)에 의한 구조 변화가 생기면서 강유전성이 나타나며 50%의 조성비에서 강한 강유전성 의 특성을 띄는 것으로 알려져 있다. 따라서 Hafnium과 Zirconium의 적 절한 비율과 열처리 온도의 조절을 통해 강유전체의 특성이 나타나는 Orthorhombic Phase의 결정상이 형성될 수 있도록 유도하는 것이 중요하 다.

XRD를 통해 50%의 Zr 조성비로 400° C에서 700° C까지 100° C 단위로 열처리를 진행한 소자의 결정구조를 측정하였다. 측정 결과 33.1°의 각도에서 강한 peak가 발생하는 것이 확인되었으며, 이는 고온에서 상 안정상인 Tetragonal phase가 형성된 것으로 판단된다. 이 Peak의 경우 열

처리 온도가 증가할수록 세기가 강해졌으며 고온으로 갈수록 결정상이 더욱 안정적으로 바뀌는 것으로 판단된다. 또한 28.5°와 31.5°에서 peak 가 나타났으며, 이는 각각 Monoclinic Phase가 Orthorhombic Phase가 형성된 것으로 보인다. Orthorhombic Phase가 형성되었으나 Tetragonal Phase가 강하게 나타났으며, 상대적으로 많은 분율을 차지하는 Tetragonal Phase로 인해 Ferroelectric 특성이 나타나지 않은 것으로 생각된다. 따라서 Tetragonal Phase와 Monoclinic Phase의 형성을 억제시켜 Orthorhombic Phase의 비율을 증가시킬 수 있는 방법을 찾는 과정이필요할 것으로 판단된다.

#### 3. 절연층 혼합 비율에 따른 박막의 모폴로지 변화

게이트 절연층의 비율에 따른 특성을 파악하기 위해 우선 Atomic Force Microscopy (AFM)를 사용하여 Hafnium과 Zirconium의 비율에 따른 절연층 박막의 모폴로지를 분석하였다. 측정을 위한 디바이스의 경우 Hafnium과 Zirconium의 비율을 각각 100:0,80:20,50:50,20:80,0:100으로 설정하였으며 Box Furnace를 사용하여 500°의 온도에서 열처리를 진행하였다. Figure 19은 스캔 사이즈를 54m로 설정한 후 측정한고분자 박막의 AFM 이미지이다. AFM 이미지를 통해 박막의 표면을 분석해봤을 때, Hafnium Oxide에 도핑된 Zirconium Oxide의 비율이 증가할수록 표면 거칠기를 의미하는 RMS(Root Mean Square)값이 증가하는 경향성을 확인할 수 있었으며, 이는 성장시킨 Hafnium Zirconium 박막에 구조적인 변화가 발생한 것으로 추론할 수 있다. 거칠어진 박막의 표면은 절연층과 활성층 사이의 계면에 트랩을 발생시키고 전자의 이동을 방해하여 FET의 전기적 특성에 부정적인 영향을 미칠 수 있다. 따라서 Zirconium Oxide의 비율이 증가할수록 전기적 특성은 감소할 것으로 예상된다.

Figure 19. AFM image according to Hafnium Zirconium Oxide ratio.

(a) 100 : 0, (b) 80 : 20, (c) 50 : 50, (d) 20 : 80, (e) 0 : 100

#### 4. 절연층 혼합 비율에 따른 소자의 전기적 특성 비교

Active Layer로 Indium Gallium Oxide를 8:2의 비율로 고정시키고 20%의 습도에서 실험을 진행하였다. 또한 Dielectric Layer는 Ferroelectric 특성을 가진 물질인 Hafnium Oxide와 Zirconium Oxide를 혼합하여 각각의 비율에 따른 강유전체 특성과 전기적 특성을 비교해보았다. Active Layer의 측정 방식과 마찬가지로 소스와 드레인 전국 사이에 흐르는 전류를 게이트 전압으로 조절하였으며 저전압에서 구동 가능한 디바이스를 확인하기 위해 전달 곡선의 경우 게이트 전압을  $-4V \sim +2V$ 의 범위에서 0.01V의 간격으로 전압을 인가하였고, 출력 곡선의 경우 트레인 전압을  $0V \sim +2$ 의 범위에서 0.05V의 간격으로 전압을 인가하여 전류의 양을 측정하였다.

Figure 20, Figure 21, Figure 22은 Dielectric Layer 물질의 혼합 비율에 따른 전달곡선과 출력곡선을 나타낸 그림이다. 실험의 결과는 여러 파라미터들로 나타내었으며, Table 2에 정리하였다. 소자의 전기적 특성 측정 결과 SiO2를 절연층으로 사용해 소자를 제작했을 때와 비교하여 1~2cm²/Vs 사이의 범위에서 이동도의 큰 차이는 나타나지 않았으며 누설전류 또한 게이트 절연층 박막이 두께가 얇아 졌음에도 불구하고 기존의 SiO2 기반 게이트 절연층과 크게 차이가 나지 않았으며 Hafnium Oxide와 Zirconium Oxide의 혼합비 20: 80에서 가장 우수한 성능을 나타나는 것

을 확인할 수 있었다. 강유전성 메모리의 특성은 나타나지 않았지만 기존에 널리 사용되는  $SiO_2$  절연층을  $HfO_2$ 나  $ZrO_2$ 와 같은 강유전성 물질로 대체하여 강유전 물질 기반 저전압 구동 Fe-FET를 제작 가능하다는 것으로 해석할 수 있다.

Figure 20. Characteristic graph according to HZO ratio.

(a) 100: 0, (b) 80: 20

(c) 50:50, (d) 20:80

Figure 22. Characteristic graph according to HZO ratio. (e) 0:100

| Humidity | Mobility[Cm2/Vs],Sat | Threshold Voltage[V] | On/Off Ratio          | Subthreshold Slope,SS[V/dec] |

|----------|----------------------|----------------------|-----------------------|------------------------------|

| 20%      | 1.532 (±0.08)        | 20.39                | 2.5 × 10 <sup>6</sup> | 2381.47                      |

| 30%      | 1.178 (±0.12)        | 7.43                 | 3.0 x 10 <sup>5</sup> | 2716.0                       |

| 40%      | 0.951 (±0.21)        | -8.31                | 9.4 × 10 <sup>6</sup> | 3023.09                      |

| 50%      | 1.391 (±0.42)        | -81.54               | 7.5 × 10 <sup>4</sup> | 2498.78                      |

Table 1. Summary of semiconductor layer's electrical properties according to humidity

| Ratio | Mobility[Cm2/Vs],Sat | Threshold Voltage[V] | On/Off Ratio          | Subthreshold Slope,SS[V/dec] |

|-------|----------------------|----------------------|-----------------------|------------------------------|

| 10:0  | 1.182 (±0.072)       | 0.23                 | 6.3 x 10 <sup>5</sup> | 564.97                       |

| 8:2   | 1.136 (±0.084)       | 0.54                 | 7.4 x 10⁵             | 552.49                       |

| 5:5   | 1.169 (±0.13)        | 0.48                 | 6.0 x 10 <sup>5</sup> | 568.18                       |

| 2:8   | 2.014 (±0.09)        | 0.37                 | 5.3 x 10 <sup>5</sup> | 432.90                       |

| 0:10  | 1.139 (±0.11)        | 0.55                 | 4.3 x 10 <sup>5</sup> | 565.22                       |

**Table 2.** Summary of gate dielectric layer's electrical properties according to ratio

### V. 요 약

본 논문에서는 기존에 사용되는 절연층의 한계점을 해결하기 위해 산화물기반 강유전체 물질을 게이트 절연층으로 대체하여 저전압 구동 강유전체기반 FET를 제작하는 실험을 진행하였다. 게이트 절연층 물질로는 n-Type 특성을 갖는 Hafnium Oxide와 Zirconium Oxide를 100:0,80:20,50:50,20:80,0:100의 비율로 혼합하여 사용하였으며 혼합 비율에 따른 전기적 특성을 분석하여 두 물질의 혼합 비율이 게이트 절연층의 역할에 영향을 미치는지 비교하였다.

우선 트랜지스터의 전기적 특성 분석에 앞서 X-Ray Diffractometer (XRD) 와 Atomic Force Microscope (AFM)를 사용하여 열처리 온도 및 혼합 비율에 따른 특성을 비교해보았다. XRD를 통한 물질의 결정학적 특성을 분석했을 때, 33.1도에서 가장 강한 Peak이 나타났으며 이는 m-Phase가형성되어 고온에서 상 안정이 이루어 졌다고 해석할 수 있다. 강유전체 물질의 특성을 발현시켜 메모리의 기능을 하기 위해서는 고온에서 o-phase가 안정한 상이 되어야 할 것으로 생각된다. 또한 AFM 이미지를 통해 혼합 비율에 따른 박막의 표면을 분석해봤을 때, Hafnium Oxide에 도핑된 Zirconium Oxide의 비율에 따른 박막 모폴로지의 변화는 결정학적 관점에서 보았을 때 크게 나타나지 않았으며, Hafnium Oxide에 도핑된 Zirconium Oxide의 비율이 증가할수록 표면 거칠기가 증가하는 것을 확인할 수 있었다. 박막의 표면 거칠기가 증가하는 것을 확인

계면에서 이동하는 전자의 속도에 영향을 미쳐 전자의 이동도가 감소하는 경향을 보이는 것으로 판단되었다.

소자의 전기적 특성을 파악하기 위해 Si 기판 위에 스핀코팅 방식을 이용하여 각각의 비율로 혼합된 강유전체 물질을 코팅 하였고, 활성층 물질로는 산화물 기반 n-Type 물질인 Indium Oxide와 Gallium Oxide를 스핀코팅 하였다. 이후 열 증착기를 이용하여 50nm 두께의 알루미늄(Al) 전국 패턴을 형성하여 BGTC 구조의 Fe-FET 디바이스를 제작하였다. 제작한 Fe-FET의 전기적 특성을 평가한 결과, 도핑된 Zirconium Oxide의 비율에 따른 이동도의 차이는 크게 나타나지 않았으며, 기존의 SiO2 절연층의 디바이스와 비교해봤을 때에도 소자를 평가하는 주요한 파라미터의 측면에서는 차이가 나타나지 않았다. 이는 기존에 널리 사용되는 SiO2 절연층의 tunneling effect에 의한 leakage current나 두께 측면에서의 한계점을 극복하기 위해 HfO2나 ZrO2와 같은 강유전성 물질로 대체가 가능하다는 것을 보여준다.

# 참고문헌

- [1] Eunjin Bae<sup>1</sup>, Jin Young Lee<sup>1</sup>, Seung-Yeol Han<sup>2</sup>, Chih-Hung Chang<sup>2</sup> and Si Ok Ryu<sup>1</sup>, Korean Chem. Eng. Res., Vol. 49, No. 5, October, 2011, pp. 600-604.

- [2] Anastasia Chouprik<sup>1</sup>, Sergey Zakharchenko<sup>1</sup>, Maxim Spiridonov Sergei Zarubin, Anna Chernikova, Roman Kirtaev, Pratyush Buragohain, Alexei Gruverman, Andrei Zenkevich, and Dmitrii Negrov, ACS Appl. Mater. Interfaces 2018, 10, 8818–8826.

- [3] Geun Taek Yu<sup>1</sup>, Geun Hyeong Park<sup>1</sup>, Eun Been Lee<sup>1</sup>, Min Hyuk Park<sup>1,2</sup>, Sae Mulli, Vol. 71, No. 11, November 2021, pp. 890~900.

- [4] Xiao-Ying Zhang<sup>1</sup>, Chia-Hsun Hsu<sup>1</sup>, Shui-Yang Lien<sup>1,2</sup>, Wan-Yu Wu<sup>2</sup>, Sin-Liang Ou<sup>3</sup>, Song-Yan Chen<sup>4</sup>, Wei Huang<sup>4</sup>, Wen-Zhang Zhu<sup>1</sup>, Fei-Bing Xiong<sup>1</sup> and Sam Zhang<sup>5</sup>, Nanoscale Research Letters (2019) 14:83 https://doi.org/10.1186/s11671-019-2915-0.

- [5] Ignasi<sup>1</sup> Fina and Florencio Sánchez<sup>1</sup>, ACS Appl. Electron. Mater. 2021, 3, 1530–1549.

- [6] Hien Thu Pham<sup>1</sup>, Jin Ho Yang<sup>2</sup>, Don-Sung Lee<sup>1</sup>, Byoung Hun Lee<sup>2</sup>, Hyun-Dam Jeong<sup>1</sup>, ACS Appl. Mater. Interfaces 2016, 8, 11, 7248-7256.

- [7] Ken Hoshino, Bao Yeh, John F. Wafer, Journal of the Society for Information Display Volume 21, Issue 7 p. 310-316.

- [8] Ao Liu<sup>1</sup>, Huihui Zhu<sup>2</sup>, Huabin Sun<sup>2</sup>, Yong Xu<sup>2</sup>, Yong-Young Noh<sup>1</sup>, Advanced Materials Volume 30, Issue 33 1706364.

- [9] 손기훈<sup>1</sup>, 강경문<sup>2</sup>, 박형호<sup>2</sup>, 이홍섭<sup>1,2</sup>, J. Microelectron. Packag. Soc., 27(1), 31-35 (2020)

- [10] Hengda Qiu<sup>1</sup>, Hejing Sun<sup>2</sup>, Libin Zheng<sup>2</sup>, Juncheng Xiao<sup>2</sup>, Hang Zhou<sup>1</sup>, SID International Symposium Digest of Technical Papers (Volume 51, Issue S1).

- [11] Hendrik Faber, Yen-Hung Lin, Stuart R. Thomas, Kui Zhao, Nikos Pliatsikas, Martyn A. McLachlan, Aram Amassian, Panos A. Patsalas, and Thomas D. Anthopoulos, *ACS Applied Materials & Interfaces* 2015, 7, 1, 782-790.

- [12] Hannes Dahlberg<sup>1</sup>, Anton E. O. Person, Robin Athle, and Lars-Erik Wernersson, ACS Appl. Electron. Mater. 2022, 4, 12, 6357-6363.

- [13] Ju Yong Park, Duk-Hyun Choe, Dong Hyun Lee, Geun Taek Yu, Kun Yang, Se Hyun Kim, Geun Hyeong Park, Seung-Geol Nam, Hyun Jae Lee, Sanghyun Jo, Bong Jin Kuh, Daewon Ha, Yongsung Kim, Jinseong Heo, Min Hyuk Park, Advanced Materials Accepted Articles 2204904.

- [14] Hyeon Woo Park, Jangho Roh, Yong Bin Lee, Cheol Seong Hwang, Advanced Materials Volume 31, Issue 32 1805266.

- [15] Simon Fabiano<sup>1</sup>, Xavier Crispin and Magnus Berggren, ACS Appl. Mater. Interfaces 2014, 6, 1, 438–442

- [16] Sukrob Abdulazhanov, Quang Huy Le, Dang Khou Hyunh, David Lehninger, Thomas Kanpfe and Gerald Gerlach, ACS Appl. Electron. Mater. 2022.

- [17] Morteza Hassanpour Amiri<sup>1</sup>, Jonas Heidker, Klaus Muilenm and Kanal Asadi, ACS Appl. Electron. Mater. 2020, 2, 1, 2–8

- [18] Martino Rimoldi<sup>1</sup>, Ashlee J. Howarth<sup>1</sup>, Matthew R. DeStefano<sup>1</sup>, Lu Lin<sup>1</sup>, Subhadip Goswami<sup>1</sup>, Peng Li<sup>1</sup>, Joseph T. Hupp<sup>1</sup>, and Omar K. Farha<sup>2</sup>